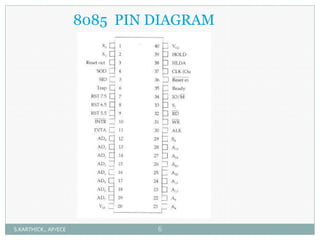

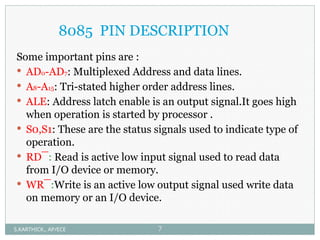

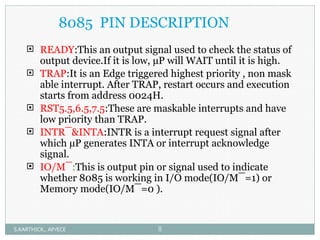

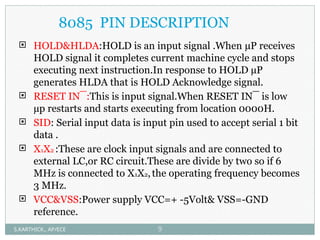

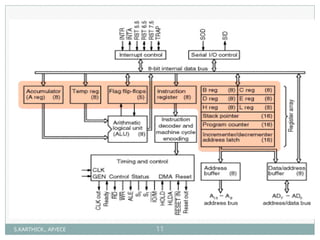

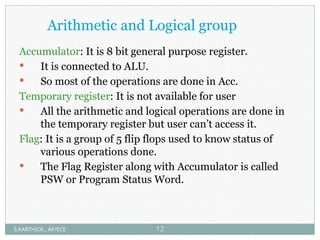

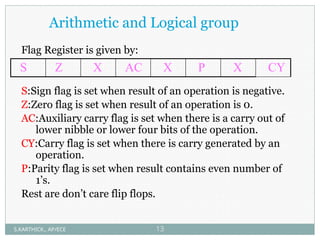

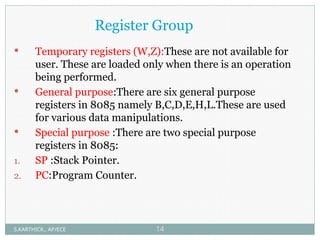

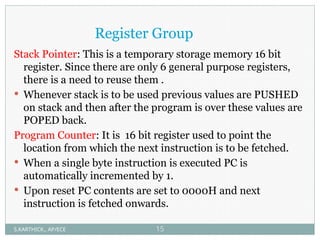

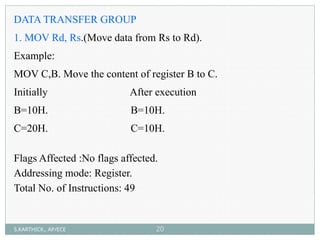

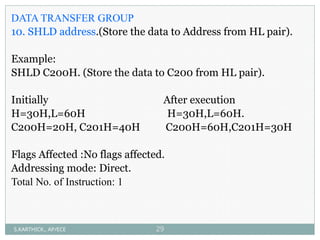

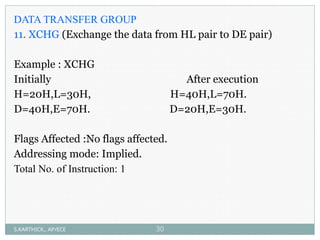

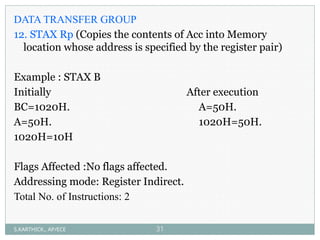

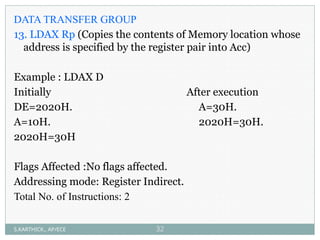

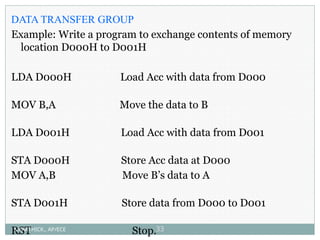

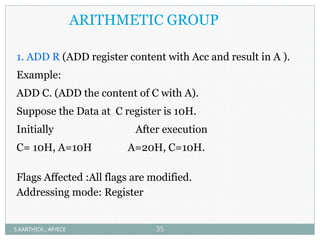

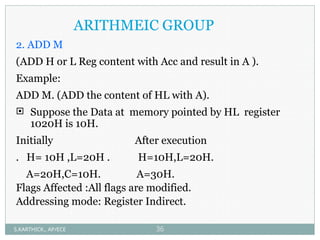

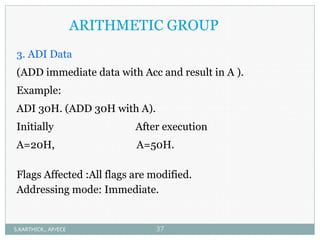

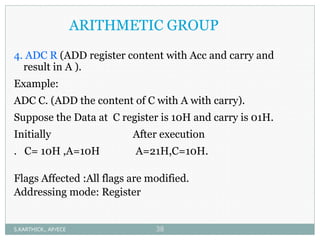

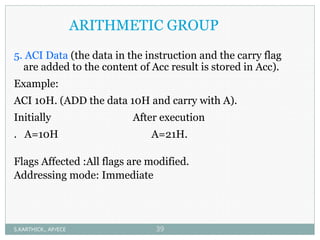

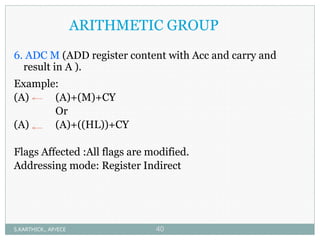

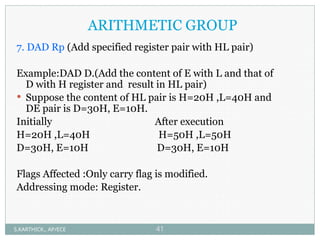

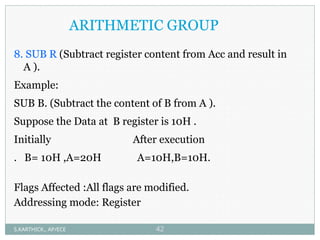

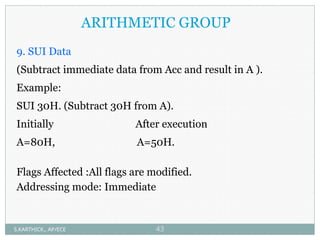

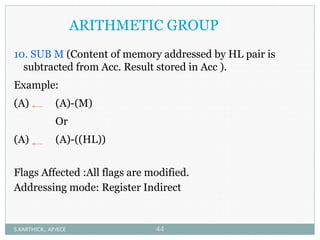

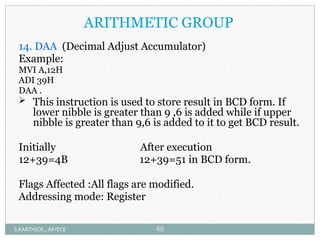

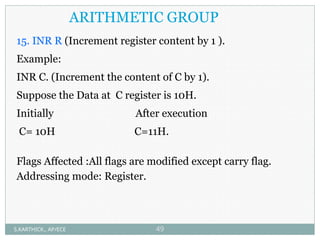

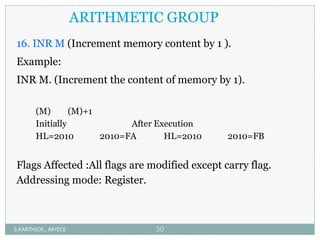

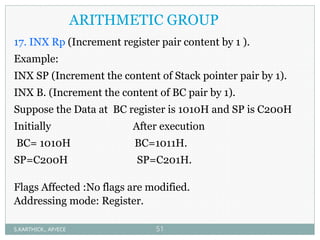

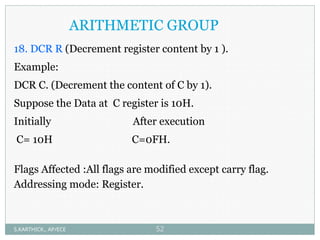

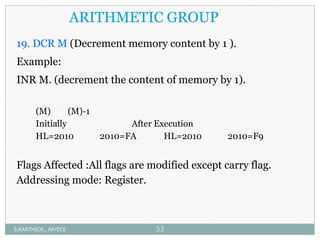

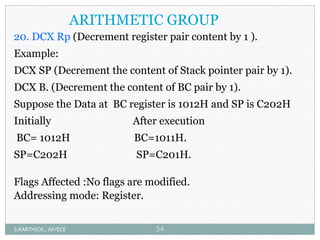

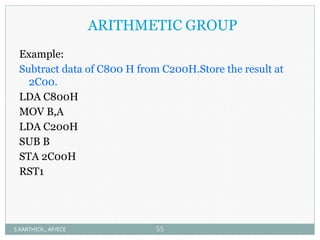

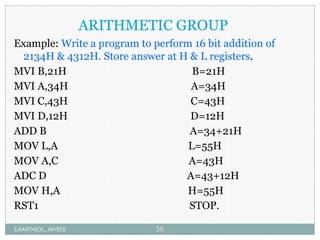

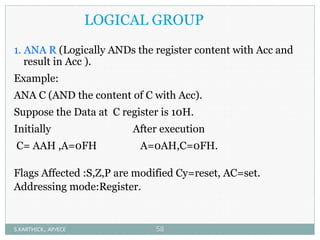

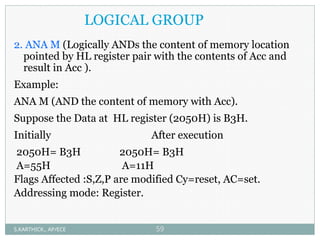

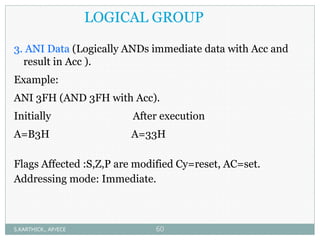

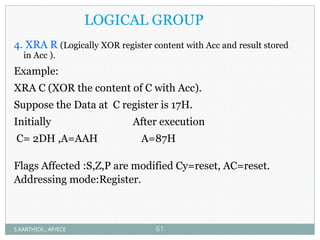

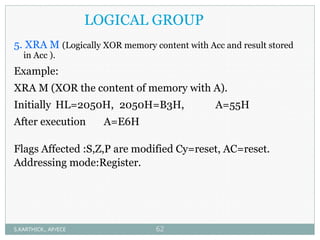

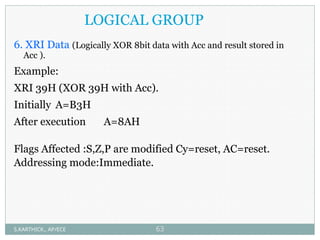

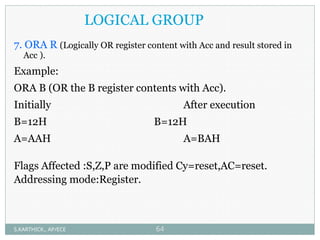

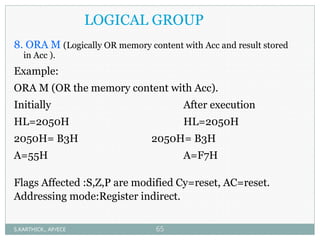

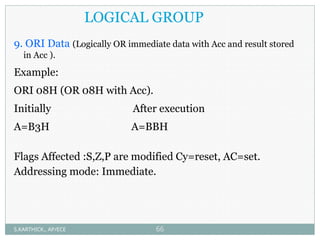

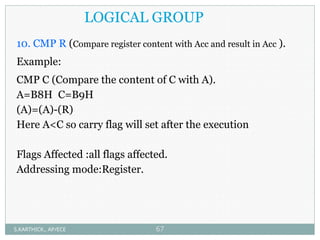

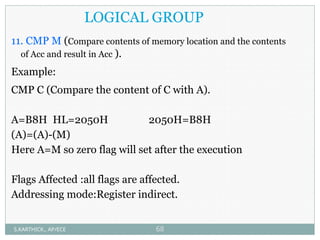

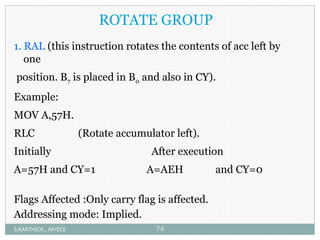

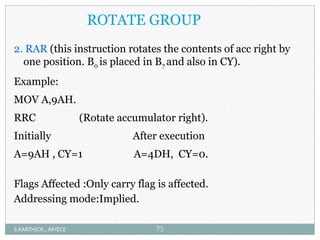

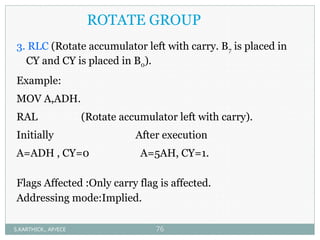

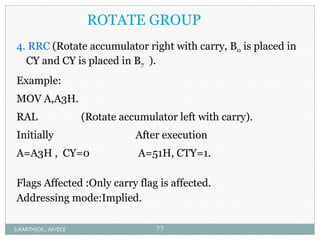

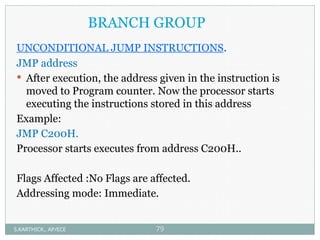

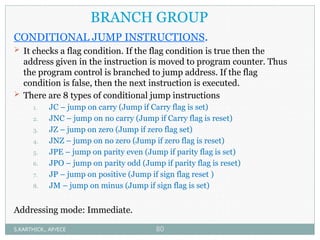

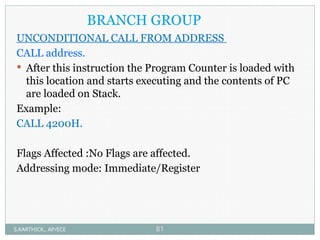

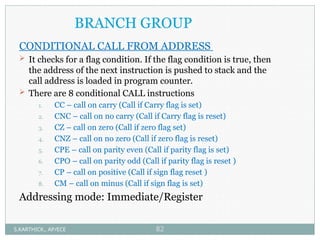

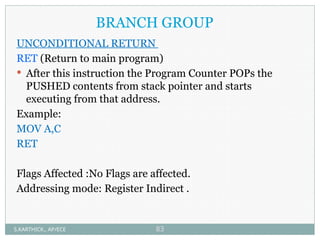

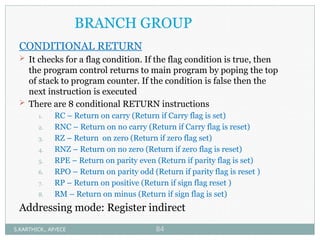

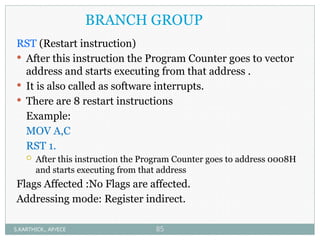

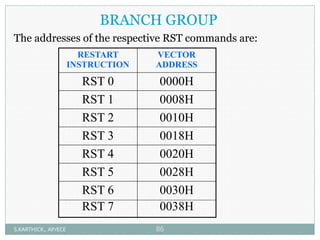

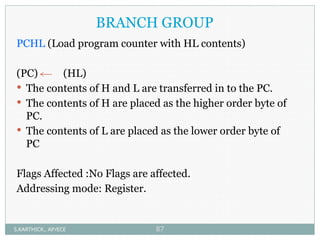

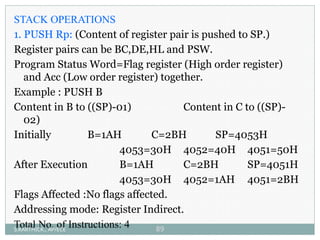

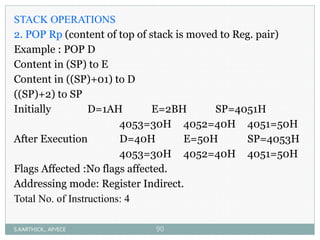

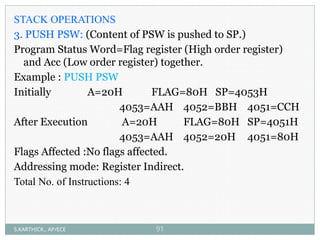

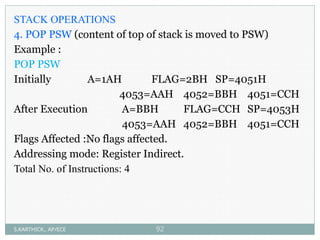

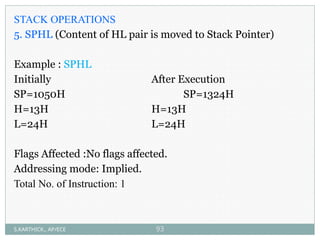

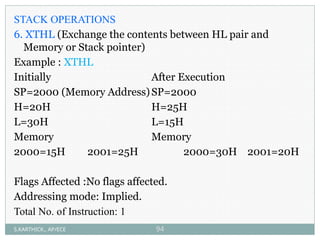

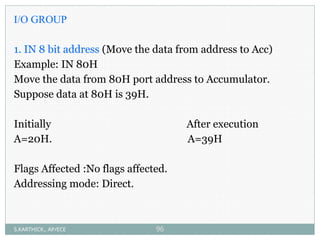

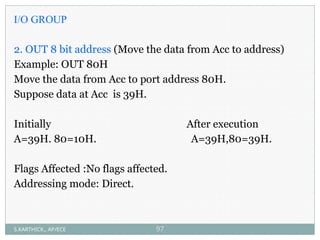

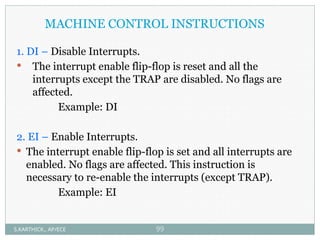

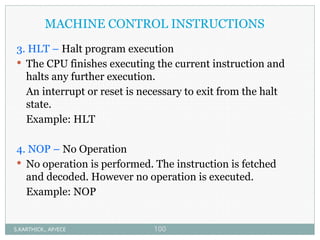

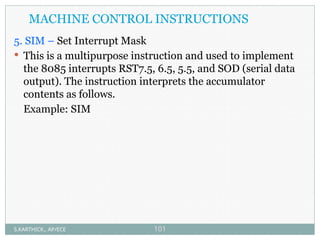

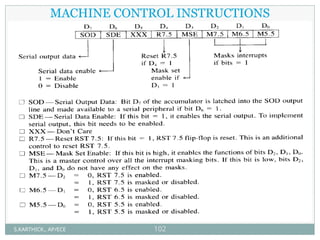

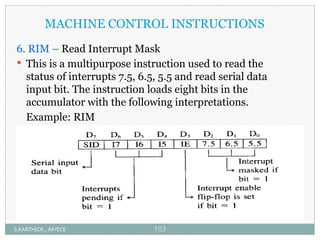

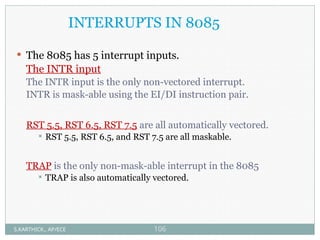

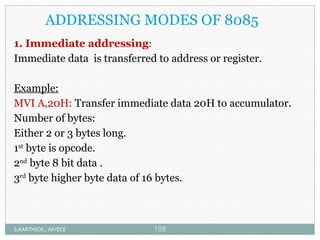

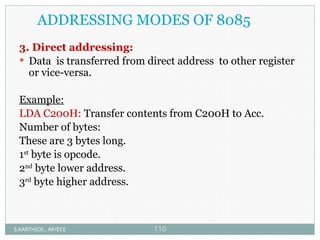

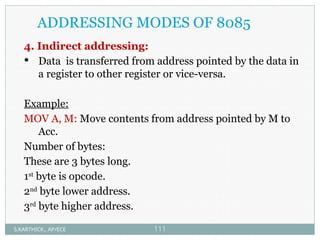

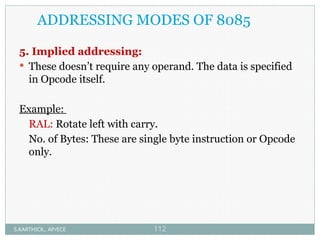

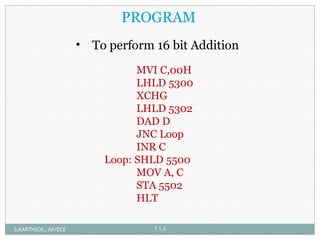

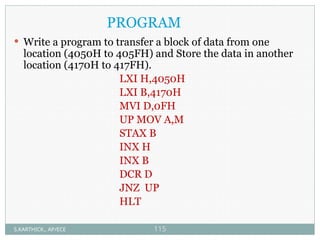

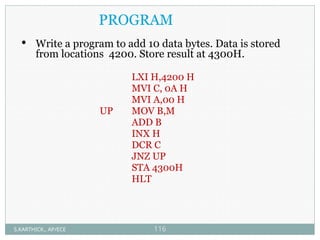

The document provides an overview of the Intel 8085 microprocessor, highlighting its features such as being an 8-bit processor with a 40-pin configuration, a maximum clock frequency of 3 MHz, and its ability to access 64K bytes of memory. It details various registers, instruction sets, and functionality including arithmetic, data transfer, and interrupt handling. The document also explains the significance of different pins and operating modes, alongside examples of instructions for better understanding.