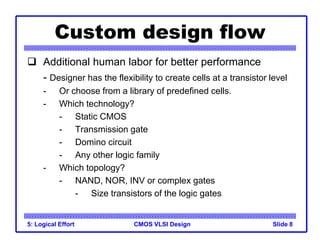

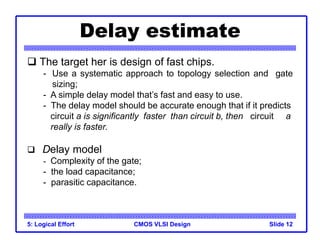

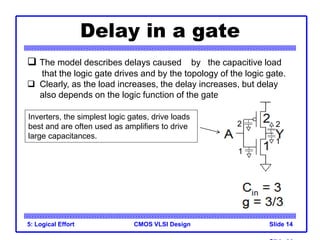

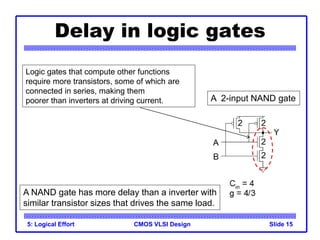

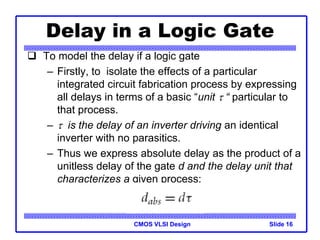

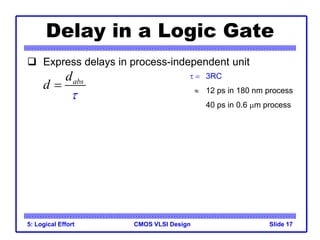

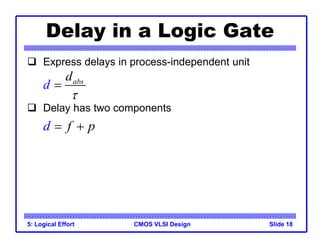

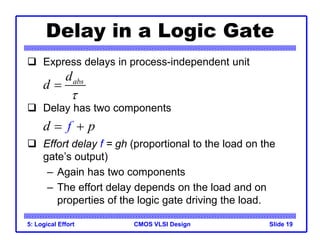

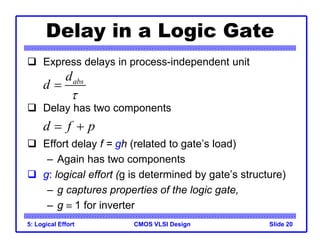

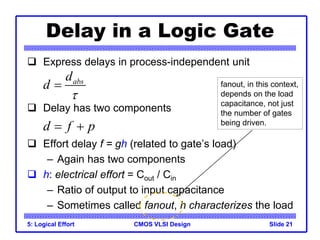

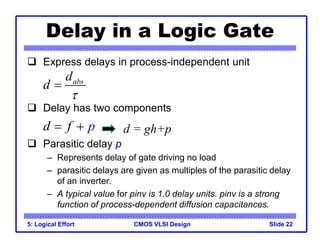

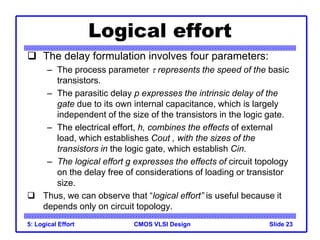

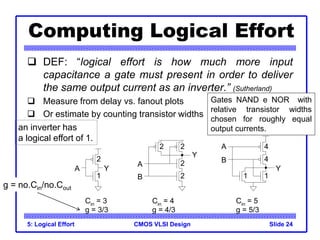

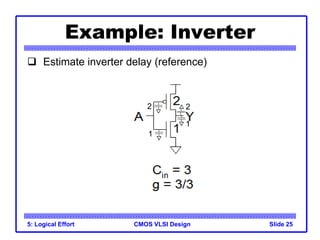

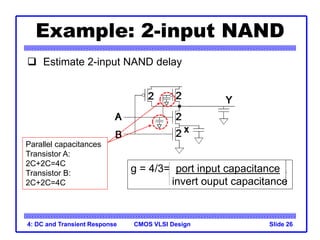

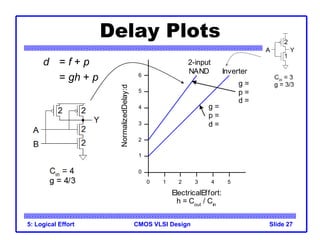

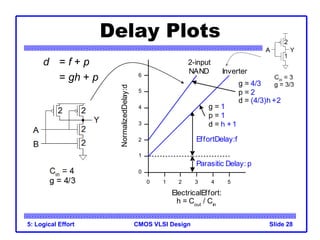

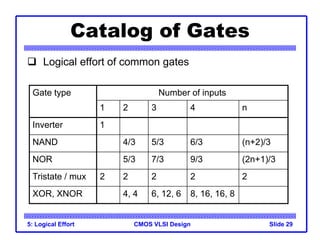

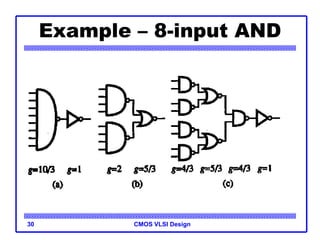

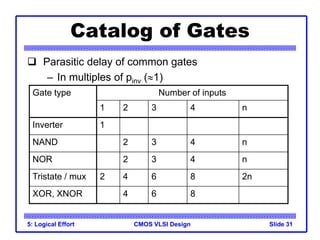

The document provides an introduction to the method of logical effort, which can be used to estimate delay in CMOS circuits. The method uses a simple delay model to allow rapid comparison of different logic structures and help select the fastest design. It defines the concept of logical effort to characterize the delay properties of different logic gates independent of load and transistor size. Logical effort, along with electrical effort and parasitic delay, is used to formulate a delay equation for logic gates. Examples are provided to demonstrate calculating logical effort values for common gates.