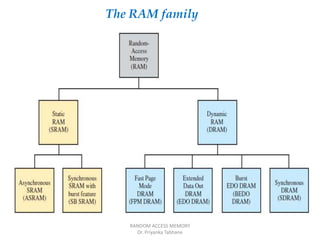

RAM is a type of memory that allows data to be read and written randomly at any location. There are two main types: SRAM uses latches and retains data indefinitely as long as power is applied, while DRAM uses capacitors and must be periodically refreshed to retain data. Both lose data when power is removed. DRAM is more common in computers due to higher density and lower cost, though SRAM is faster.