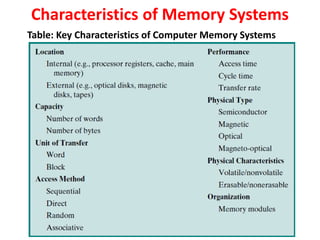

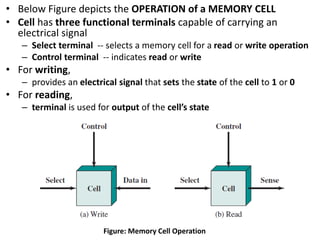

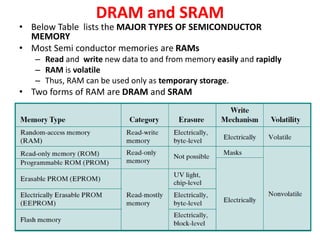

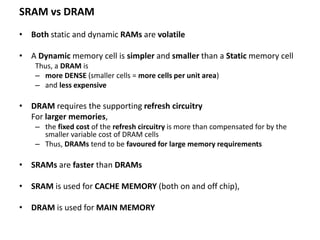

The document discusses different types of computer memory systems including cache memory, primary/main memory, and secondary memory. It describes key characteristics of memory like access time and cost per bit that change as one moves down the memory hierarchy. The document also discusses the operation of memory cells and different types of semiconductor memory like DRAM and SRAM. It compares DRAM and SRAM, noting that DRAM is denser and less expensive than SRAM but requires refresh circuitry. The document concludes by providing examples of ROM design and a circuit that uses ROM to output the square of a 3-bit input number.