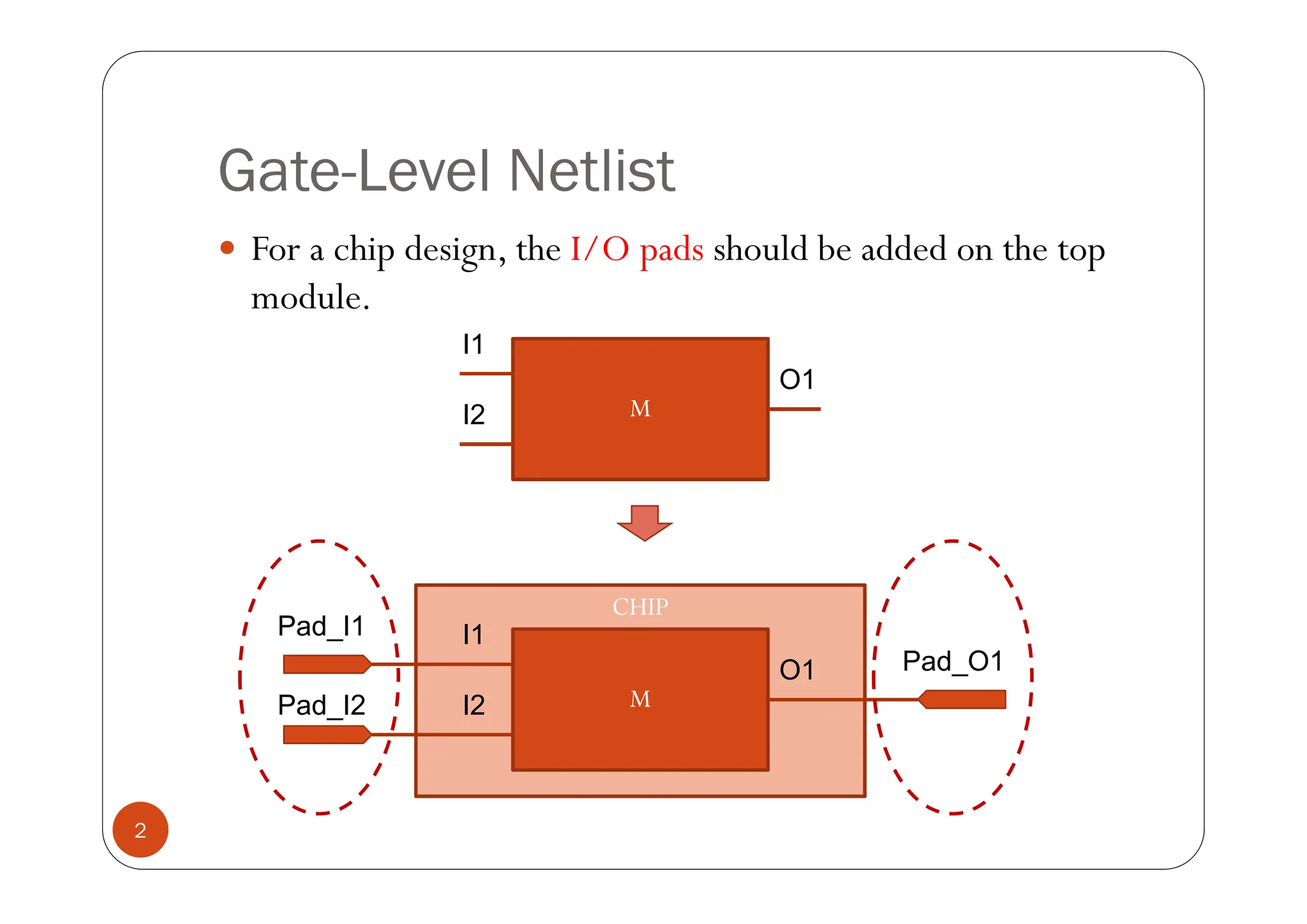

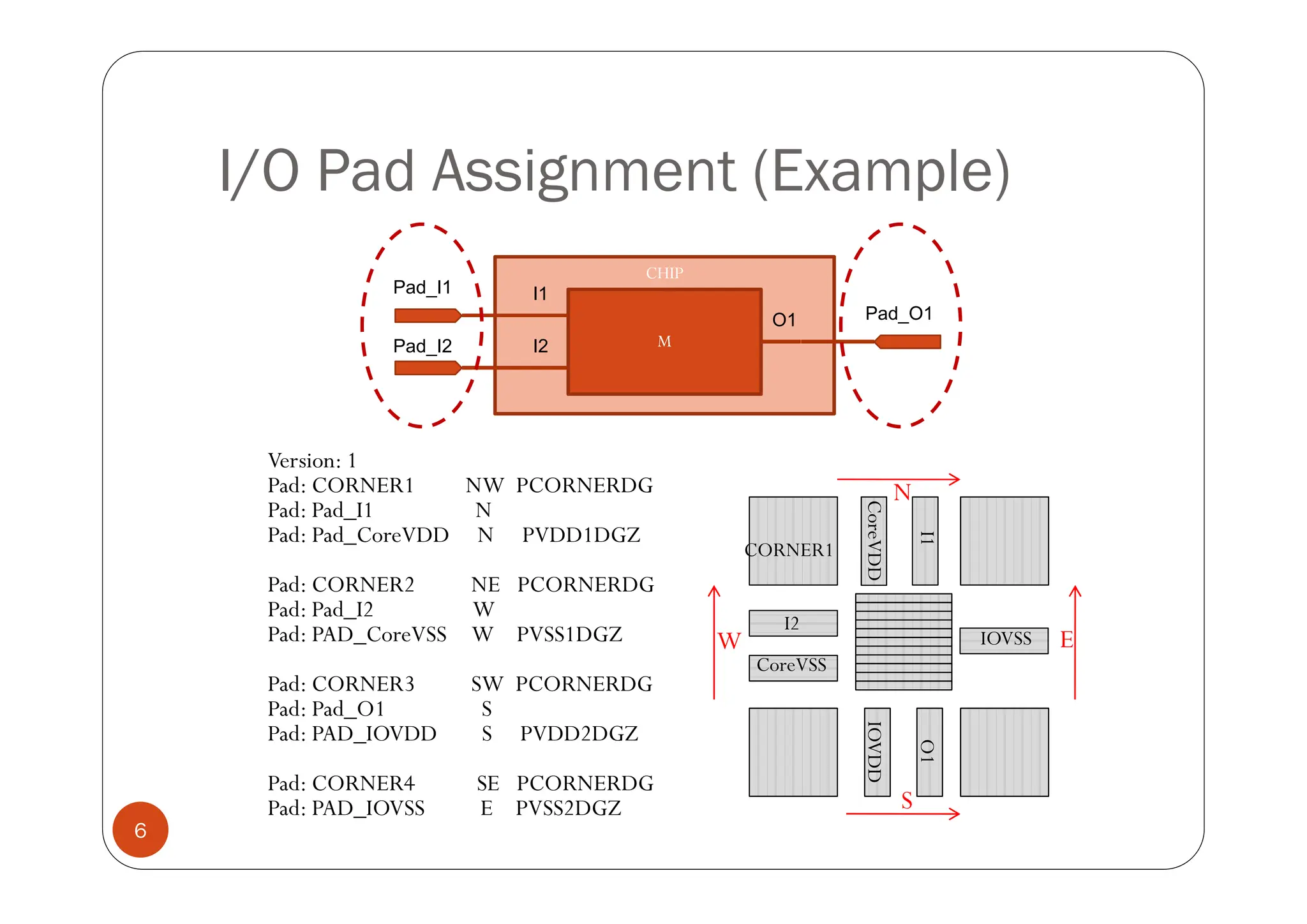

The document provides guidelines for I/O pad insertion in chip design using Cadence Innovus, emphasizing the importance of adding I/O pads to the top module for accurate simulation. It details various types of I/O pads available for the TSMC18 process, power pad assignments, and considerations for proper timing and layout before place and route (P&R) processes. Additionally, it notes that different rearrangements of pads can impact placement, routing, timing, and power consumption.