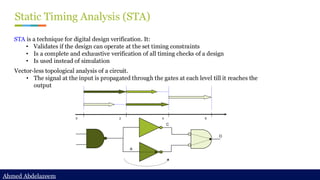

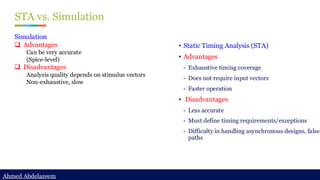

Static timing analysis (STA) is a method of validating the timing performance of a design by checking all possible paths for timing violations. STA breaks a design down into timing paths, calculates the signal propagation delay along each path, and checks for violations of timing constraints inside the design and at the input/output interface.

![Ahmed Abdelazeem

Ahmed Abdelazeem

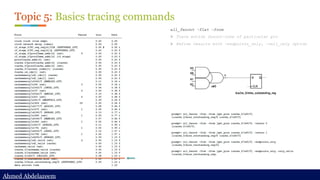

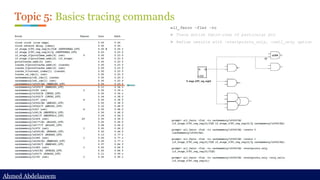

Topic 5: Basics tracing commands

all_connected [<pin/net object>]

➢ Usually we only care about leaf cell, so get leaf cell with

option –leaf

➢ Argument must be a valid database object, not a plain text

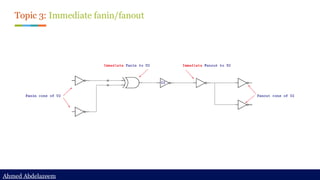

➢ Get immediate fanin/fanout](https://image.slidesharecdn.com/stabasicconcepts-250524204554-25ac4895/85/Back2School-STA-Basic-Concepts-Chapter-1-pdf-29-320.jpg)

![Ahmed Abdelazeem

Ahmed Abdelazeem

Topic 6: Synopsys object

query_object

➢ Return the object name rather than internal object

variable _sel*

get_object_name

➢ Translate design object to text sting in a list

Trick: split output into multiple lines

join [lsort -dict -unique [split [get_object_name $arg] "

" ]] "n“

Trick: [debug feature] proc_body

proc_body shows the content of a procedure. You can use it

to reveal unprotected procedure bodies for debug.](https://image.slidesharecdn.com/stabasicconcepts-250524204554-25ac4895/85/Back2School-STA-Basic-Concepts-Chapter-1-pdf-32-320.jpg)