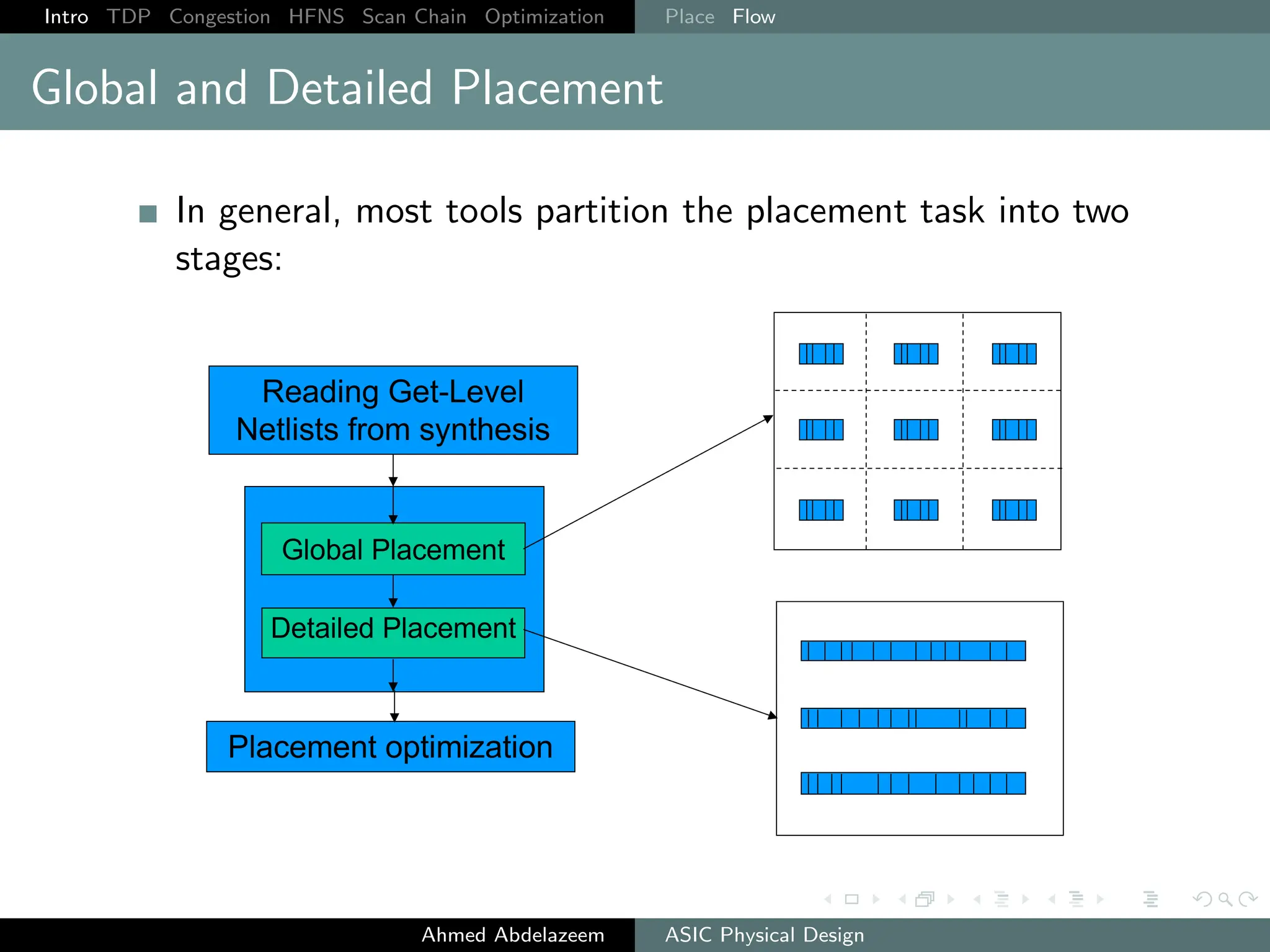

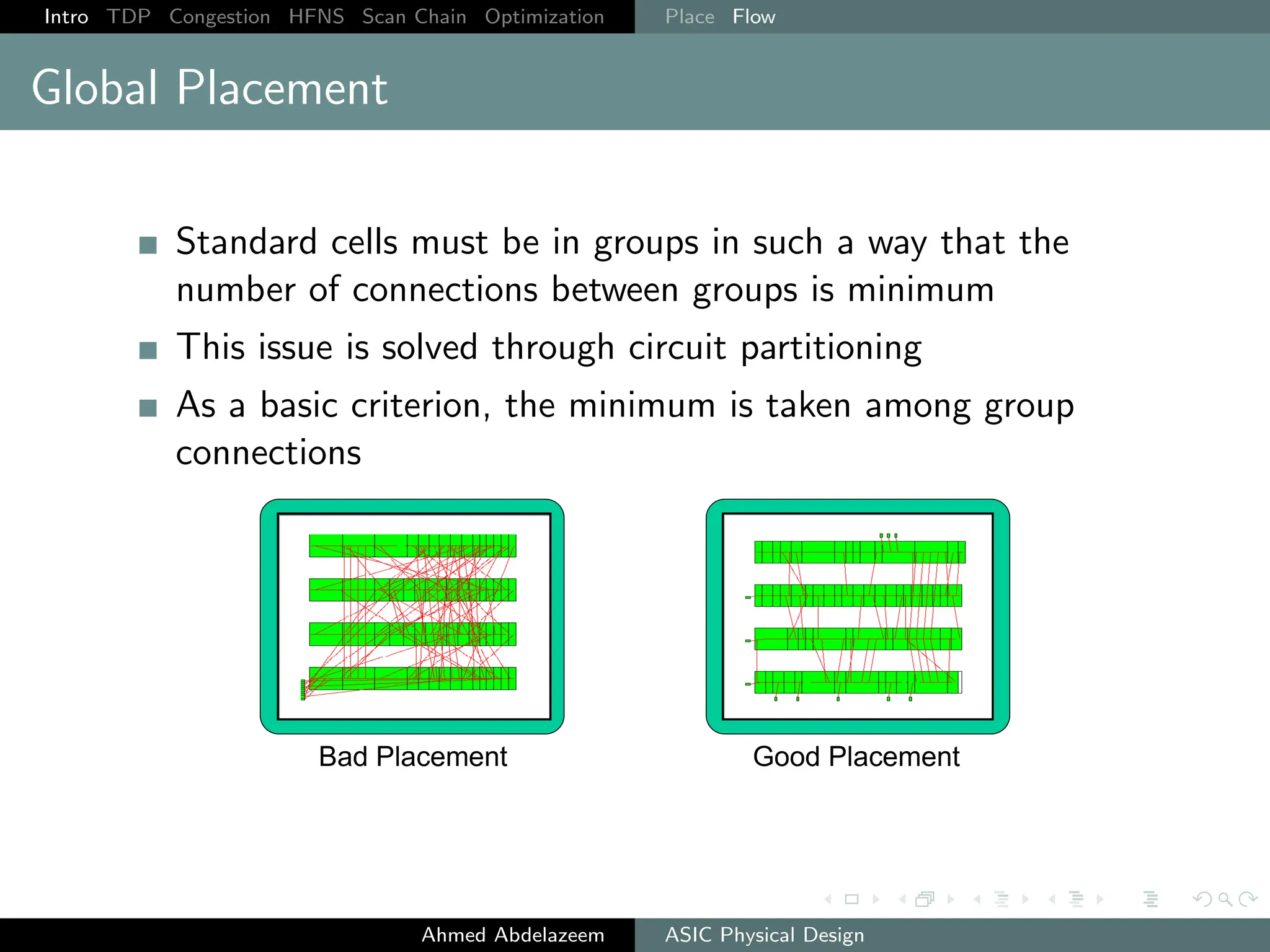

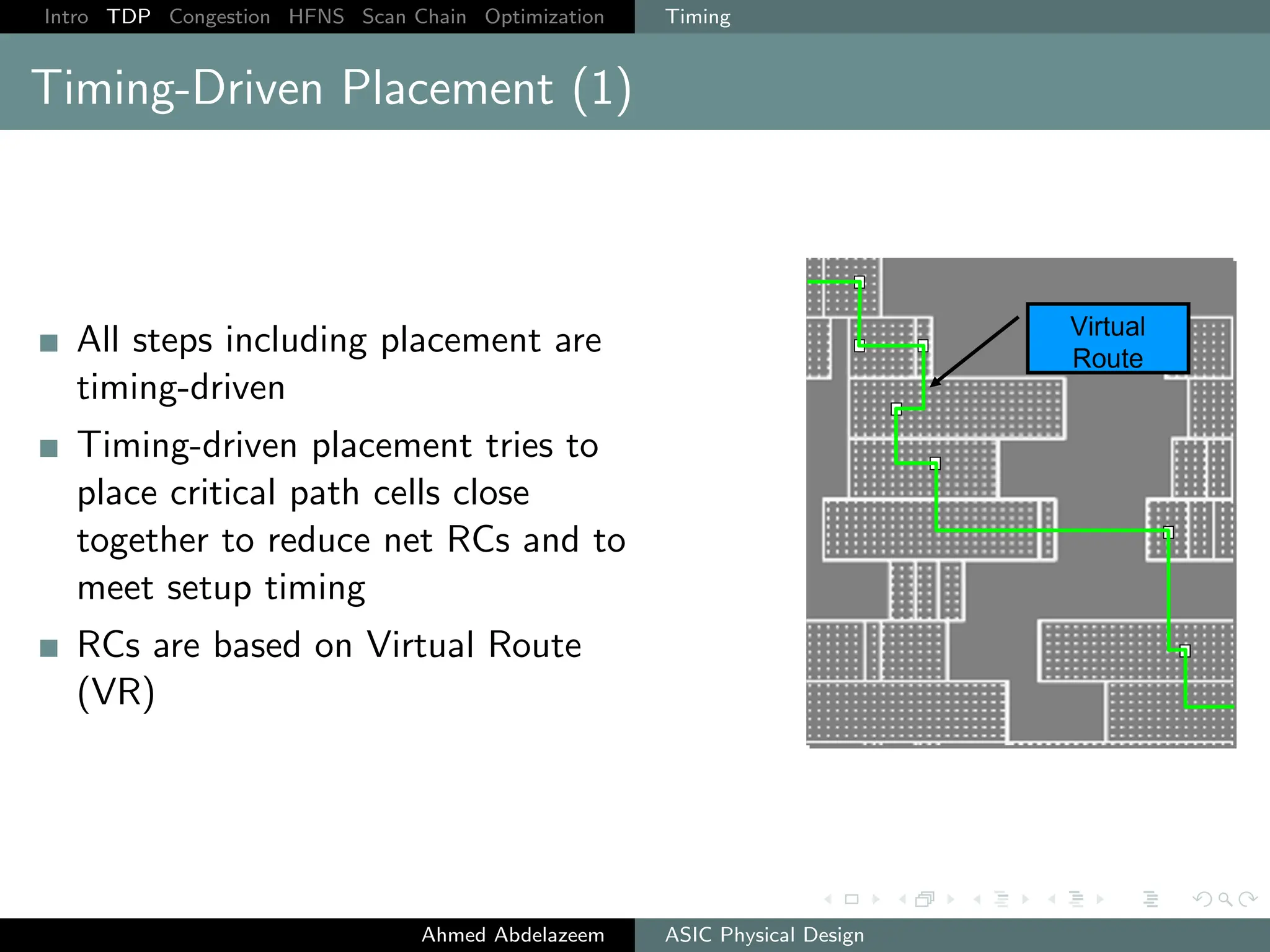

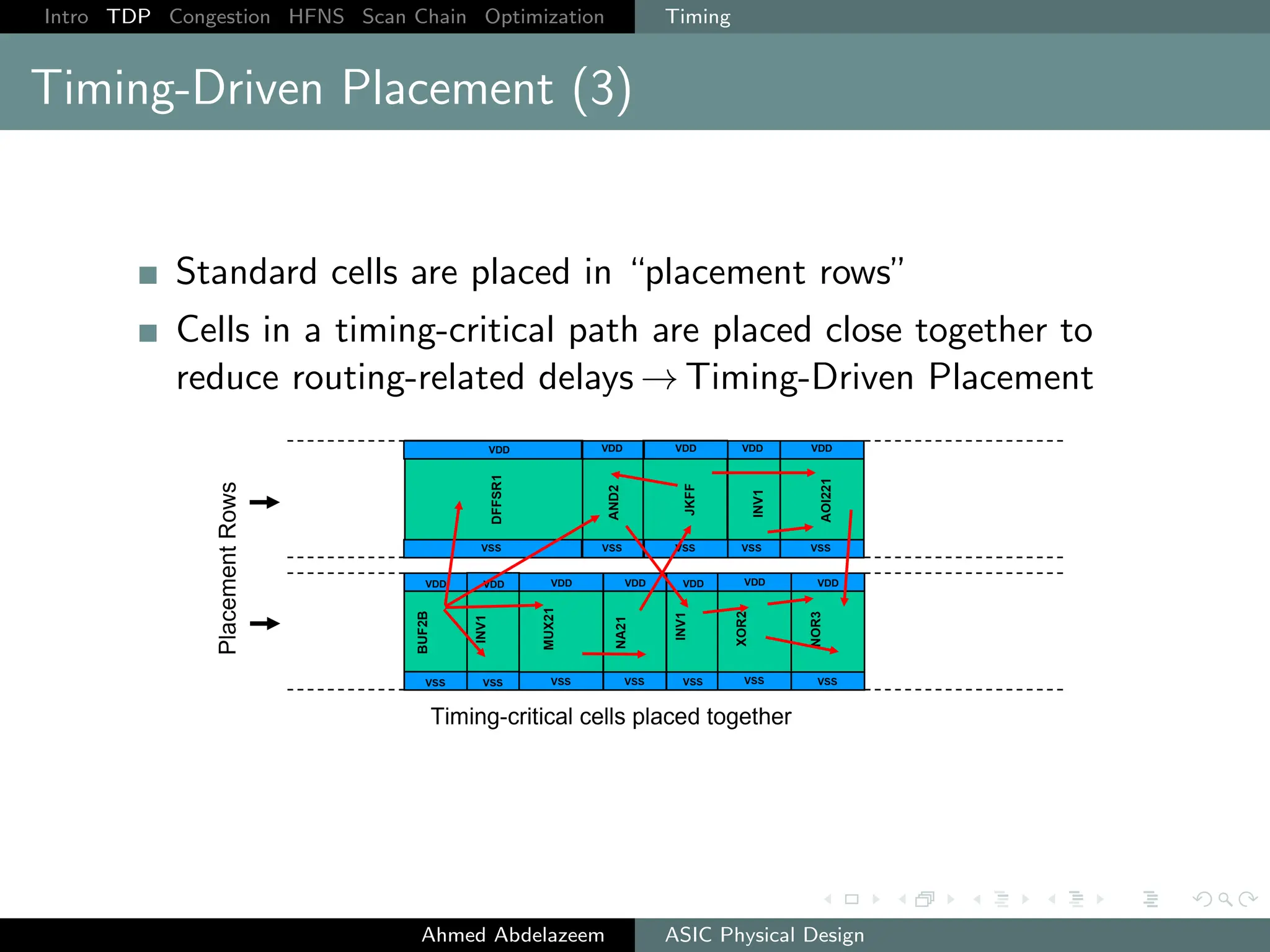

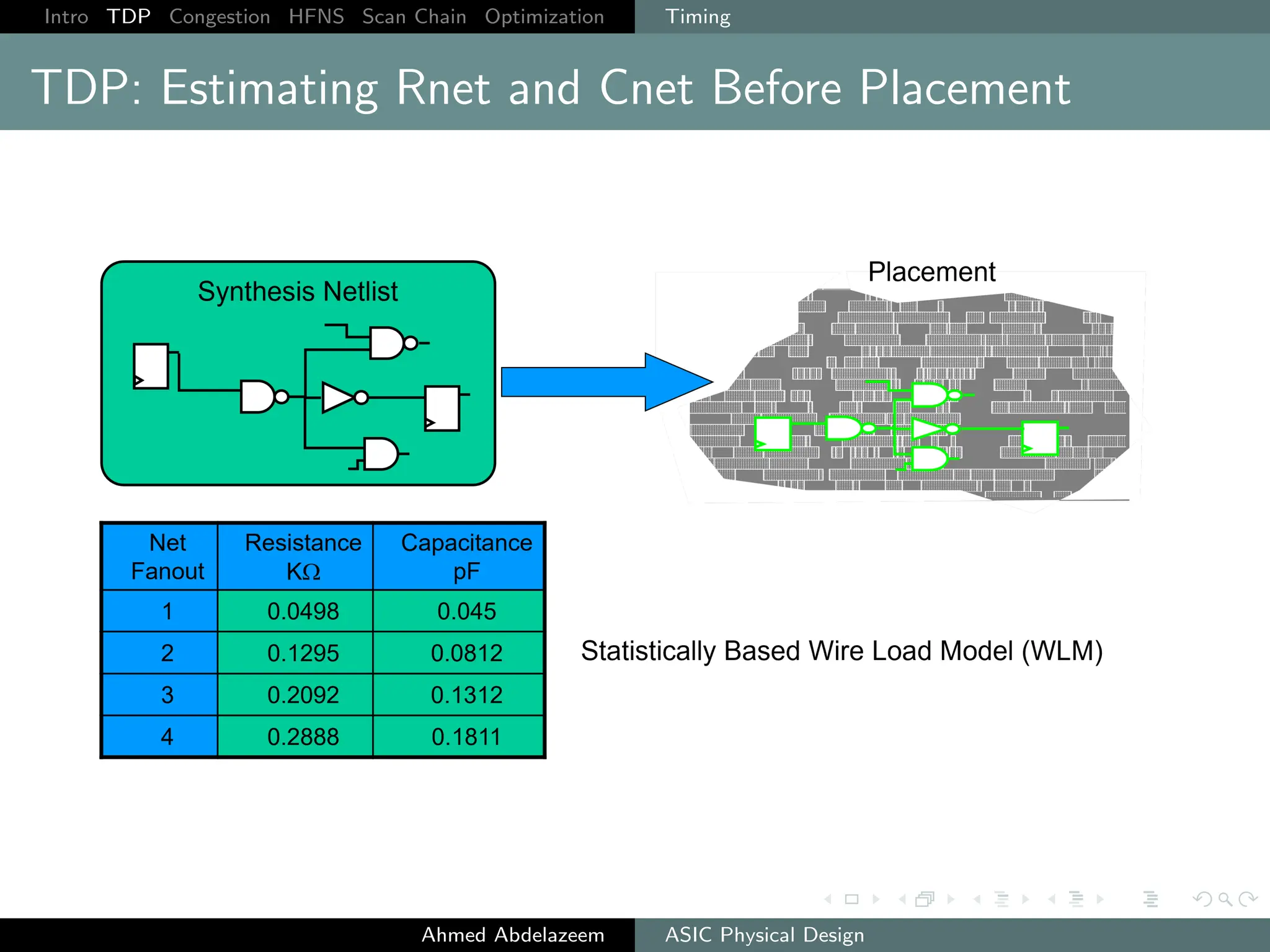

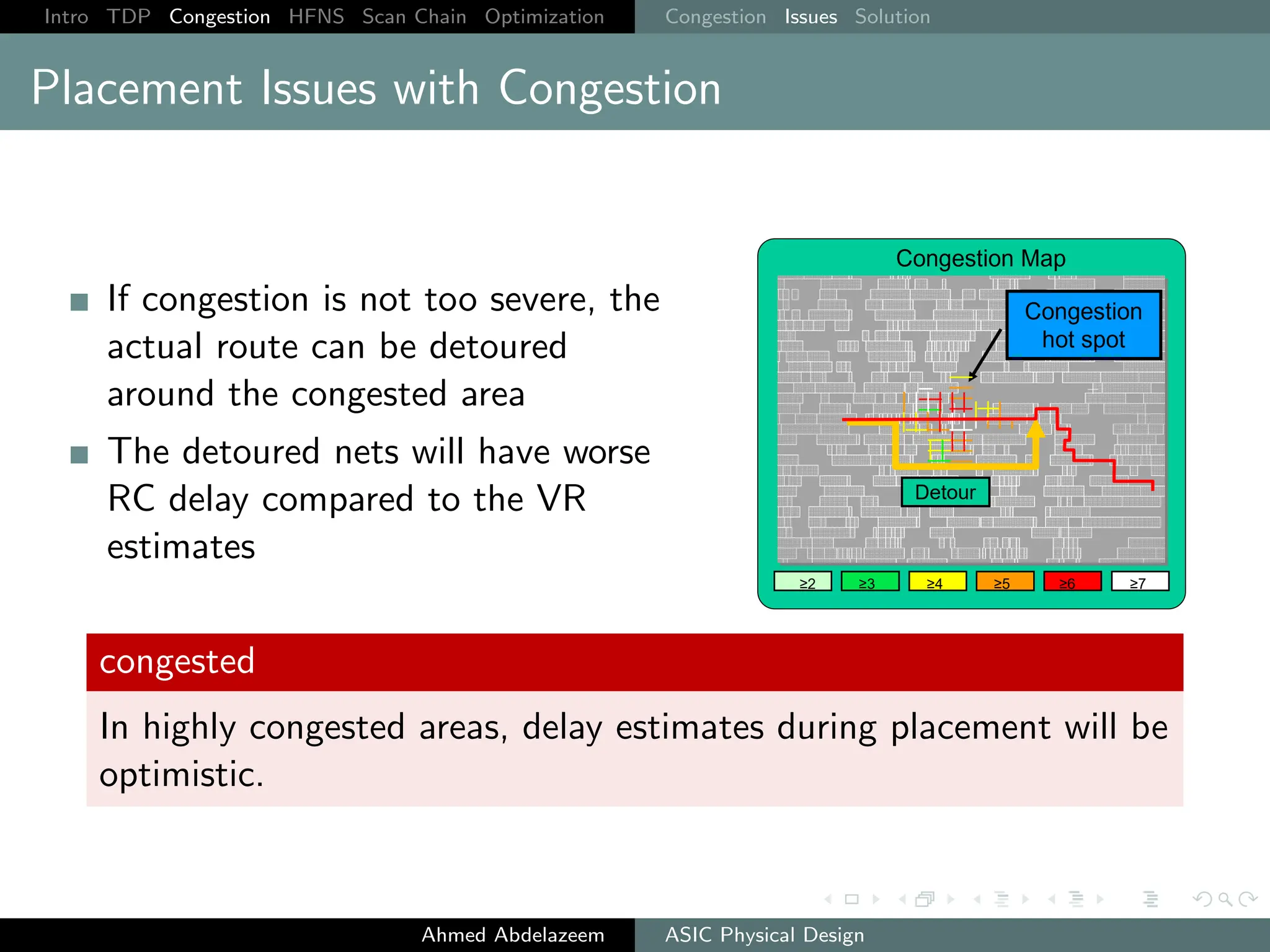

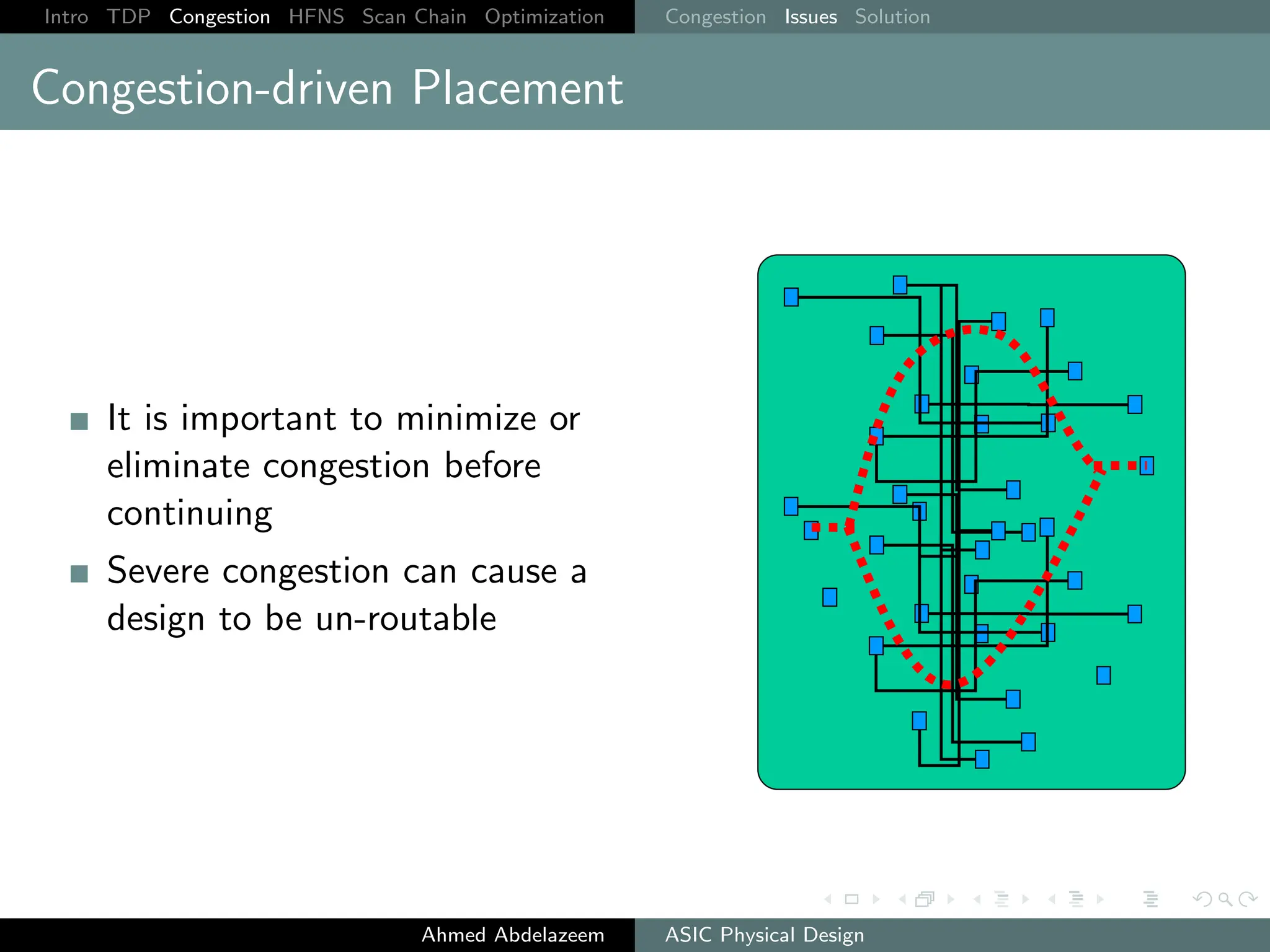

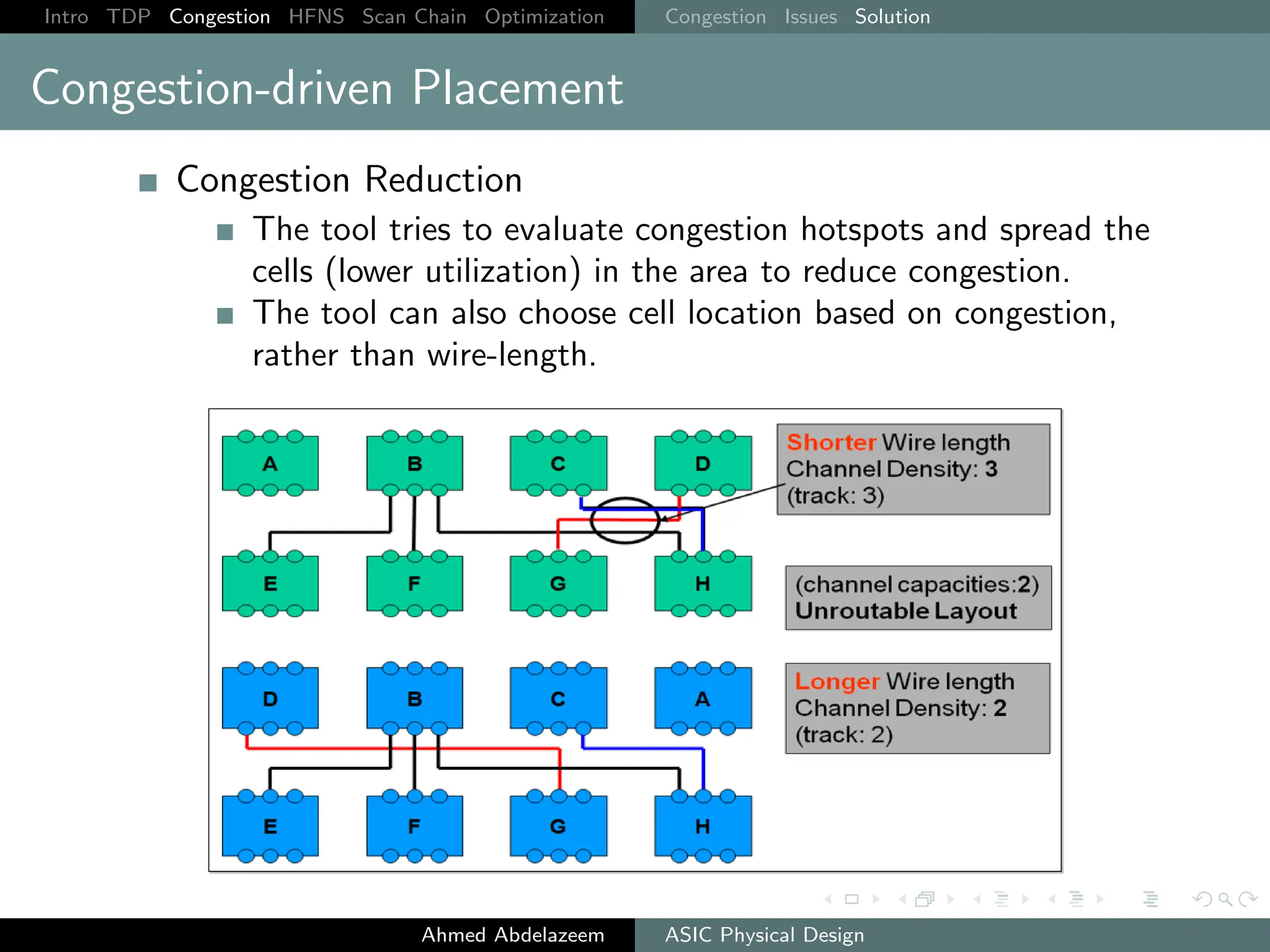

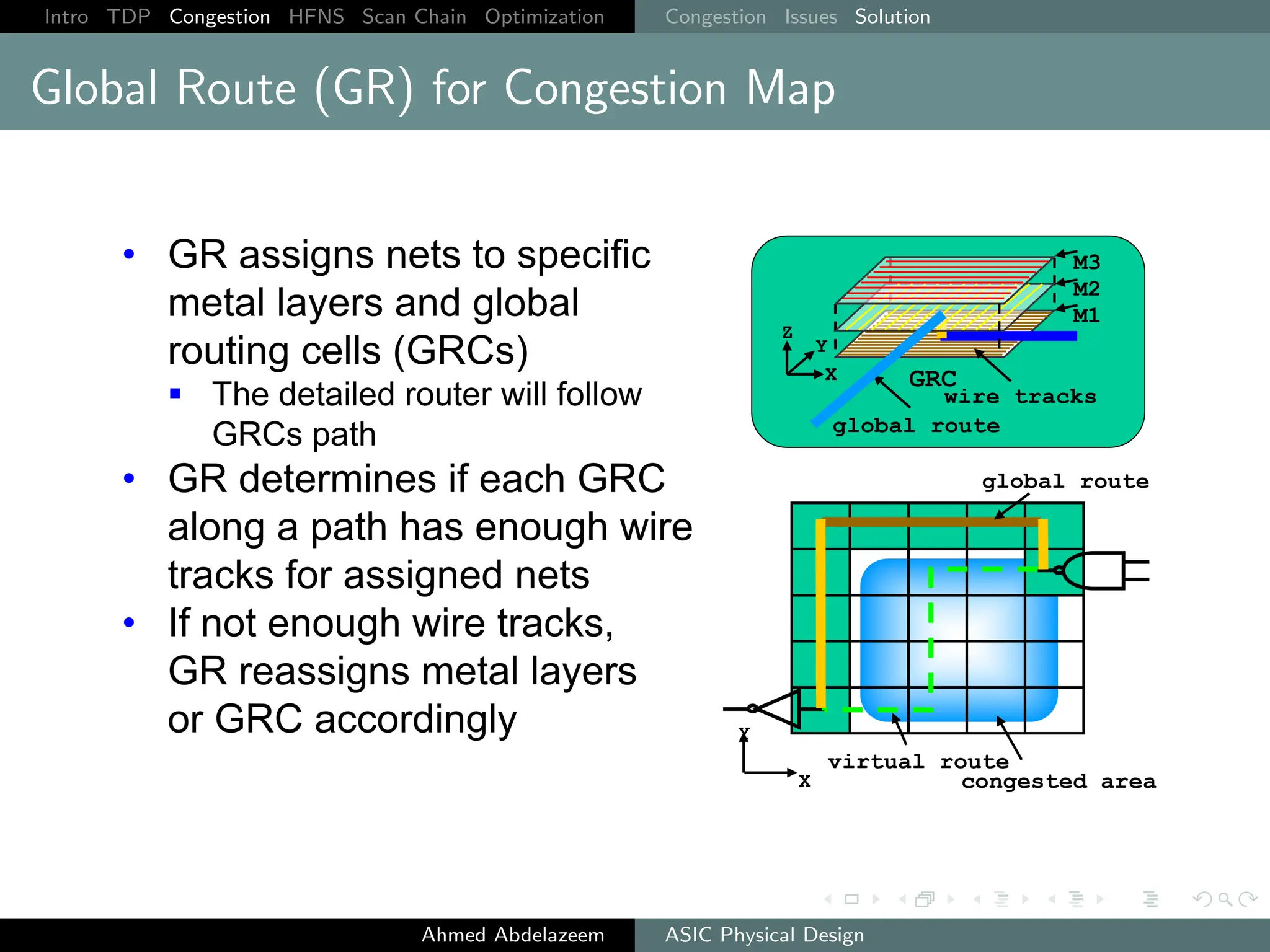

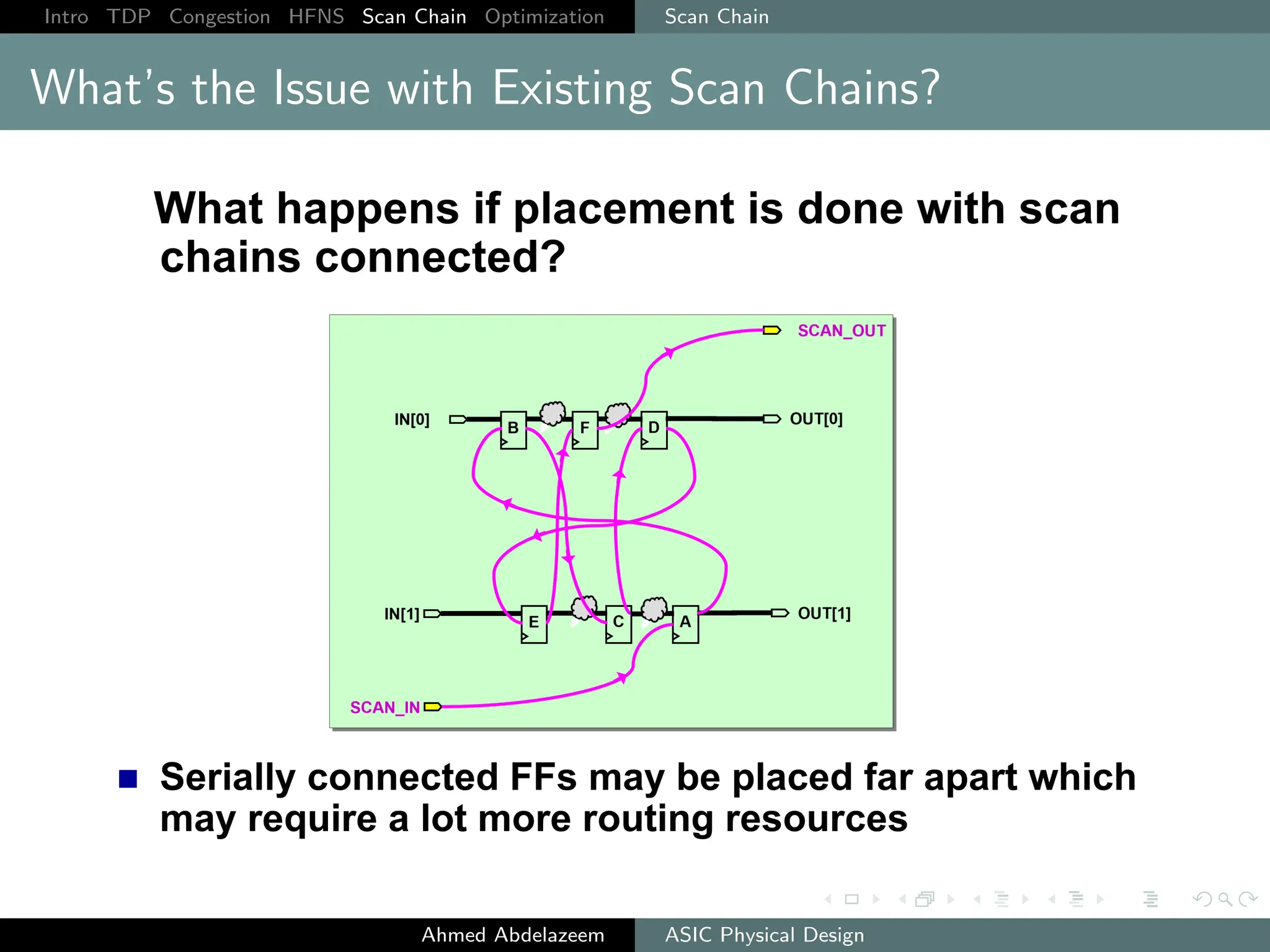

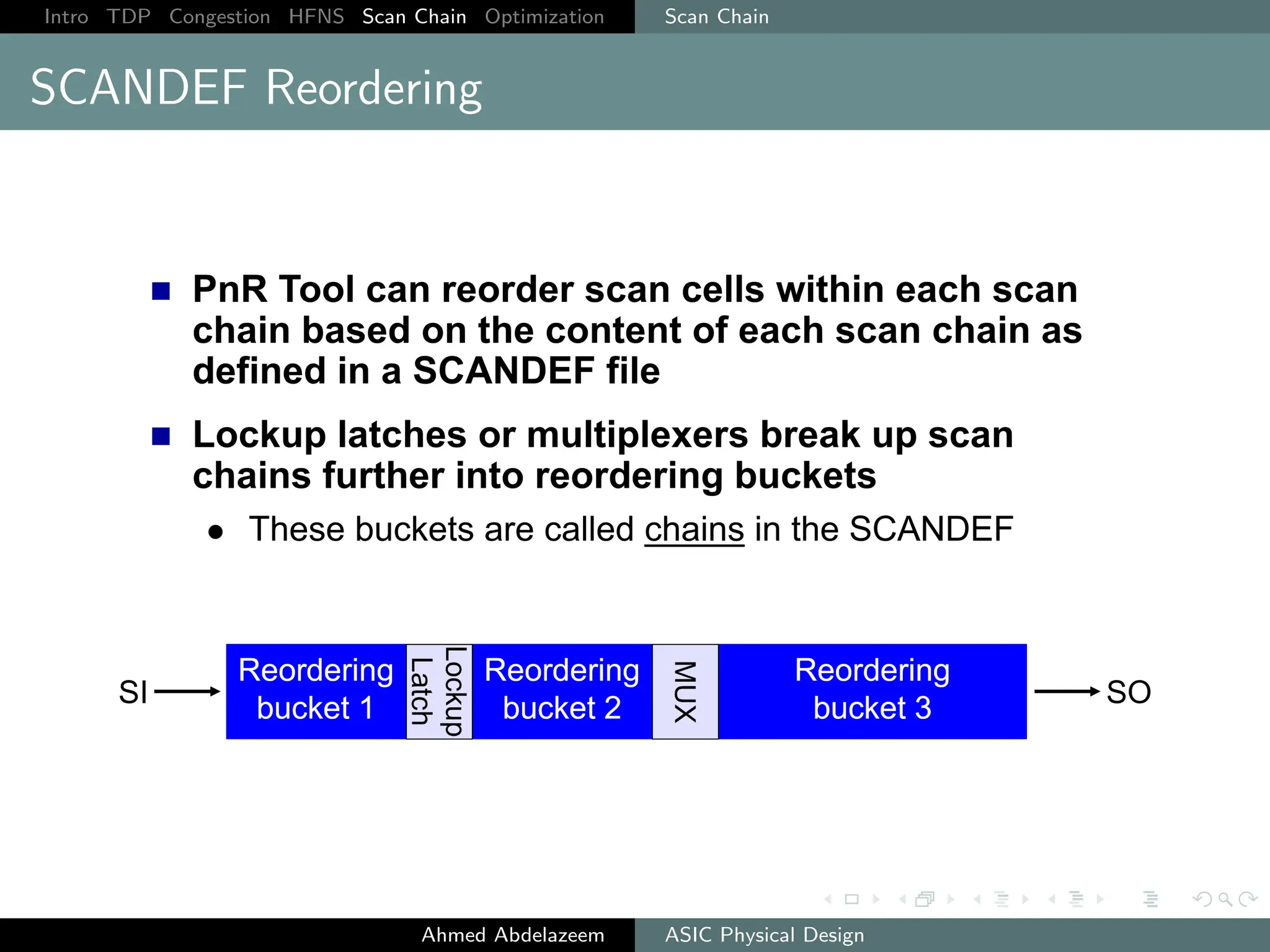

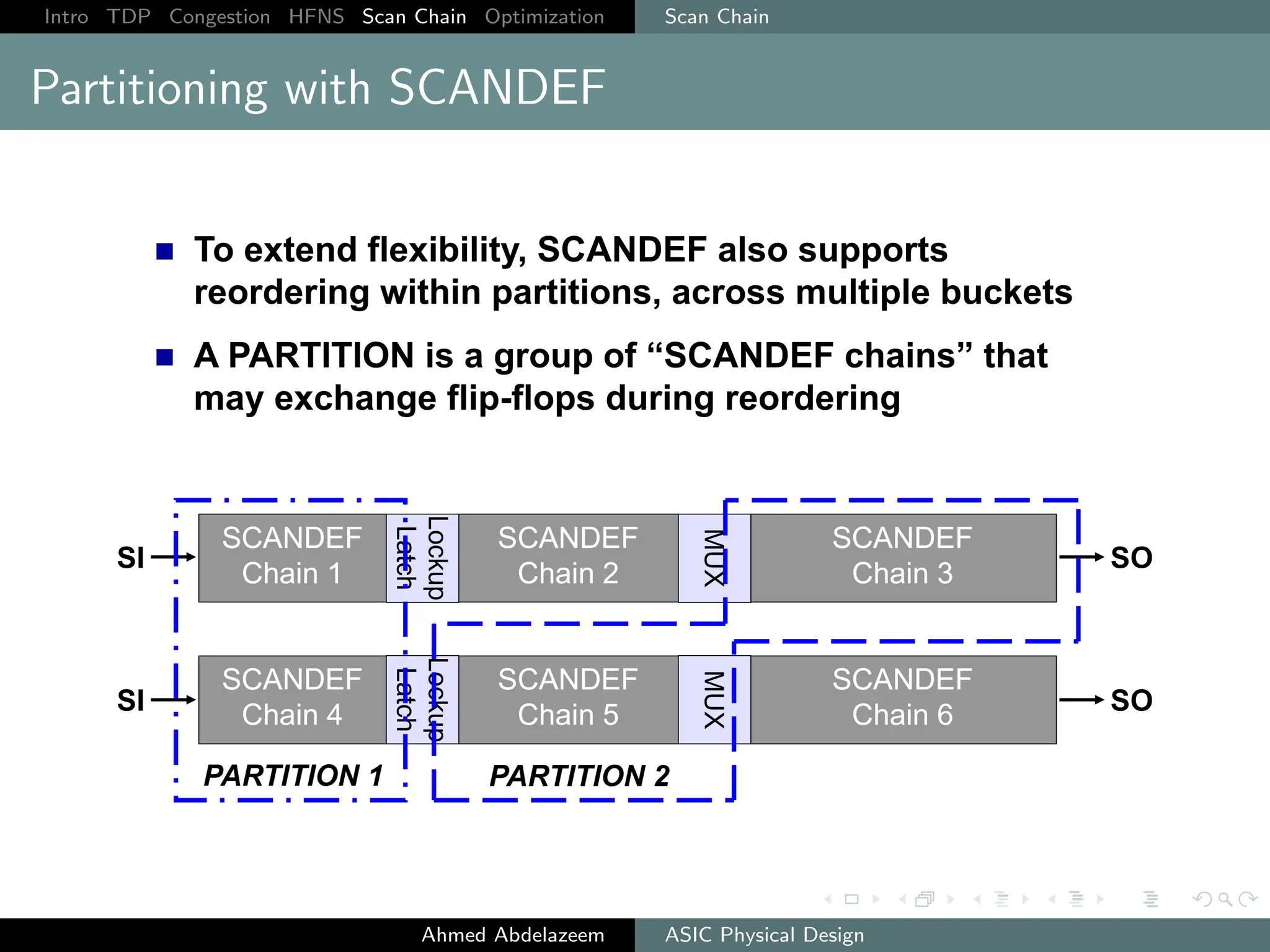

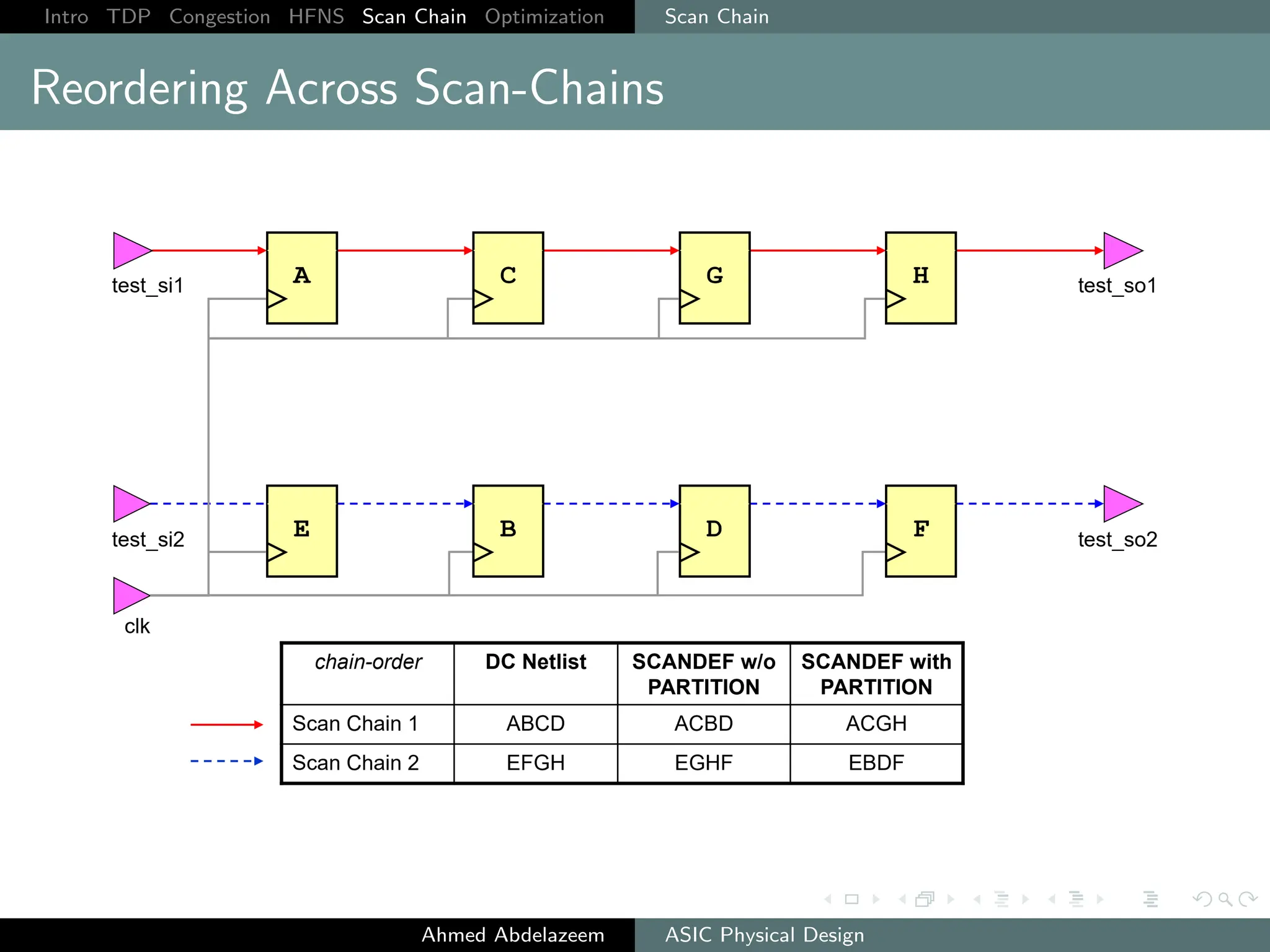

The document outlines the process of ASIC physical design and placement, particularly focusing on techniques for optimizing placement for timing and congestion. Key topics include timing-driven placement, congestion-driven placement, high fanout synthesis, and scan chain optimization, emphasizing the importance of circuit placement in modern technology nodes (65nm and below). Strategies to minimize routing congestion and ensure legal cell placement are discussed to meet timing and area constraints.