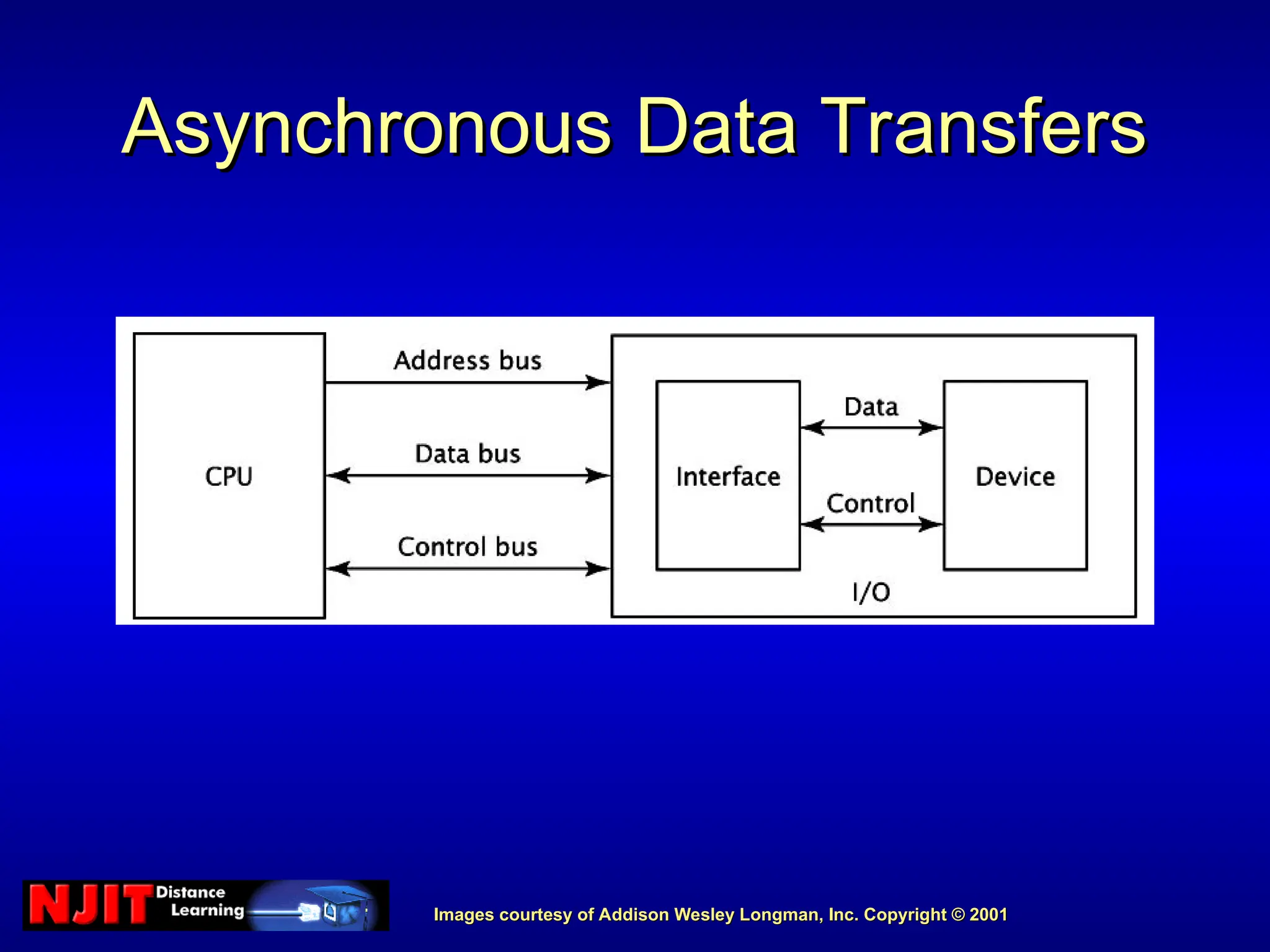

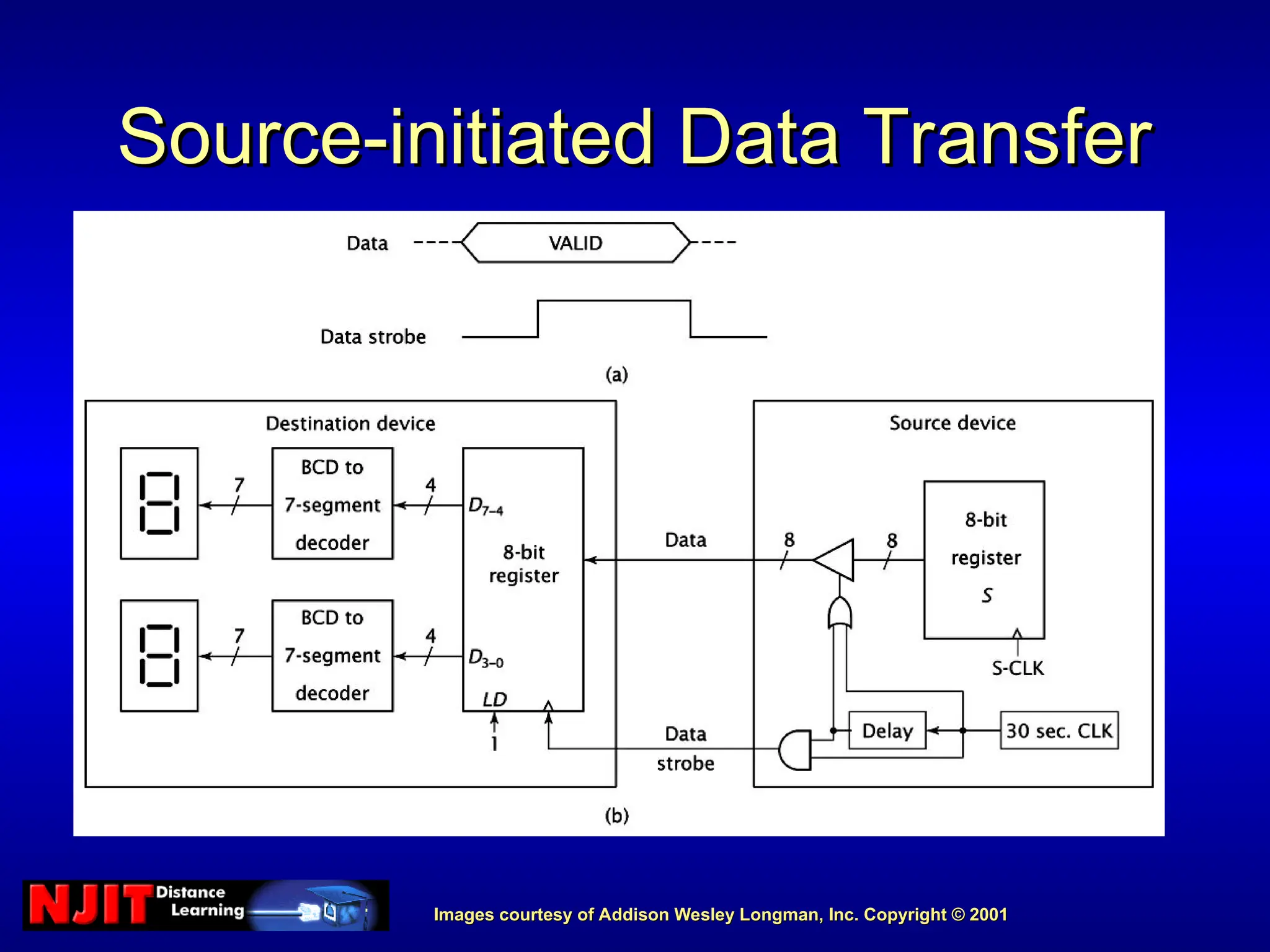

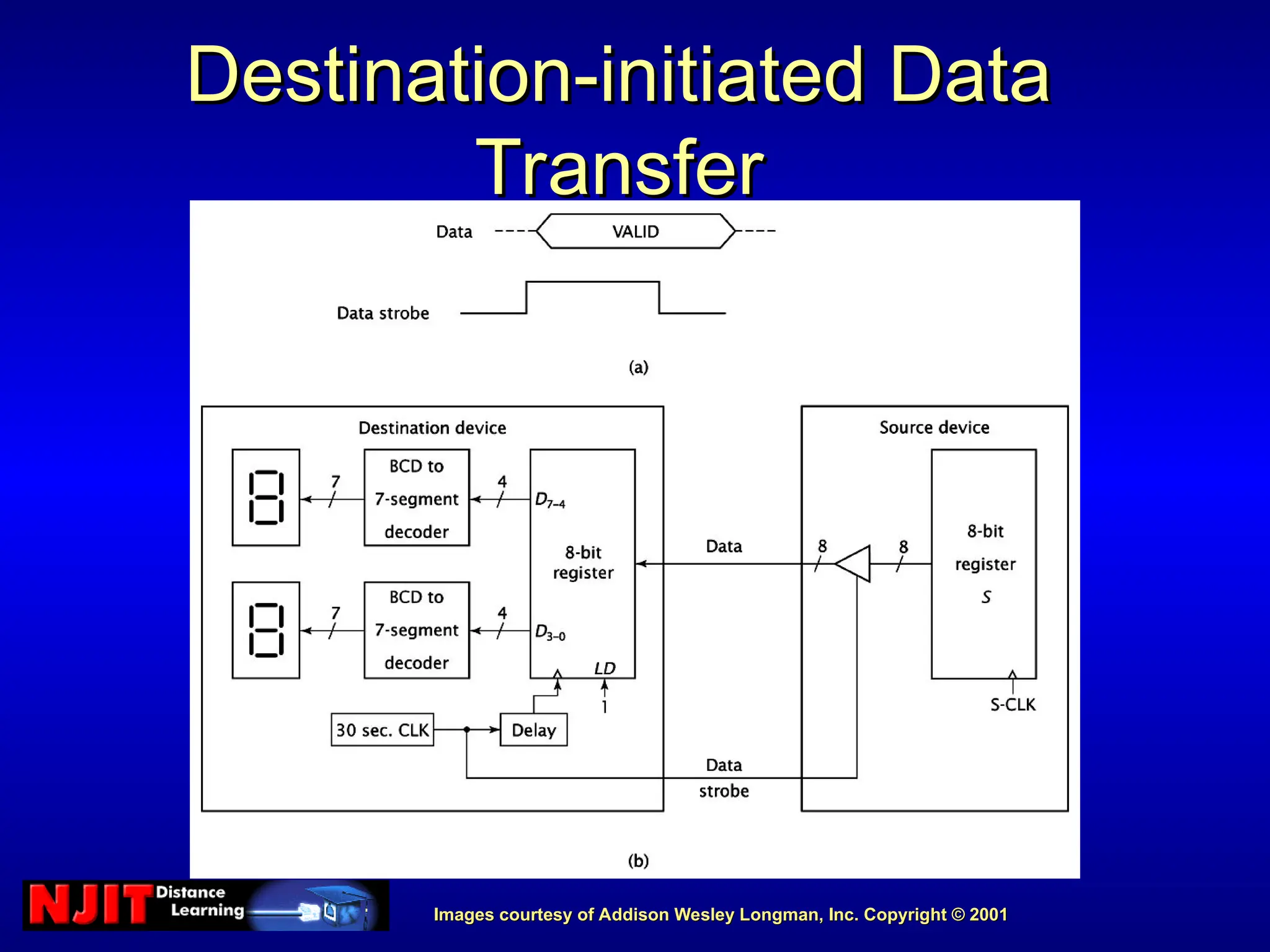

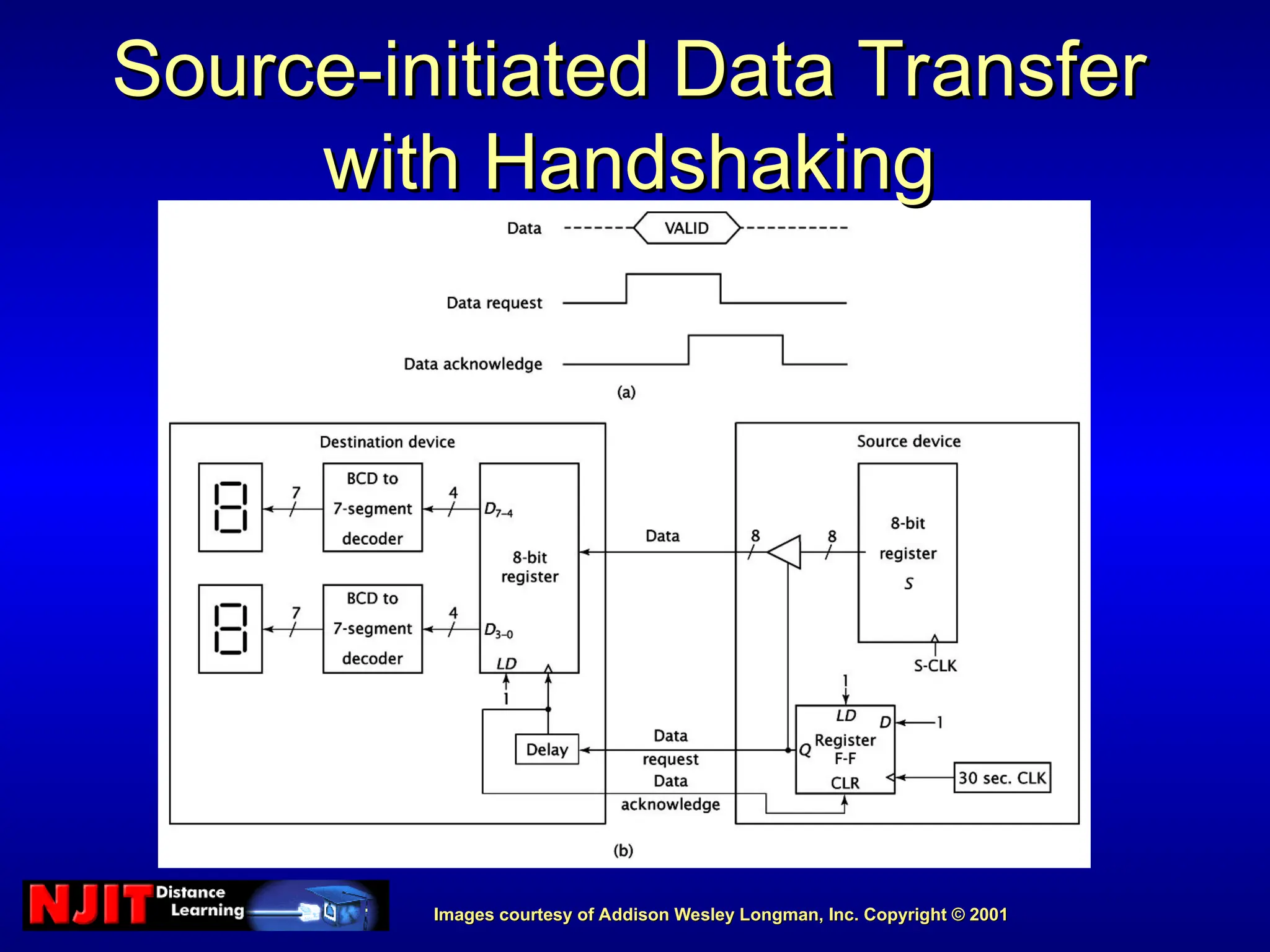

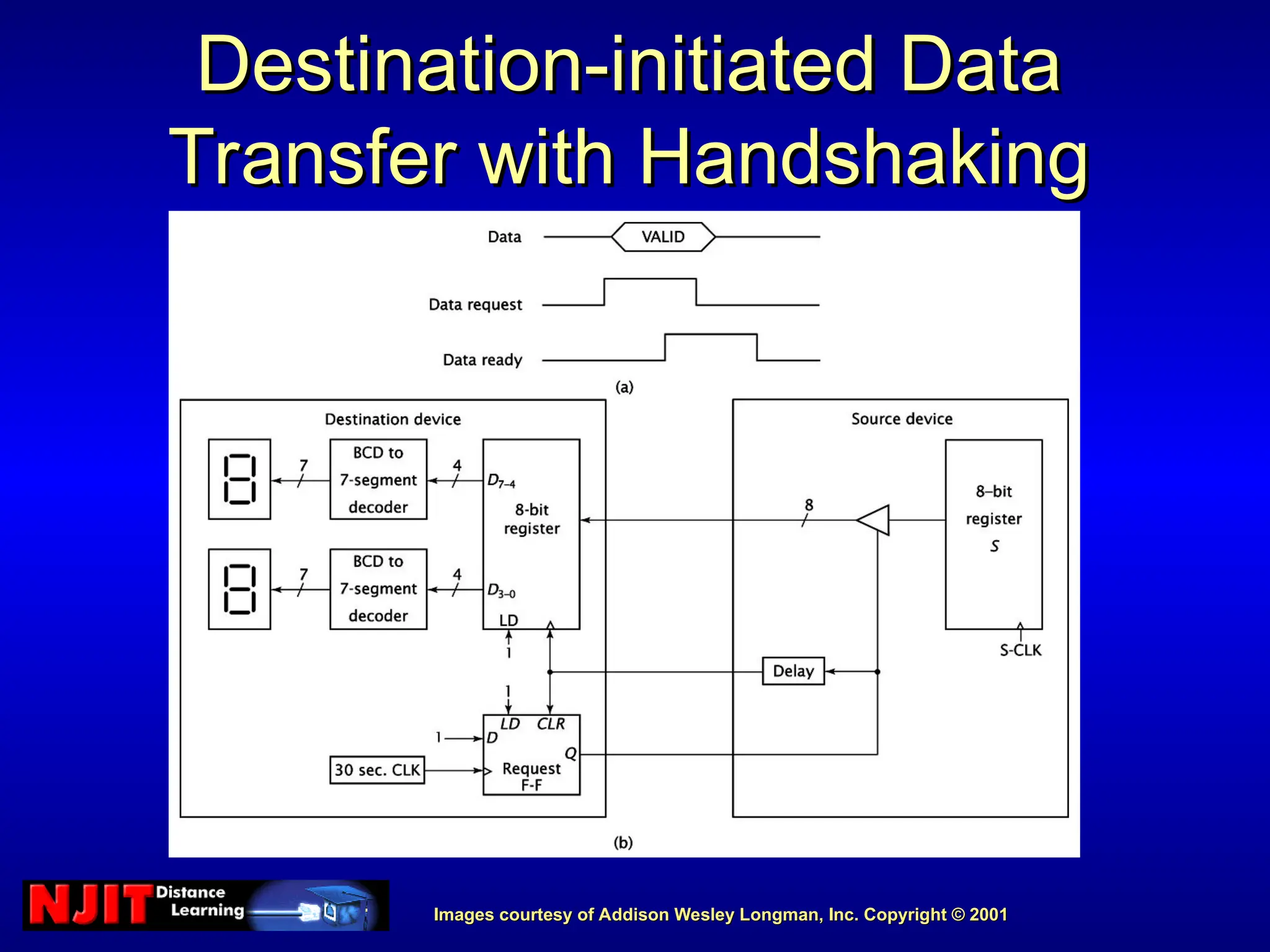

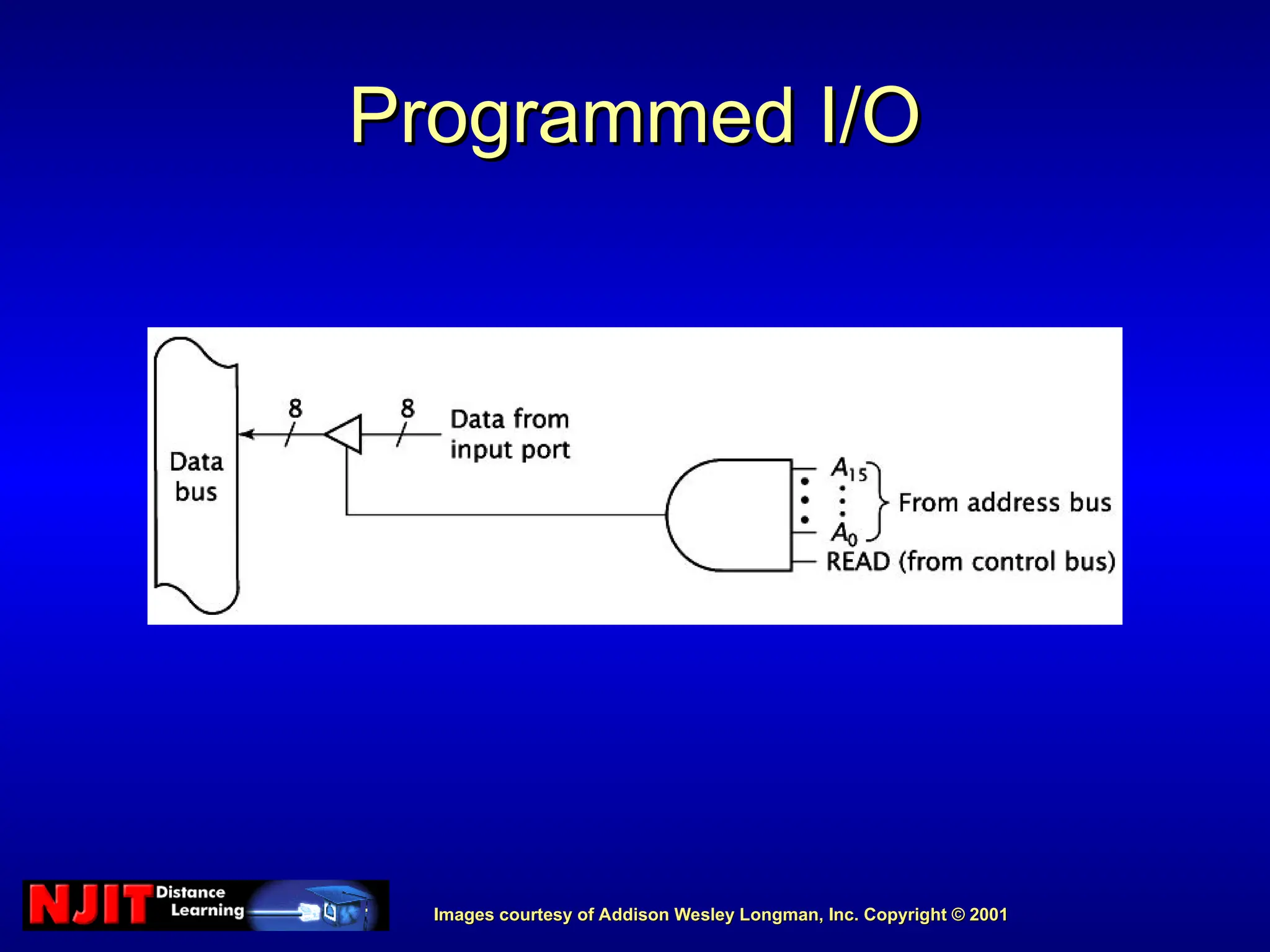

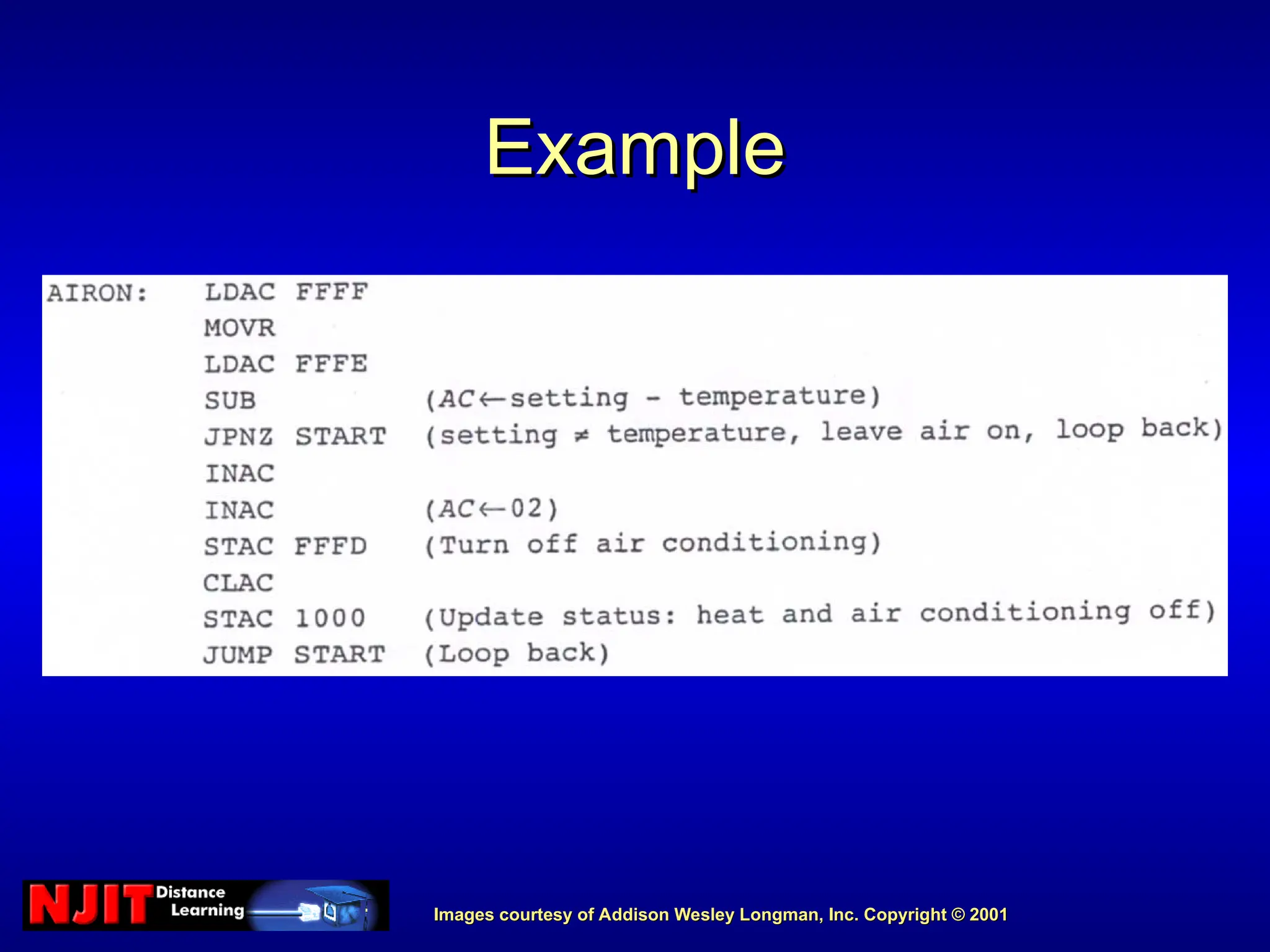

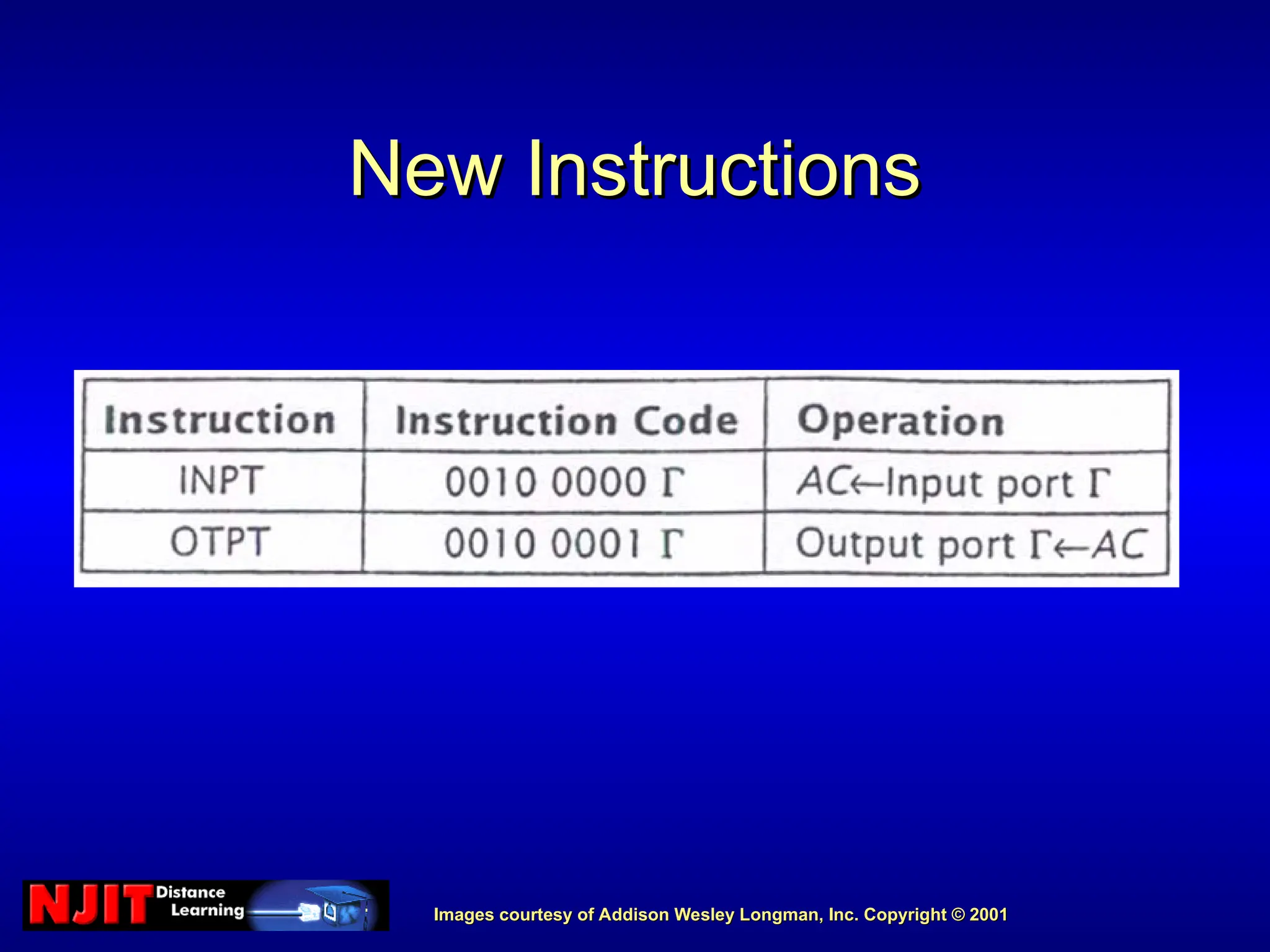

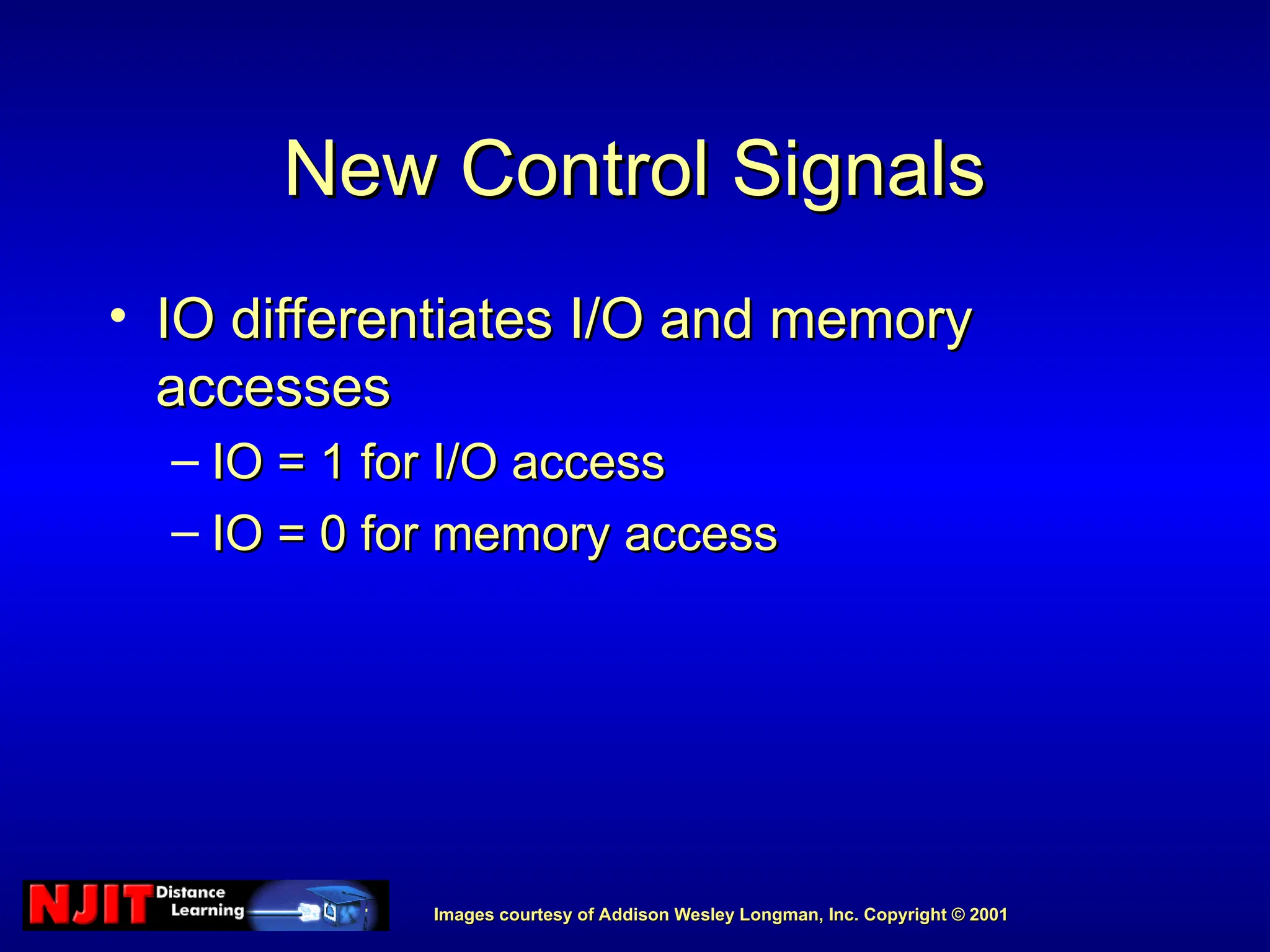

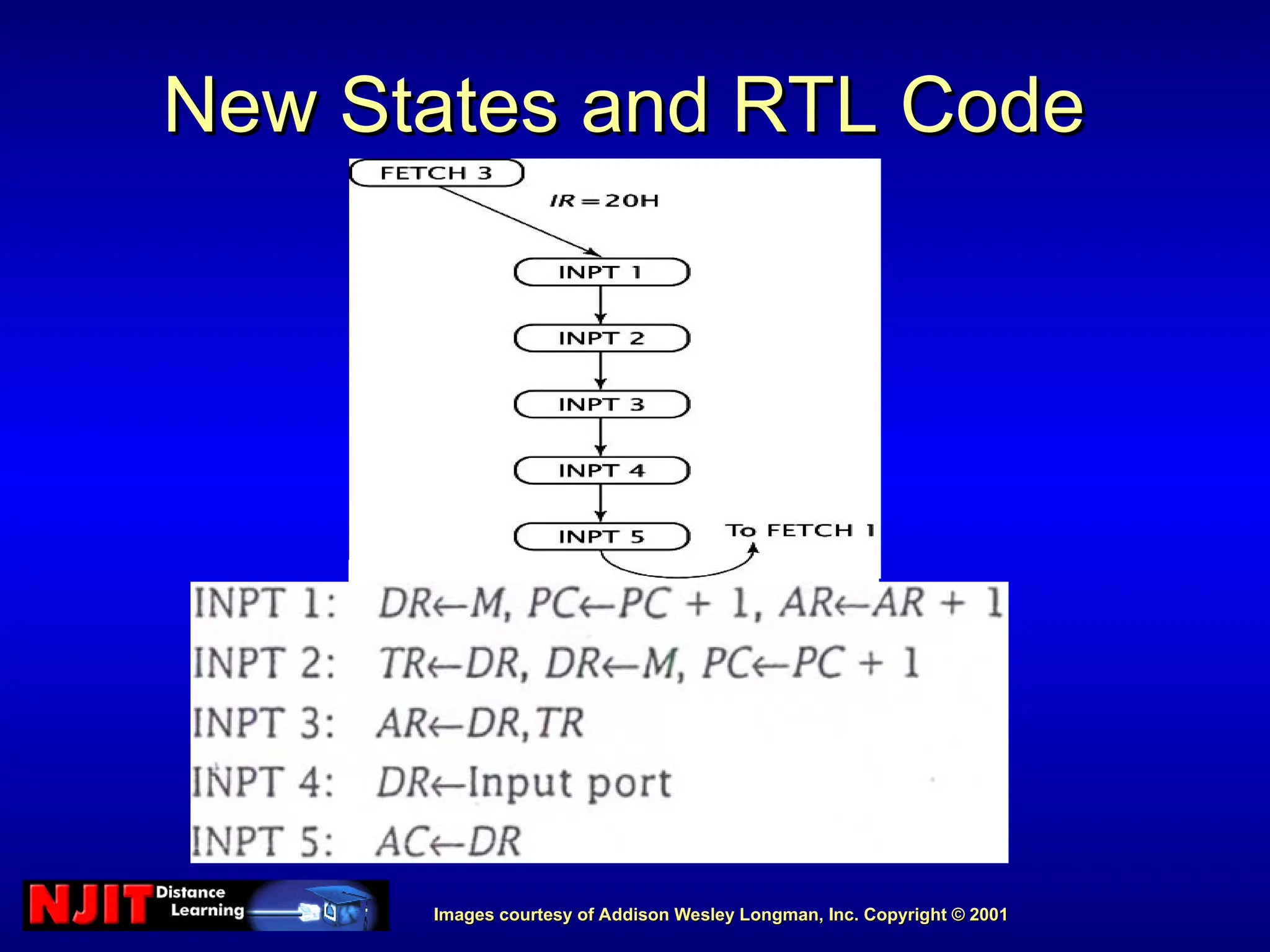

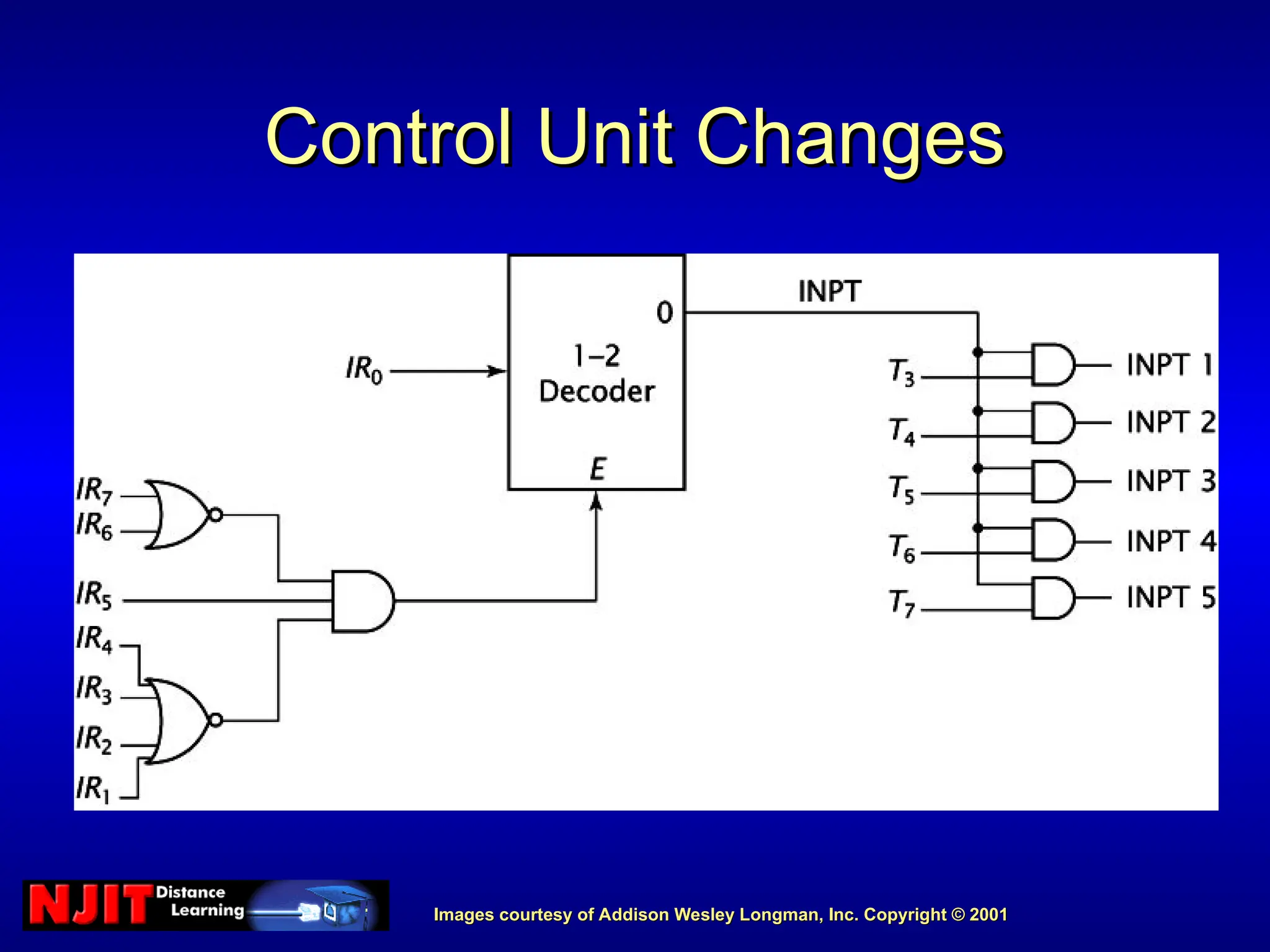

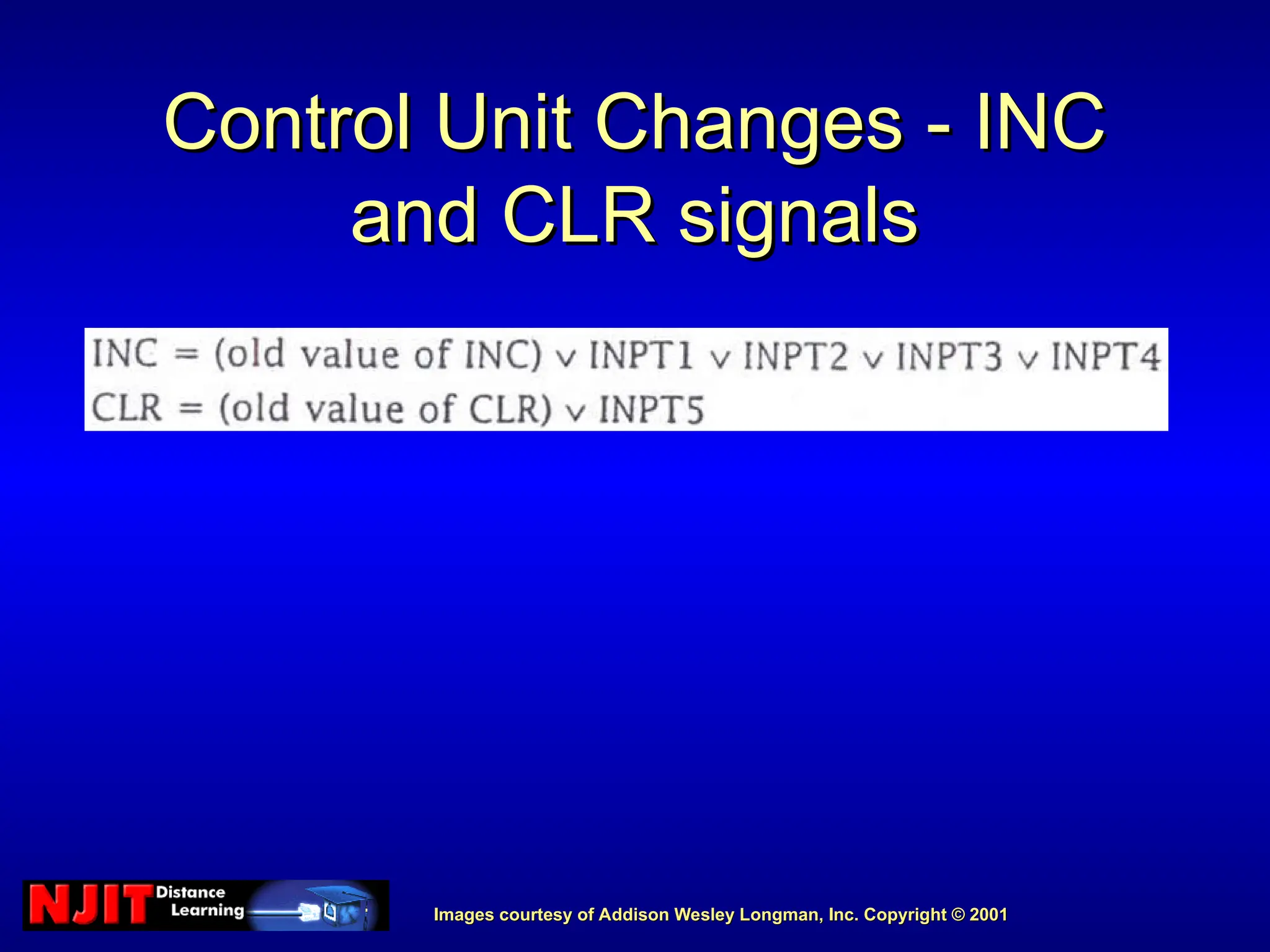

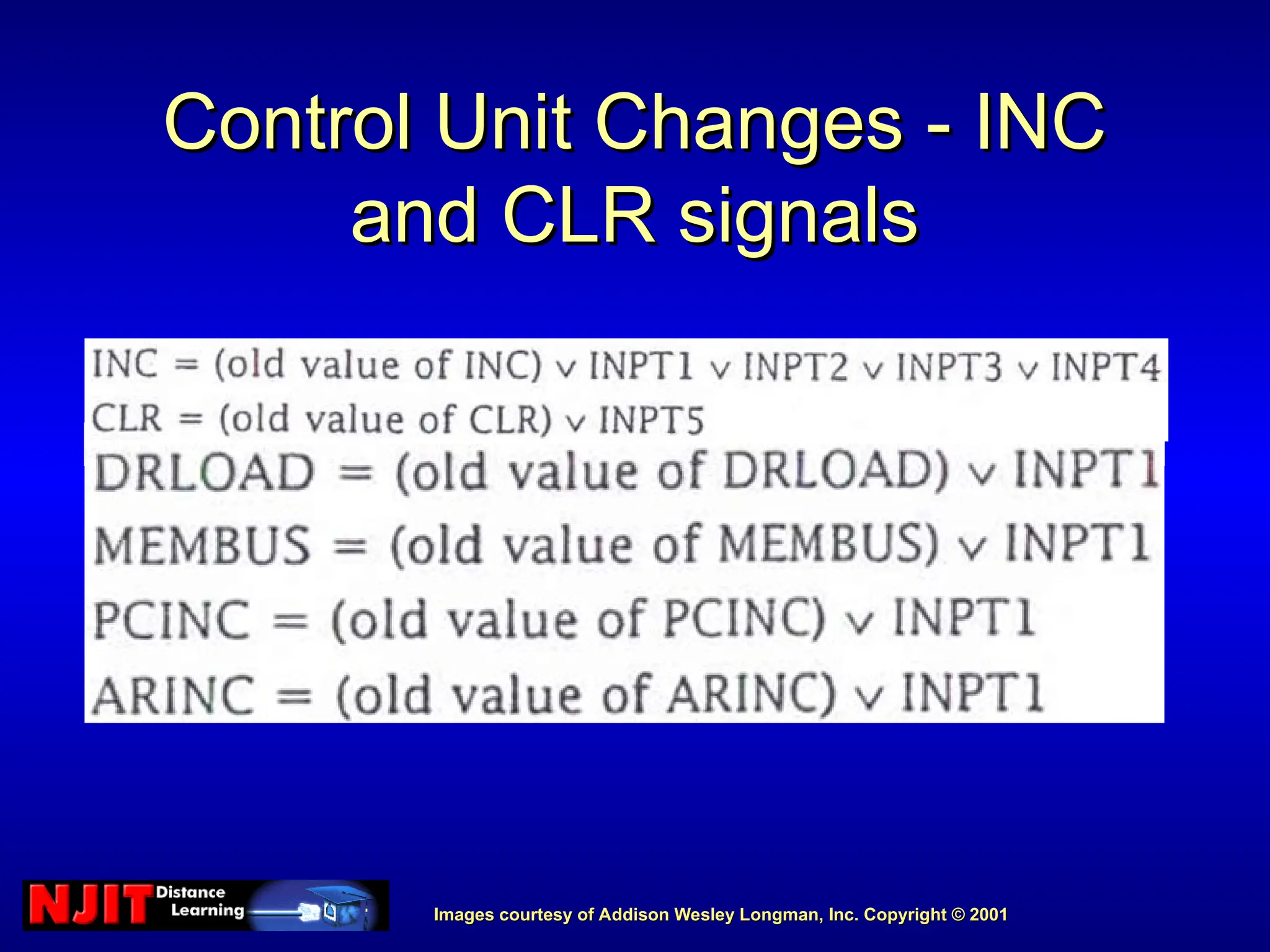

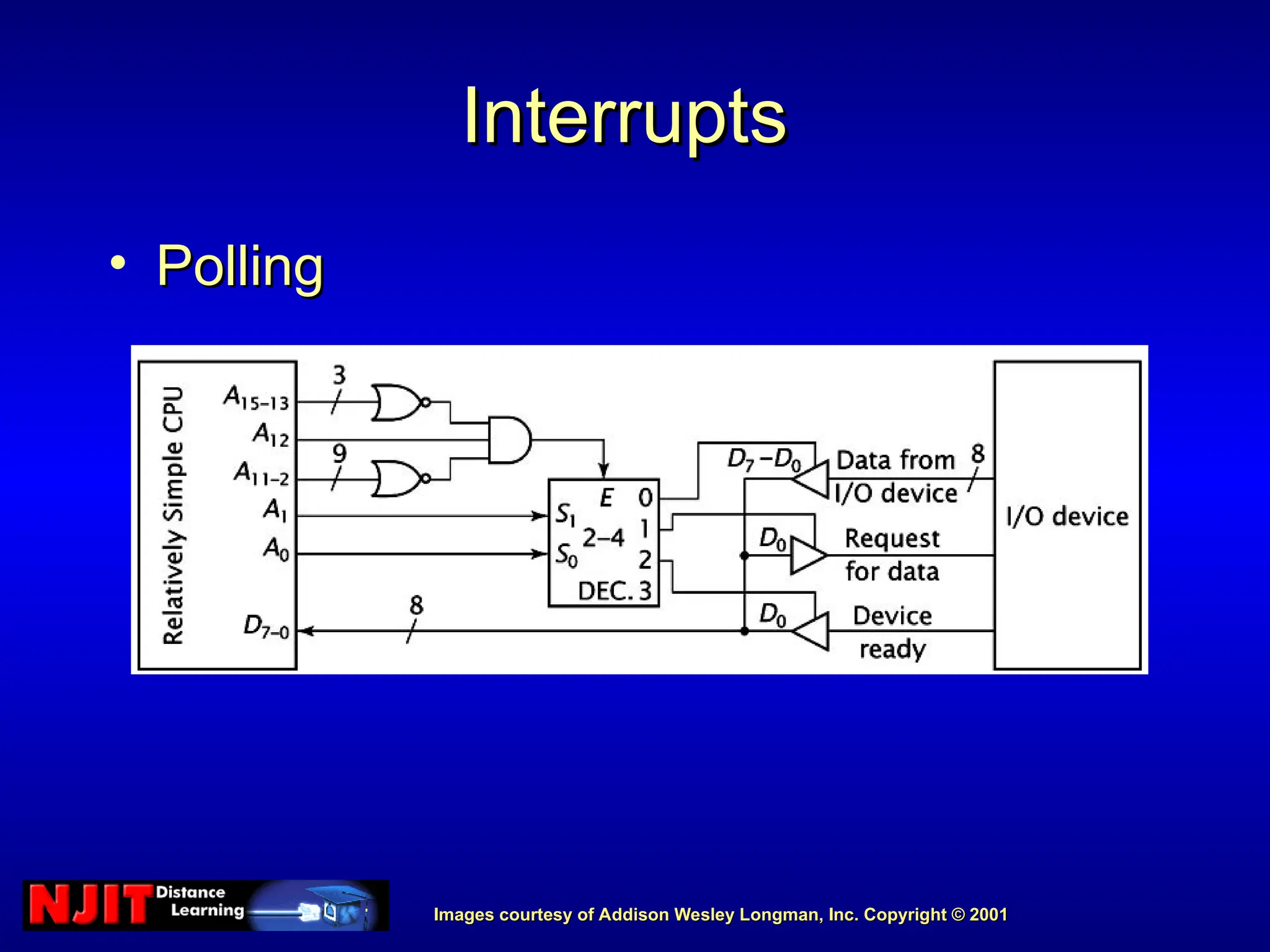

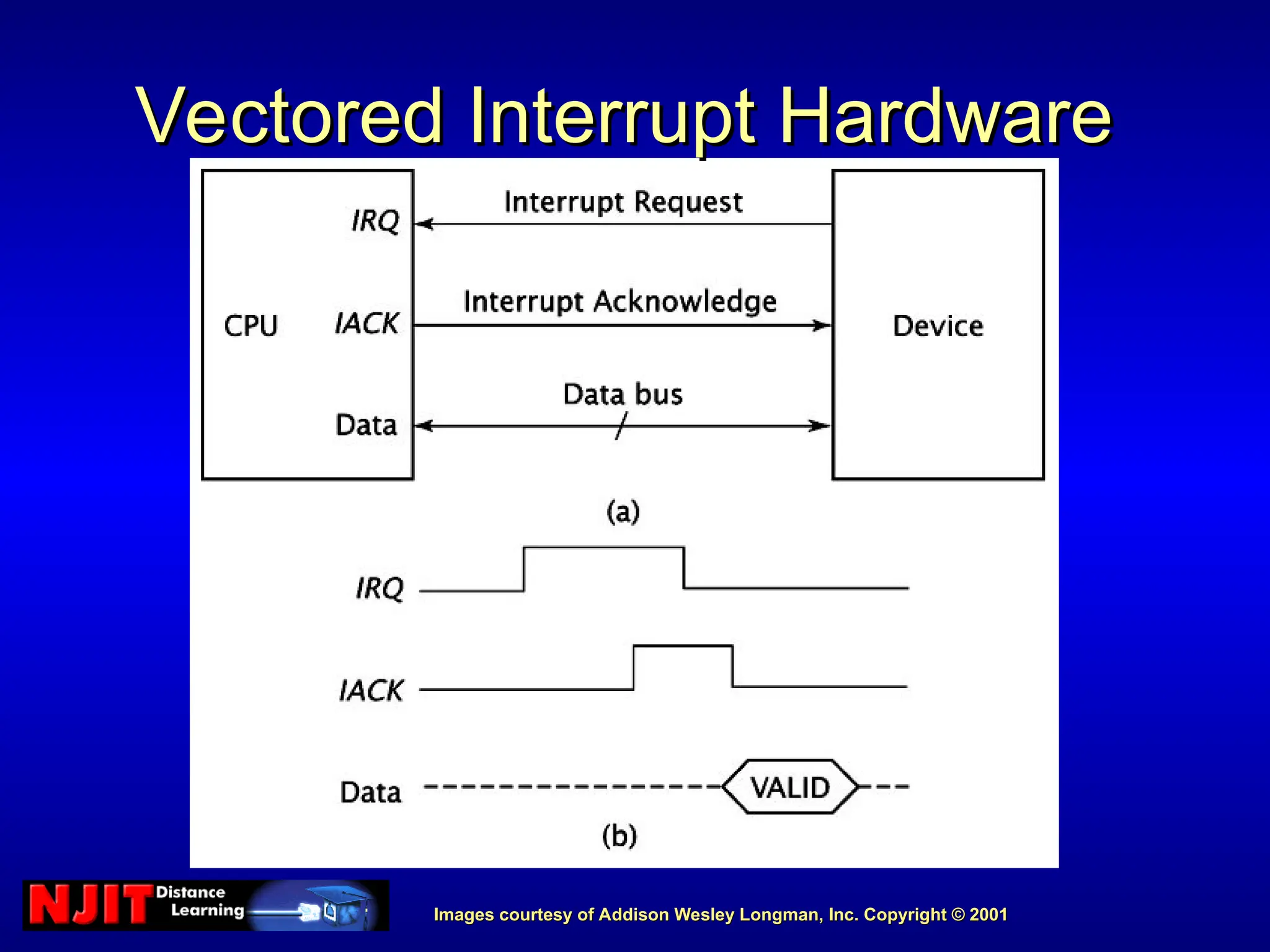

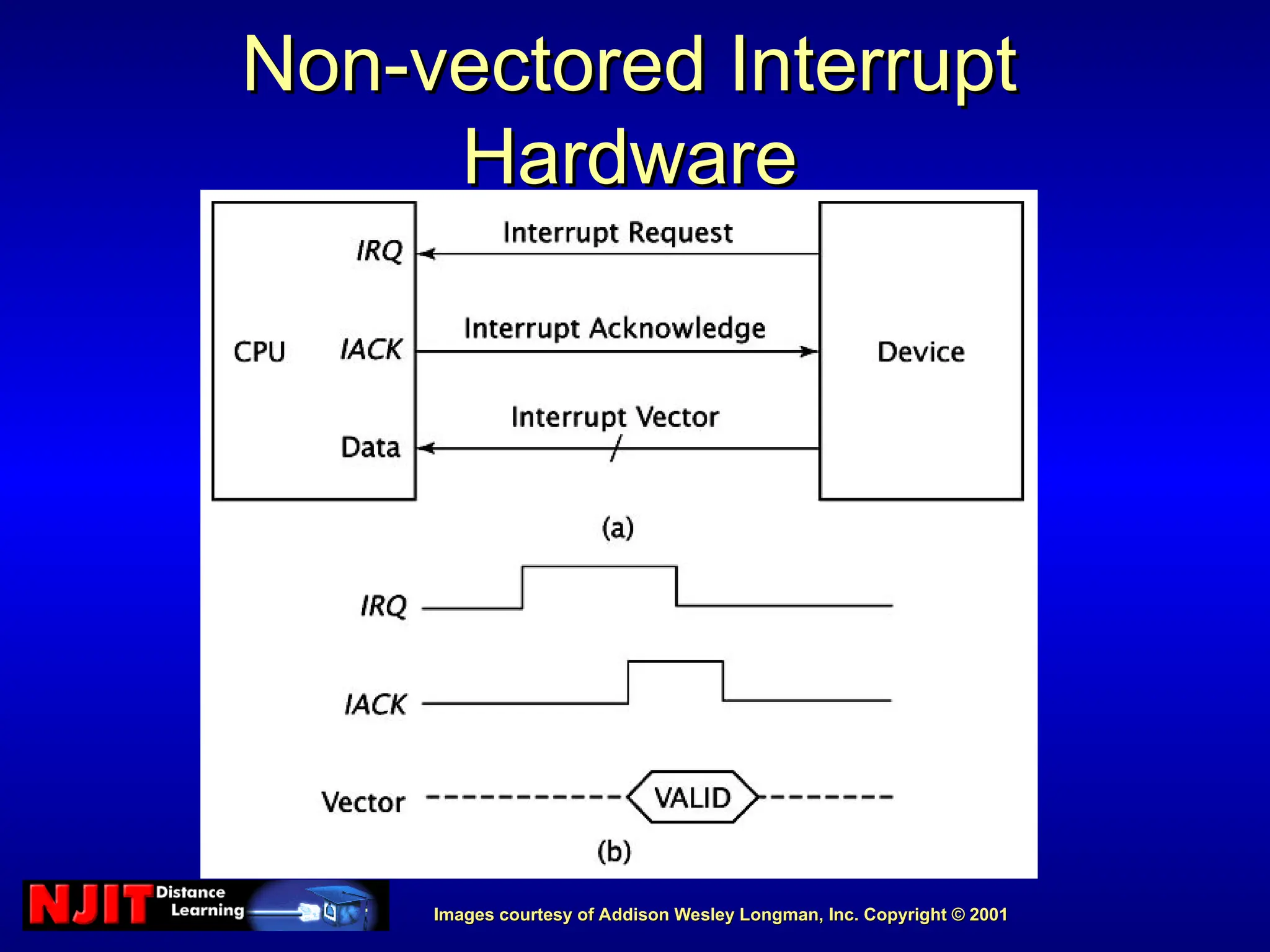

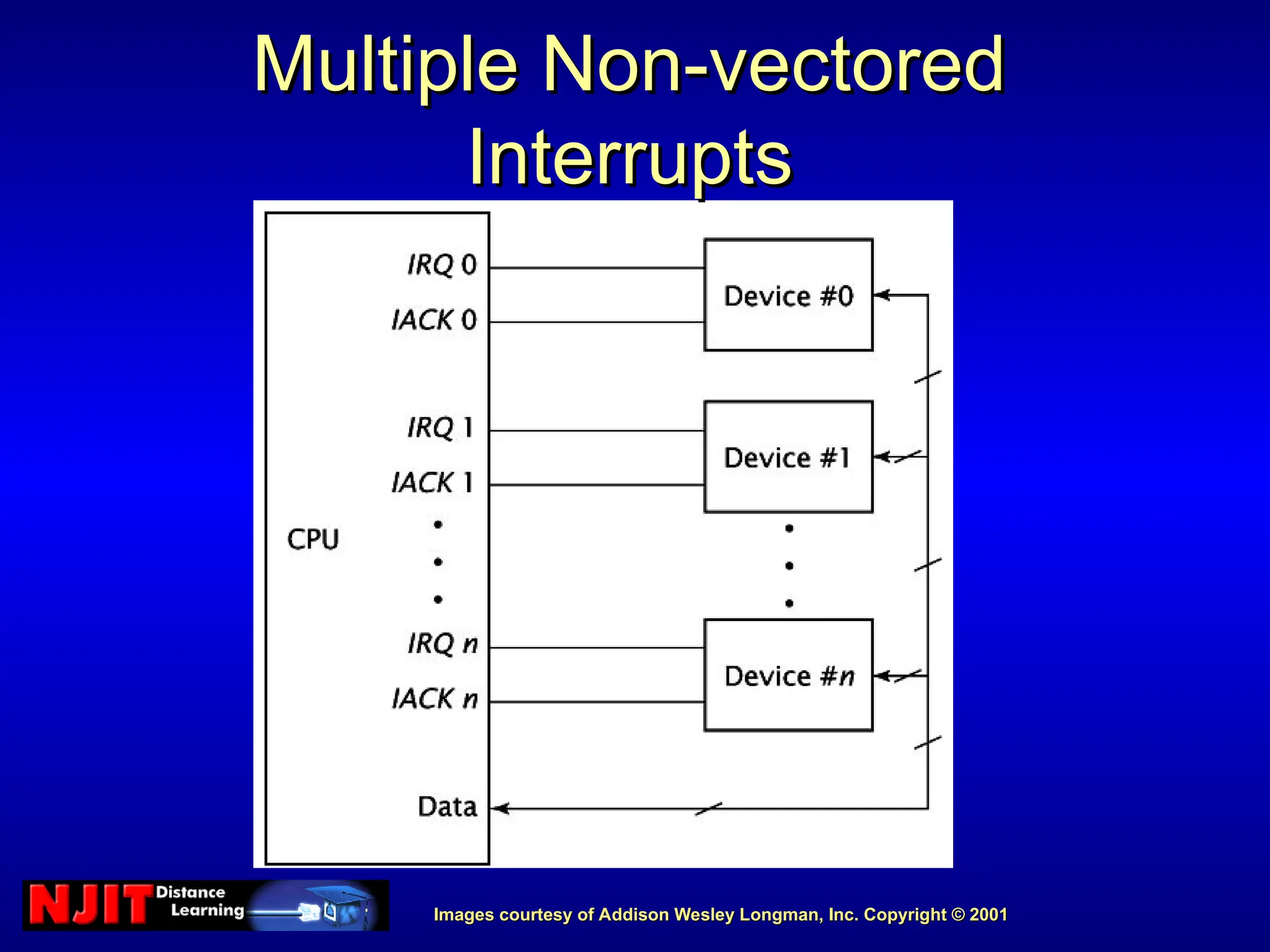

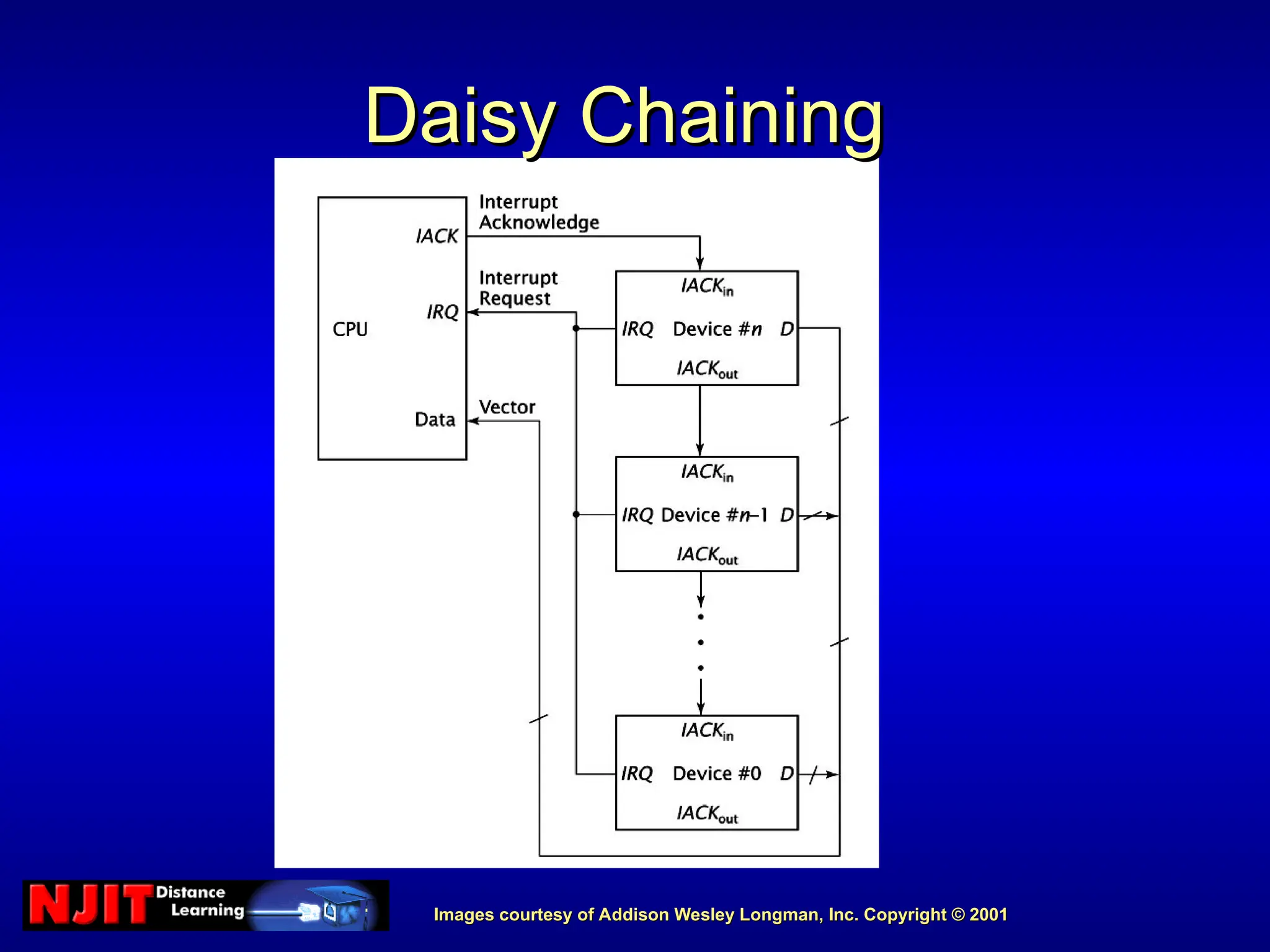

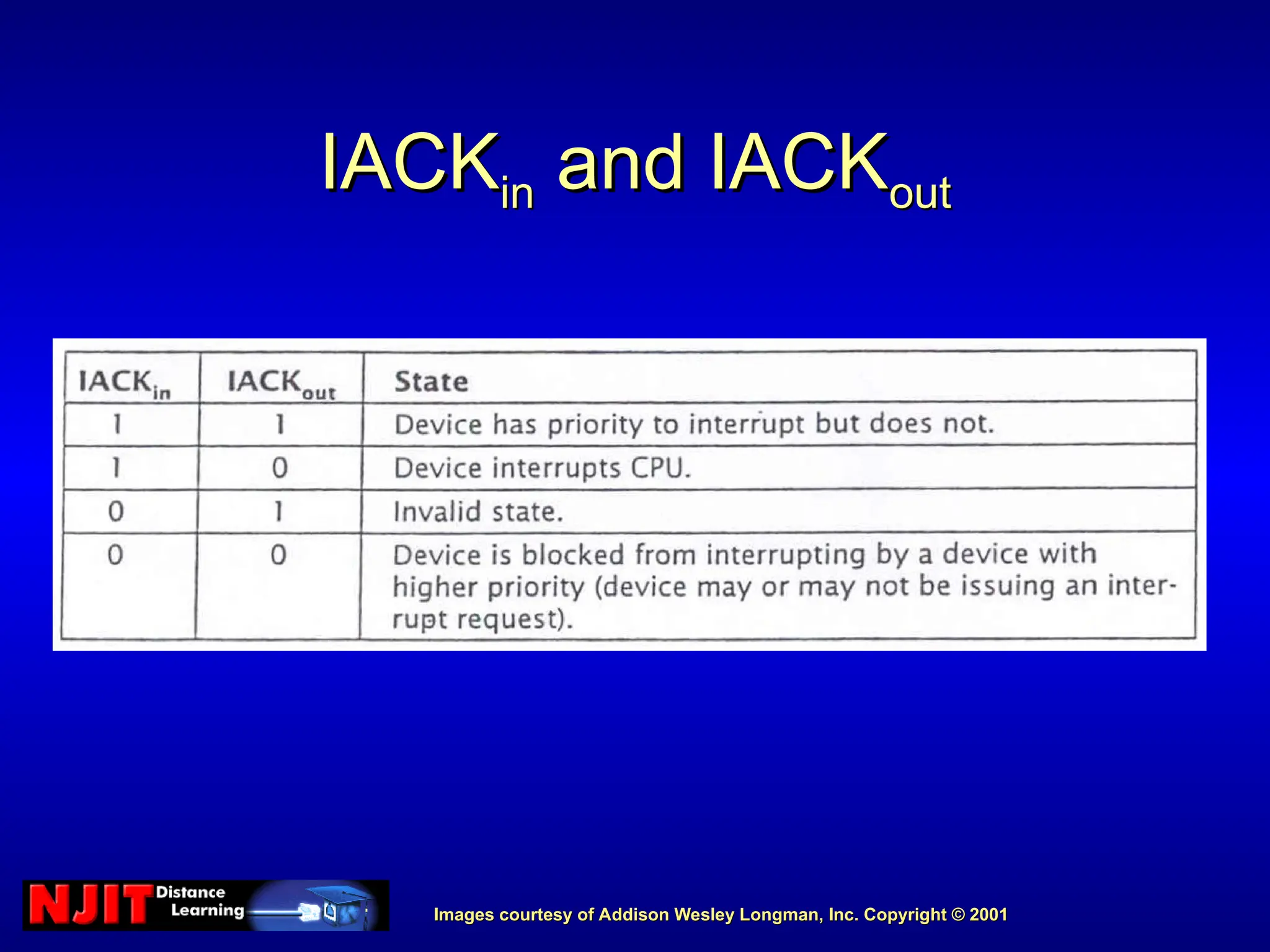

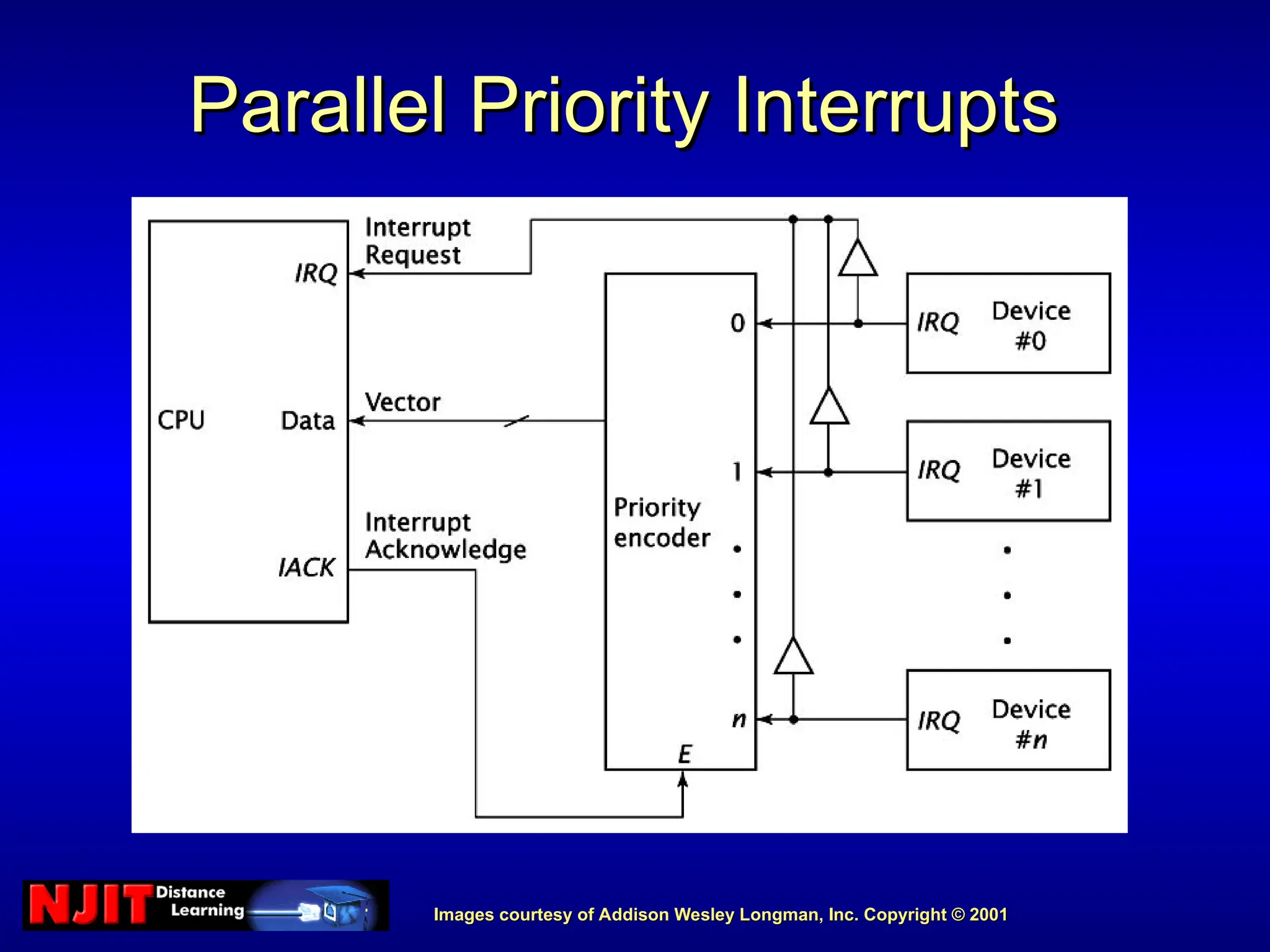

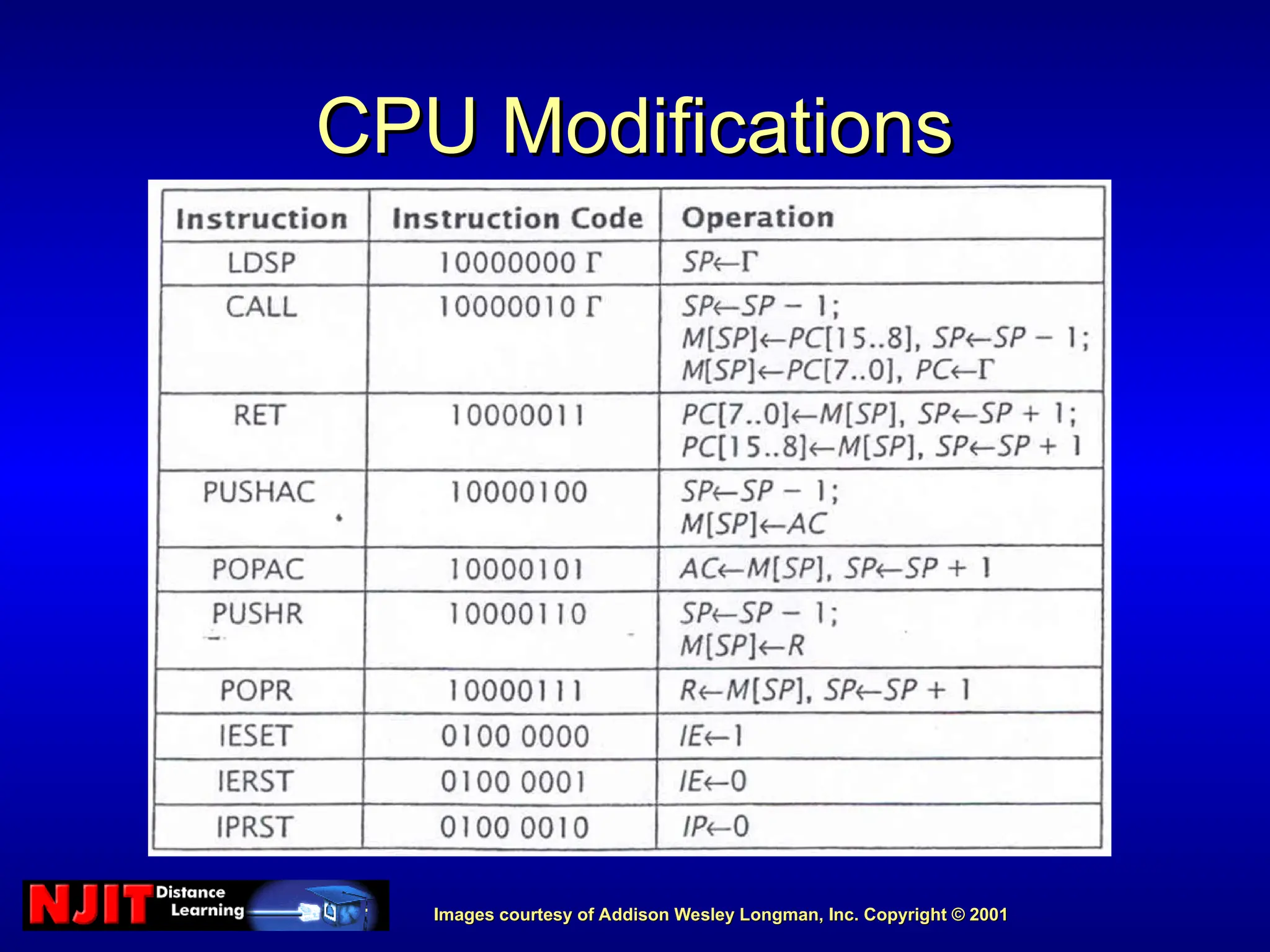

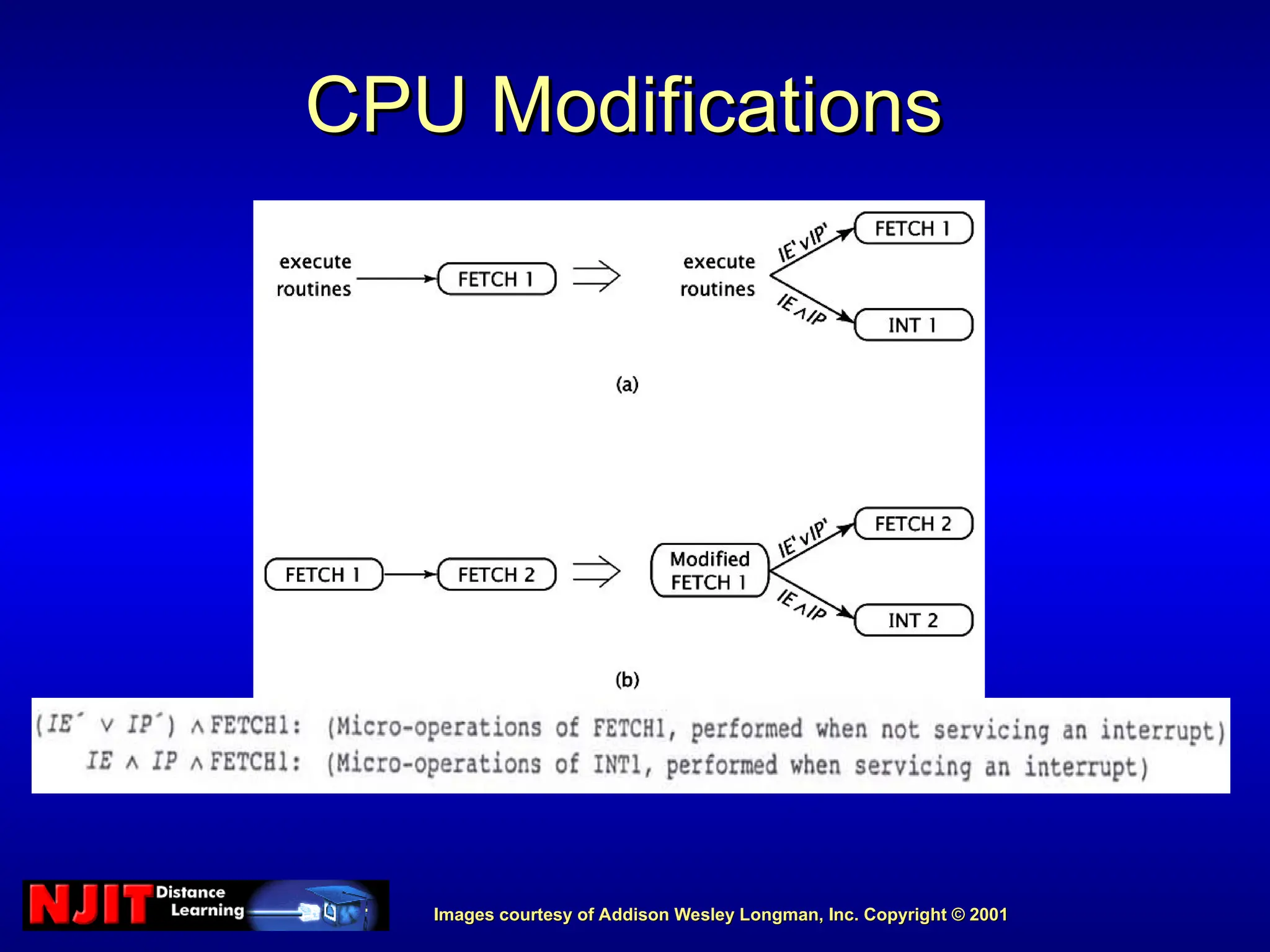

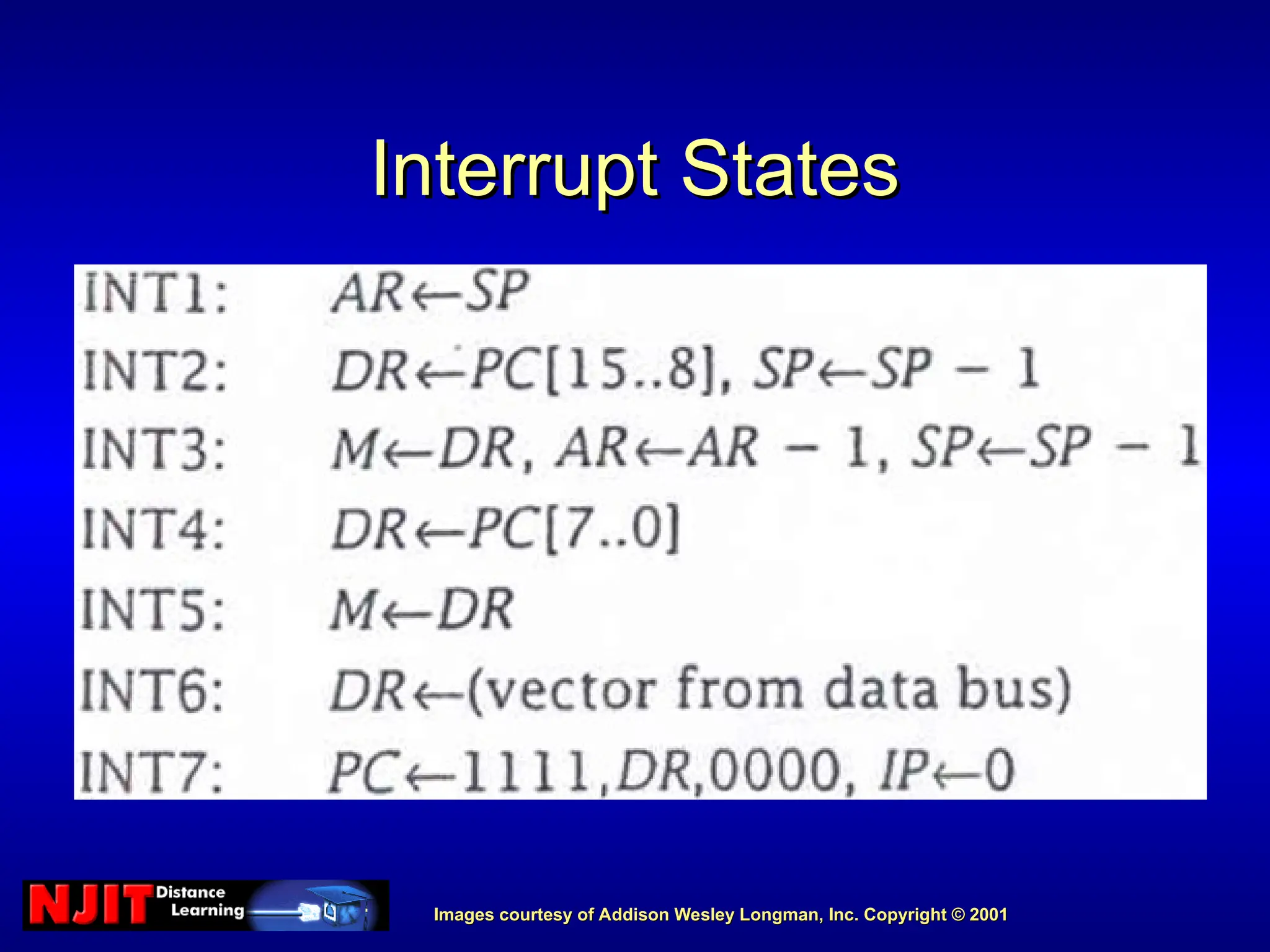

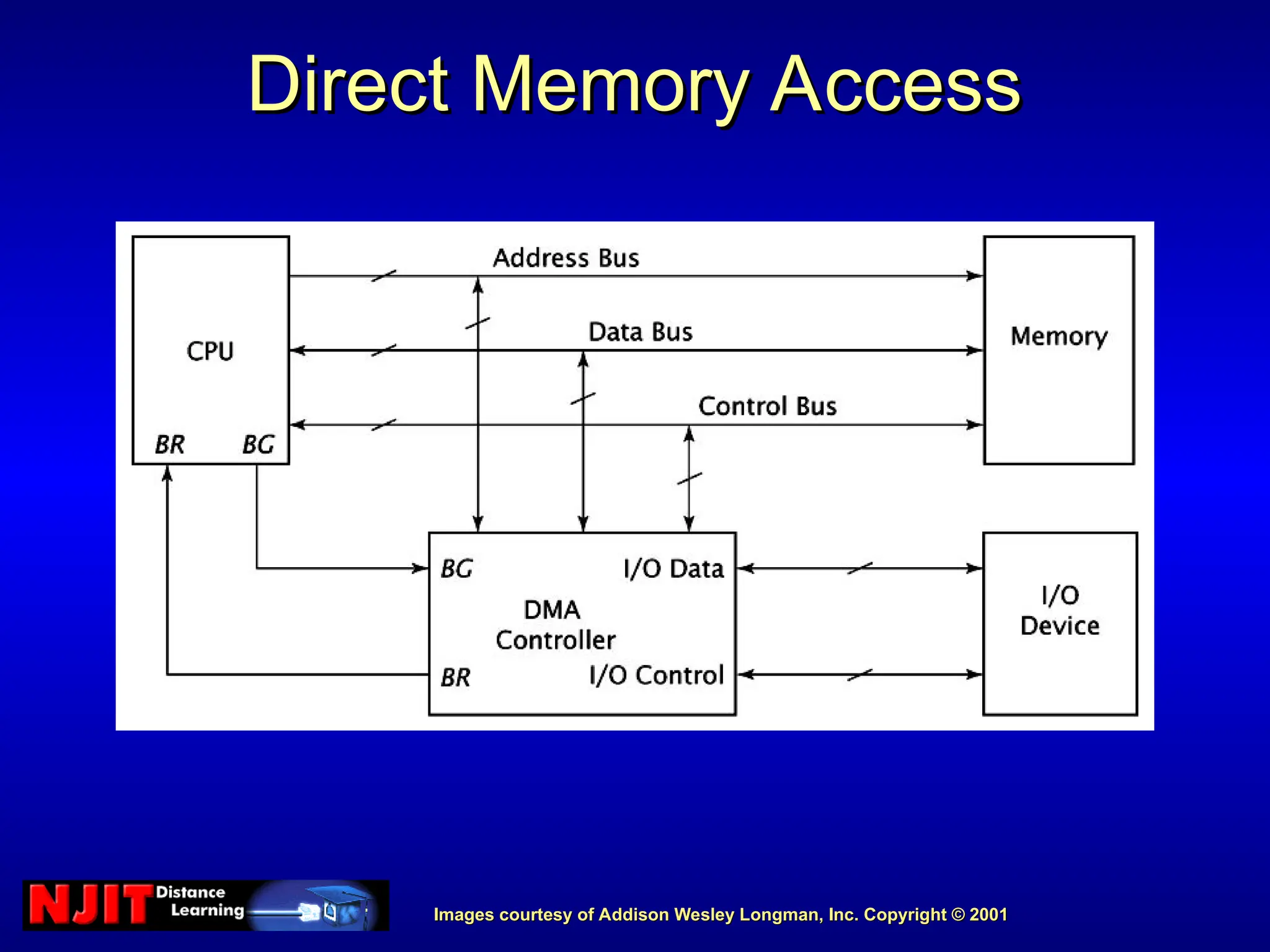

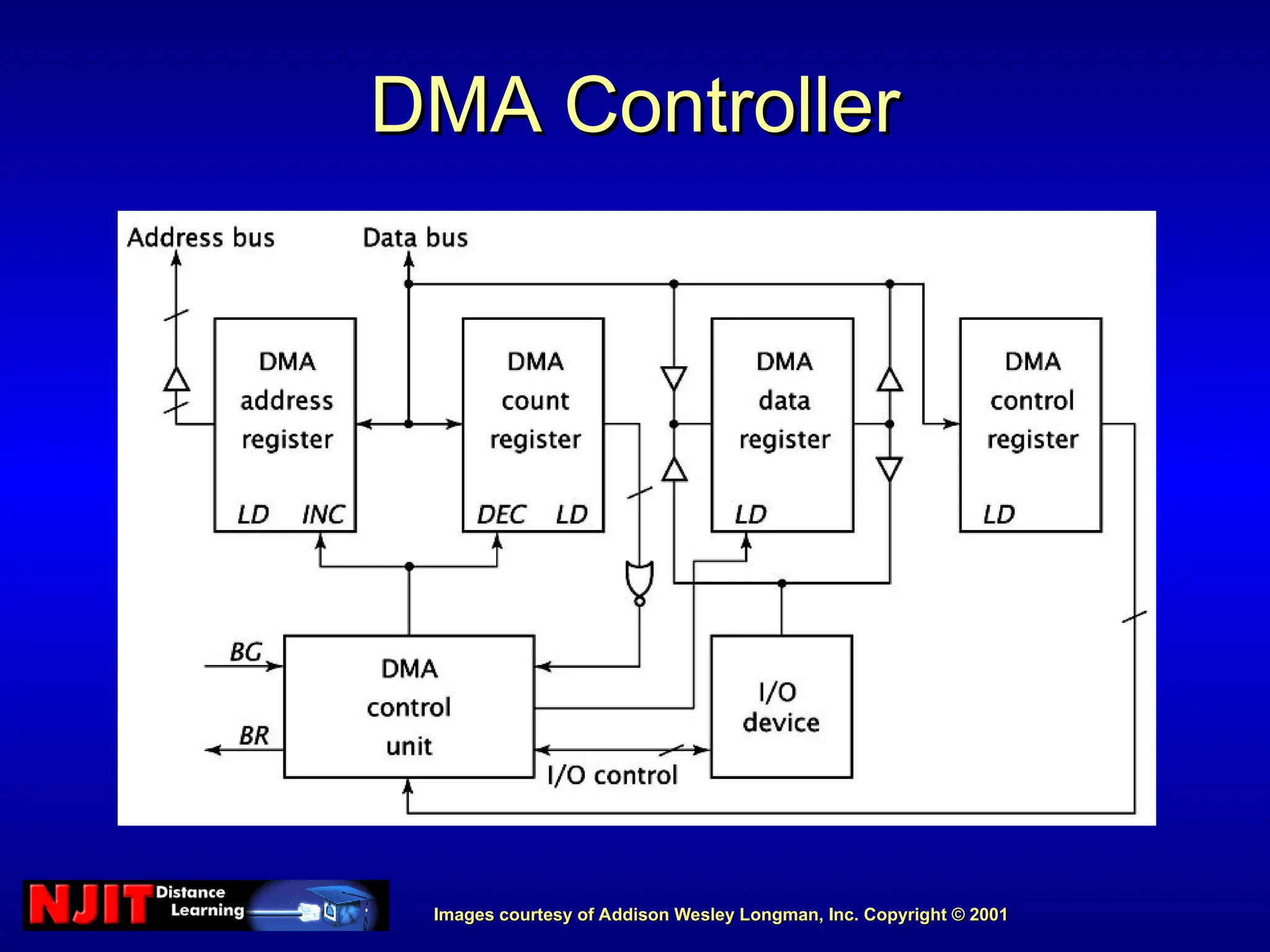

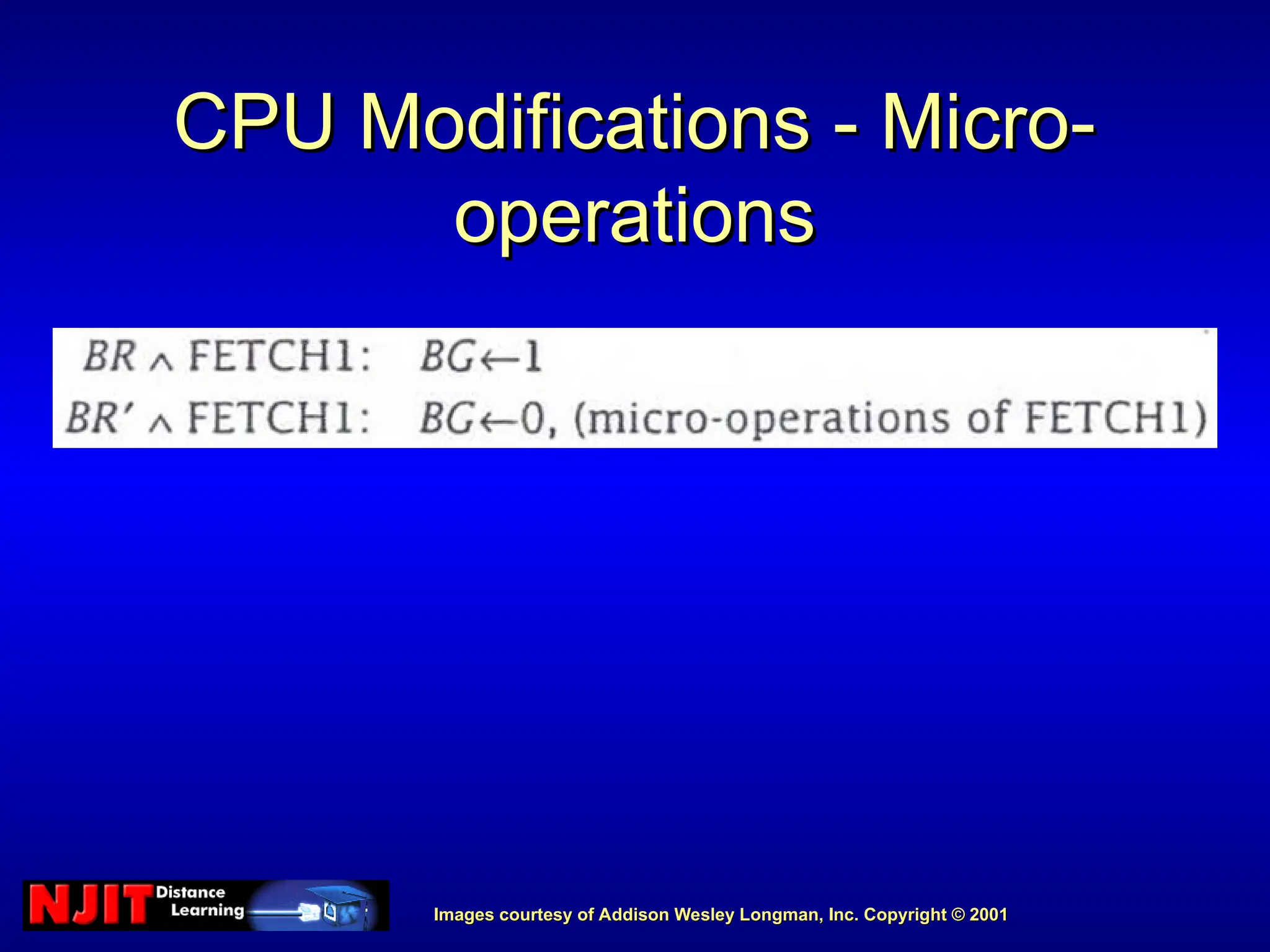

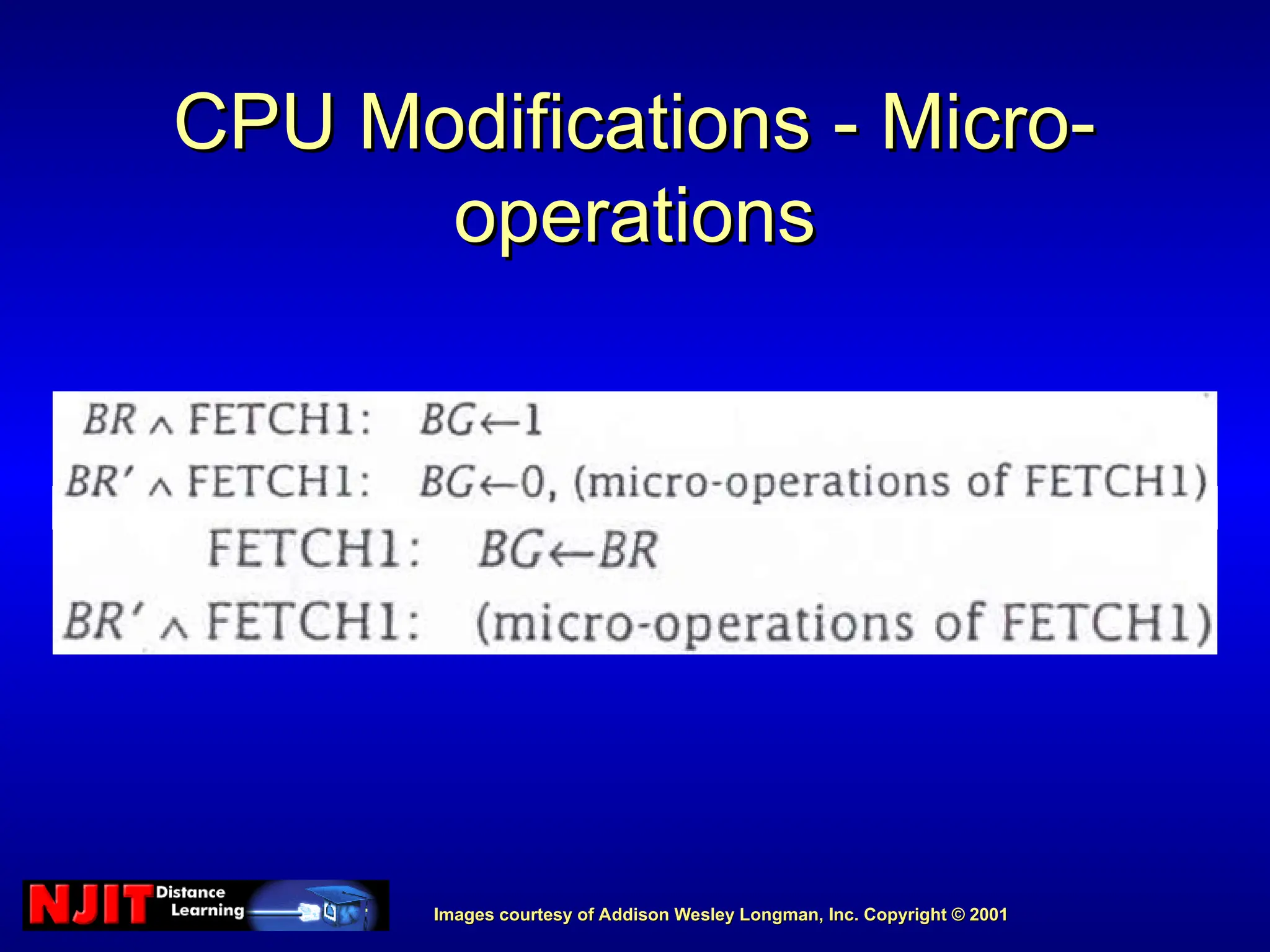

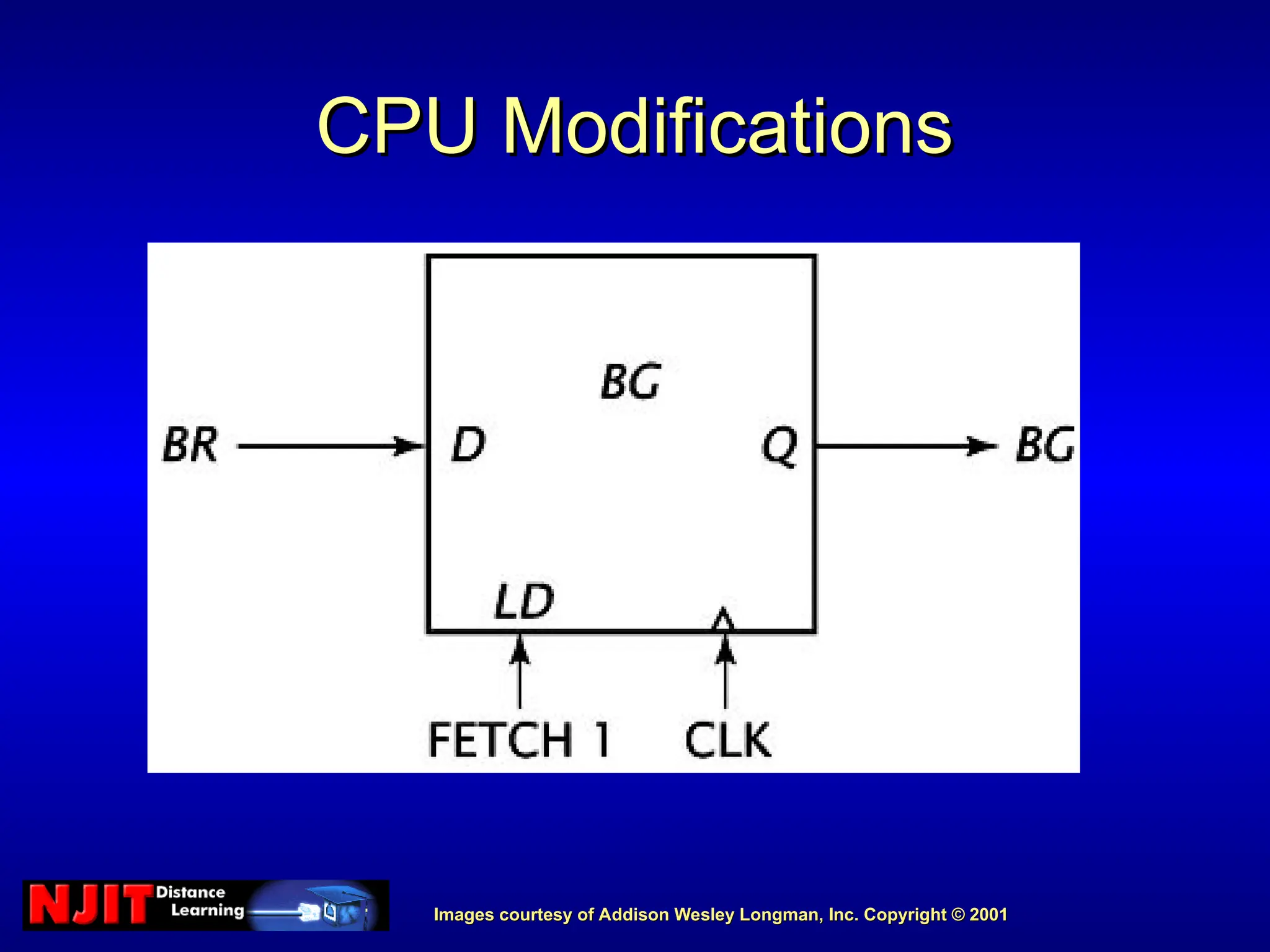

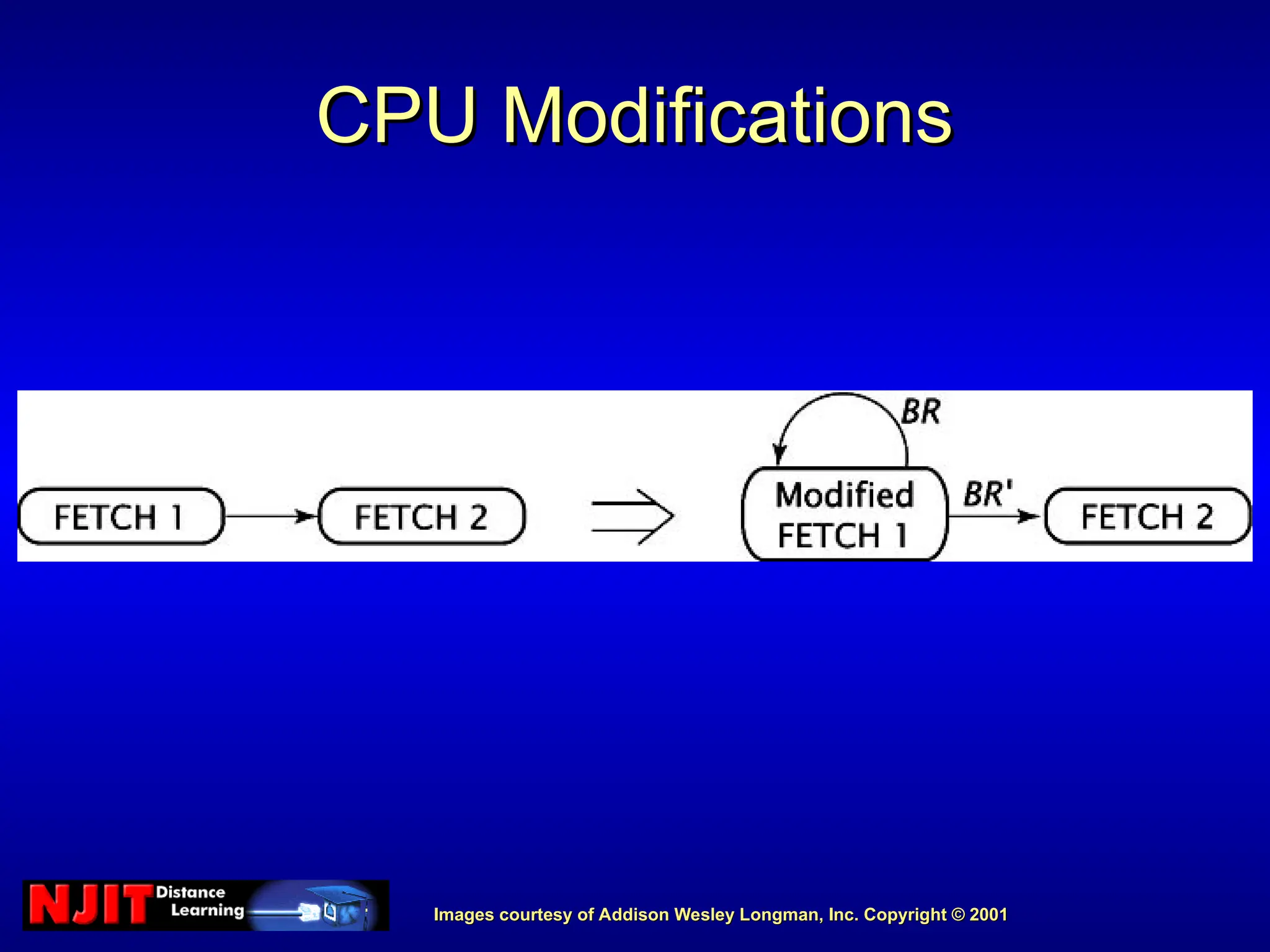

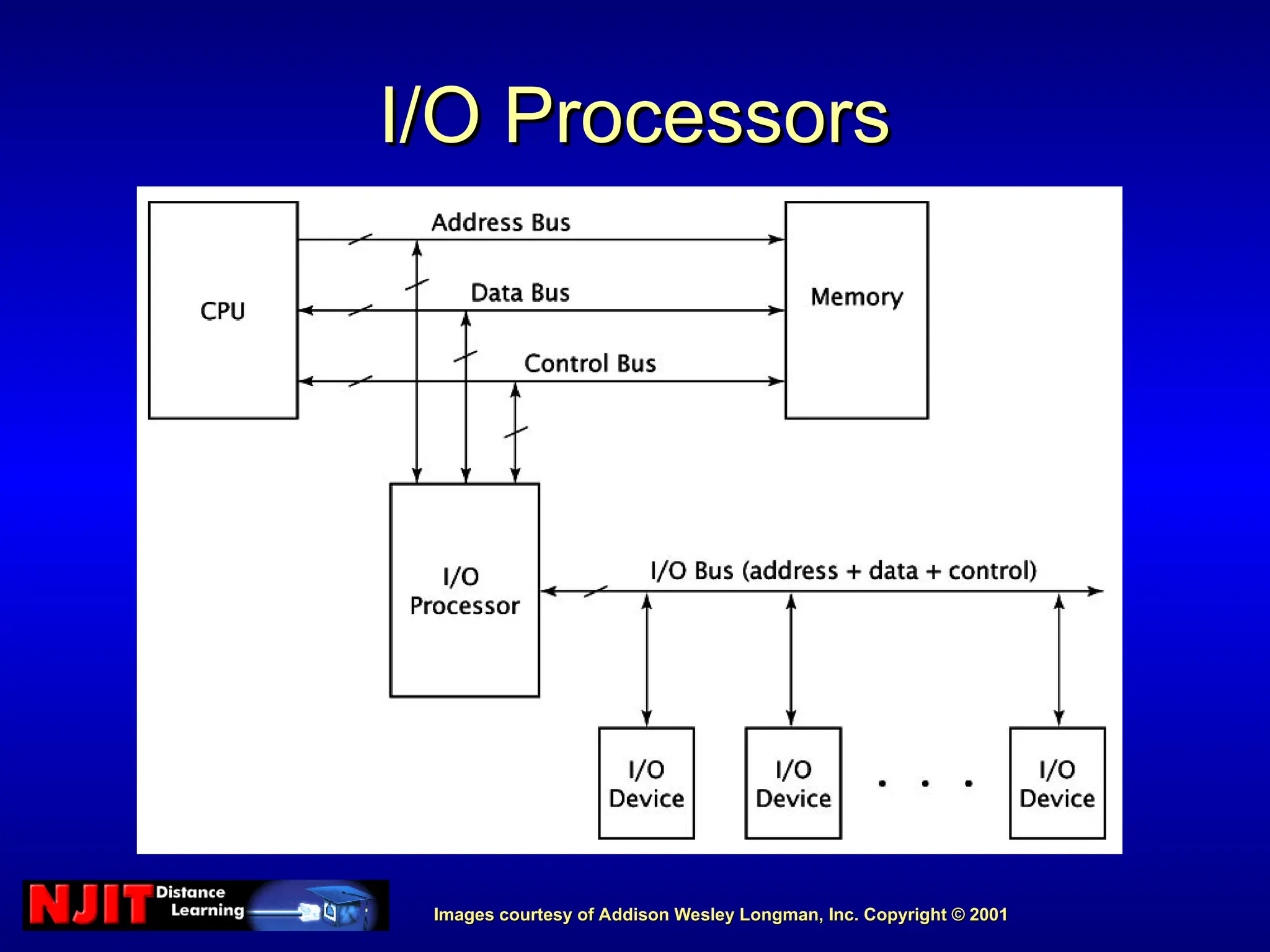

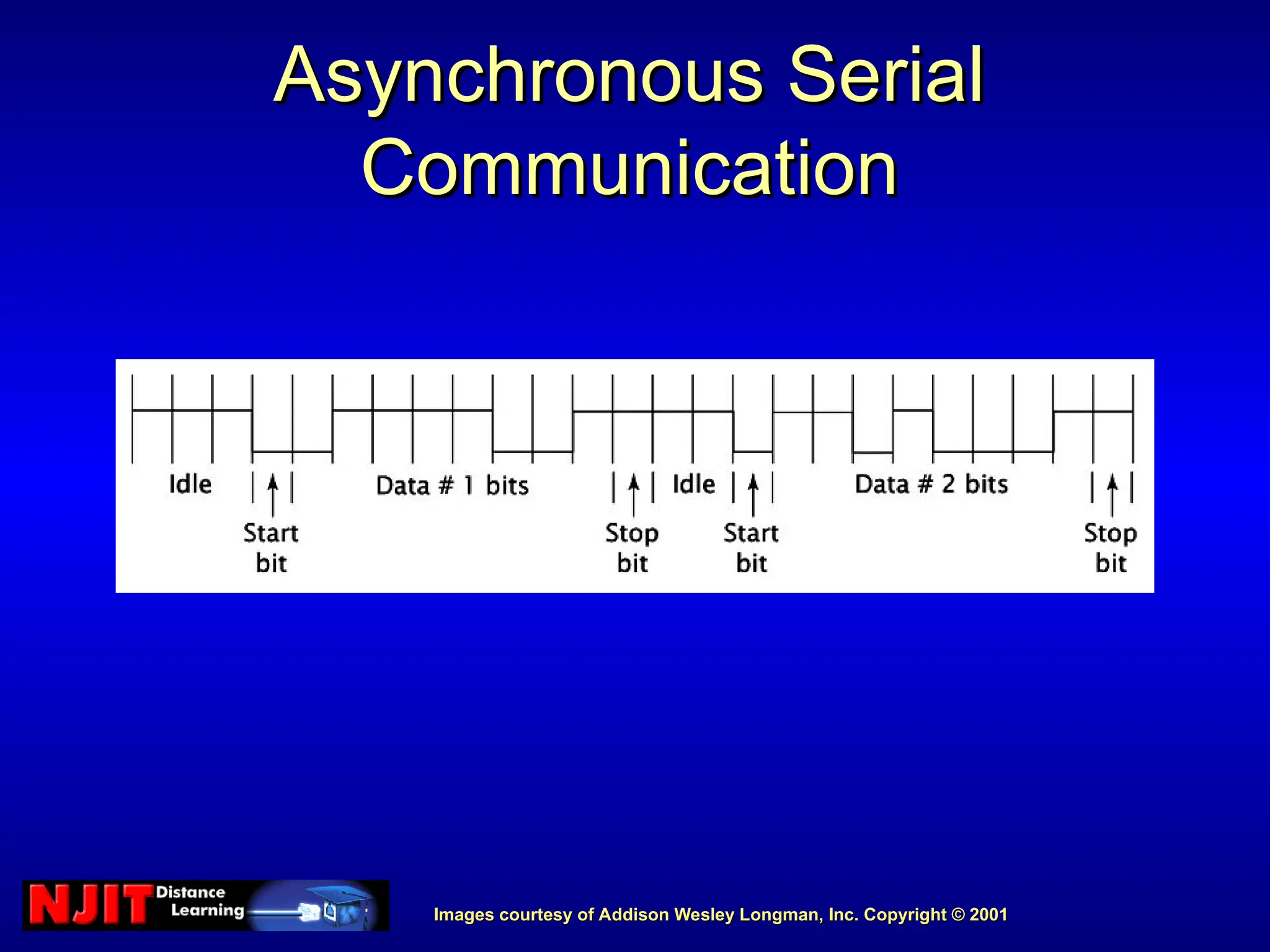

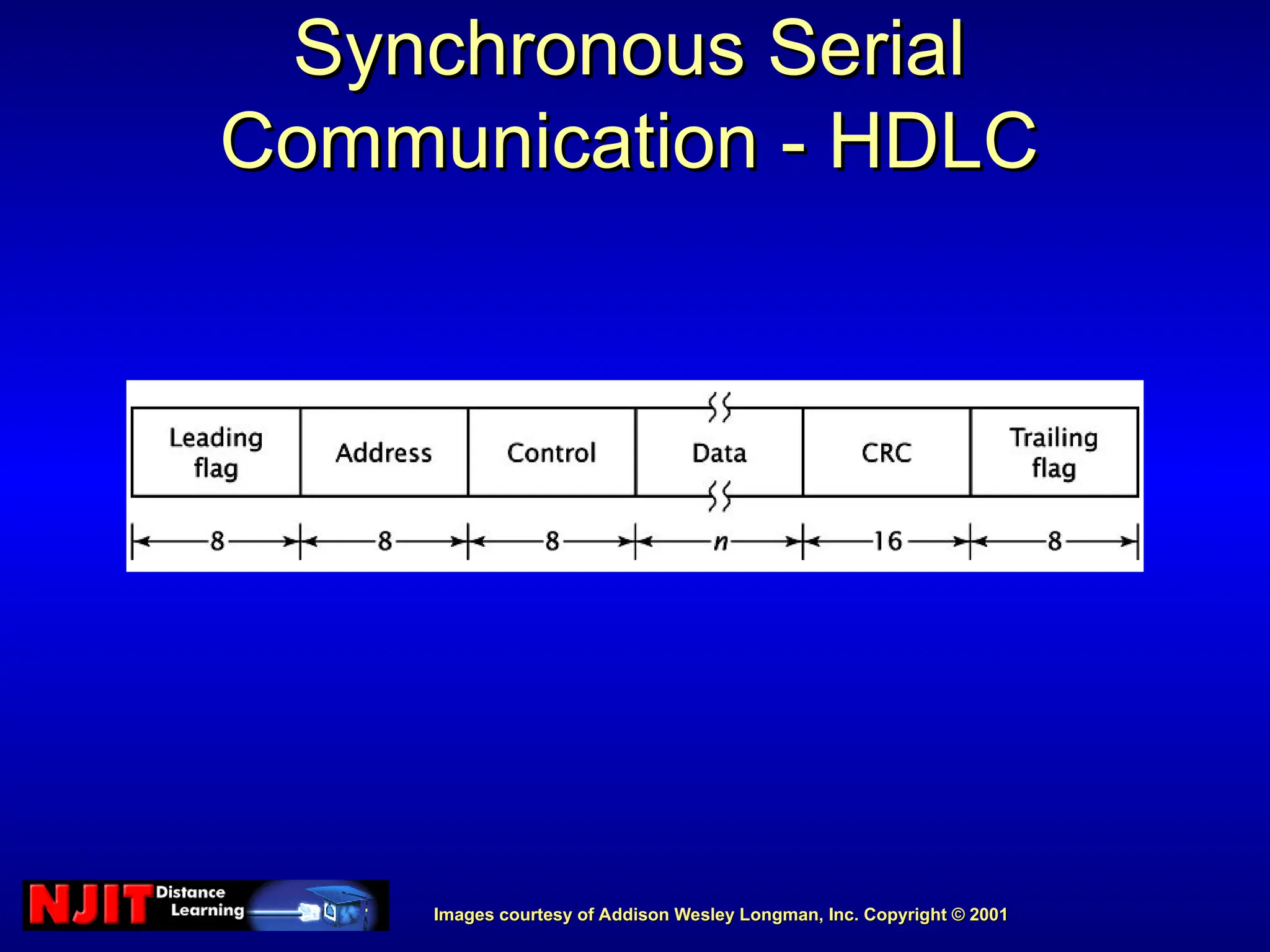

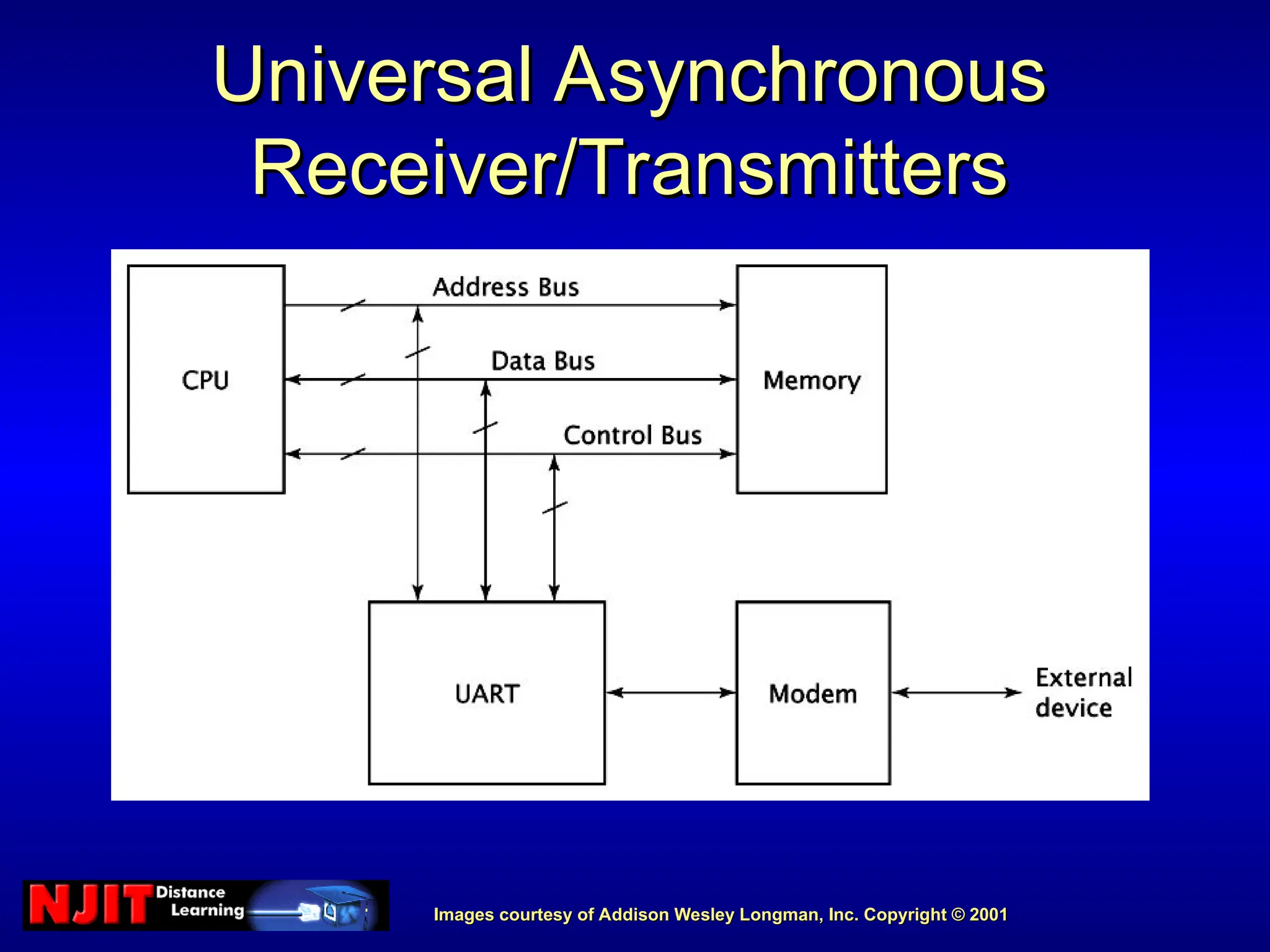

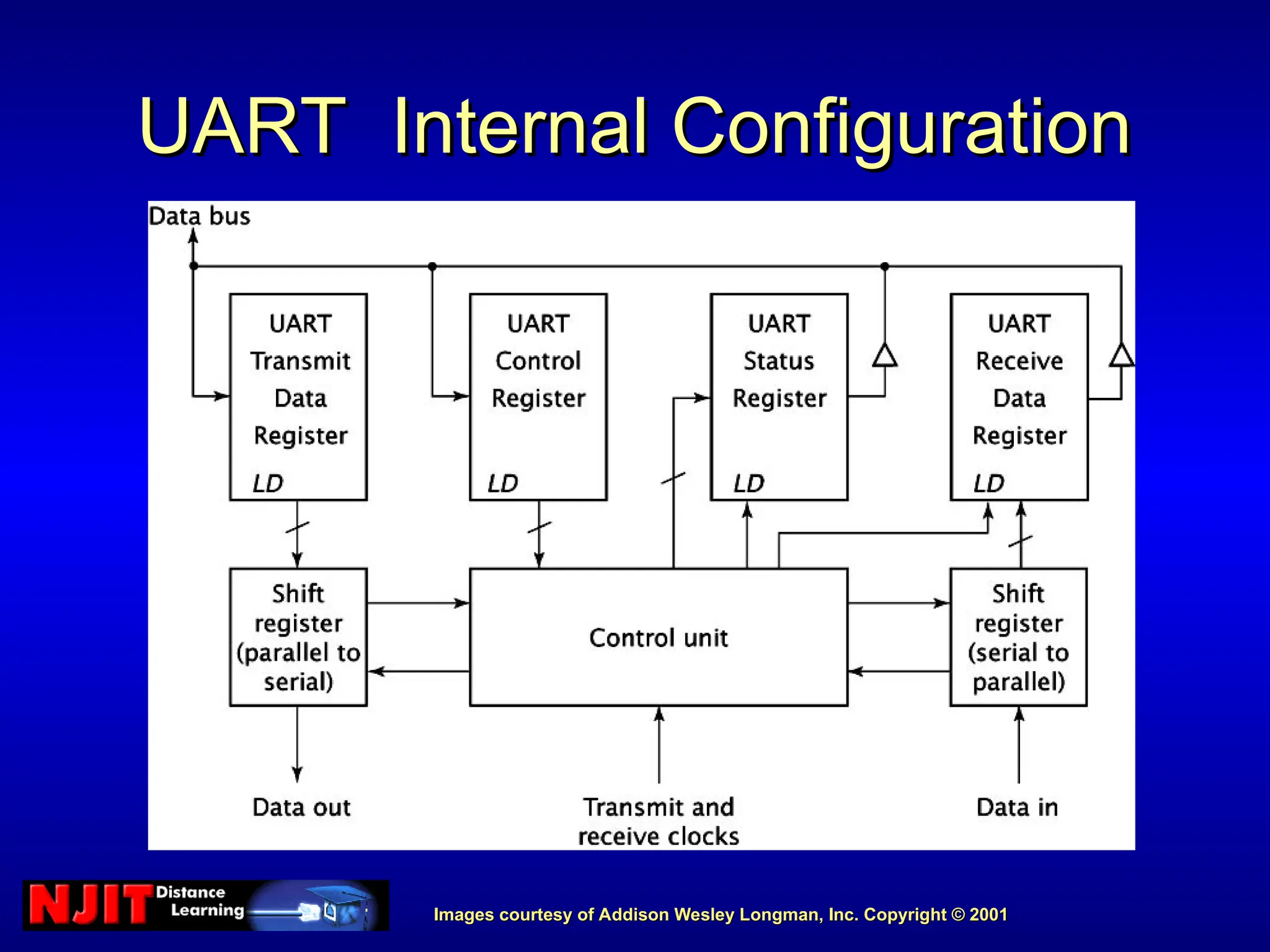

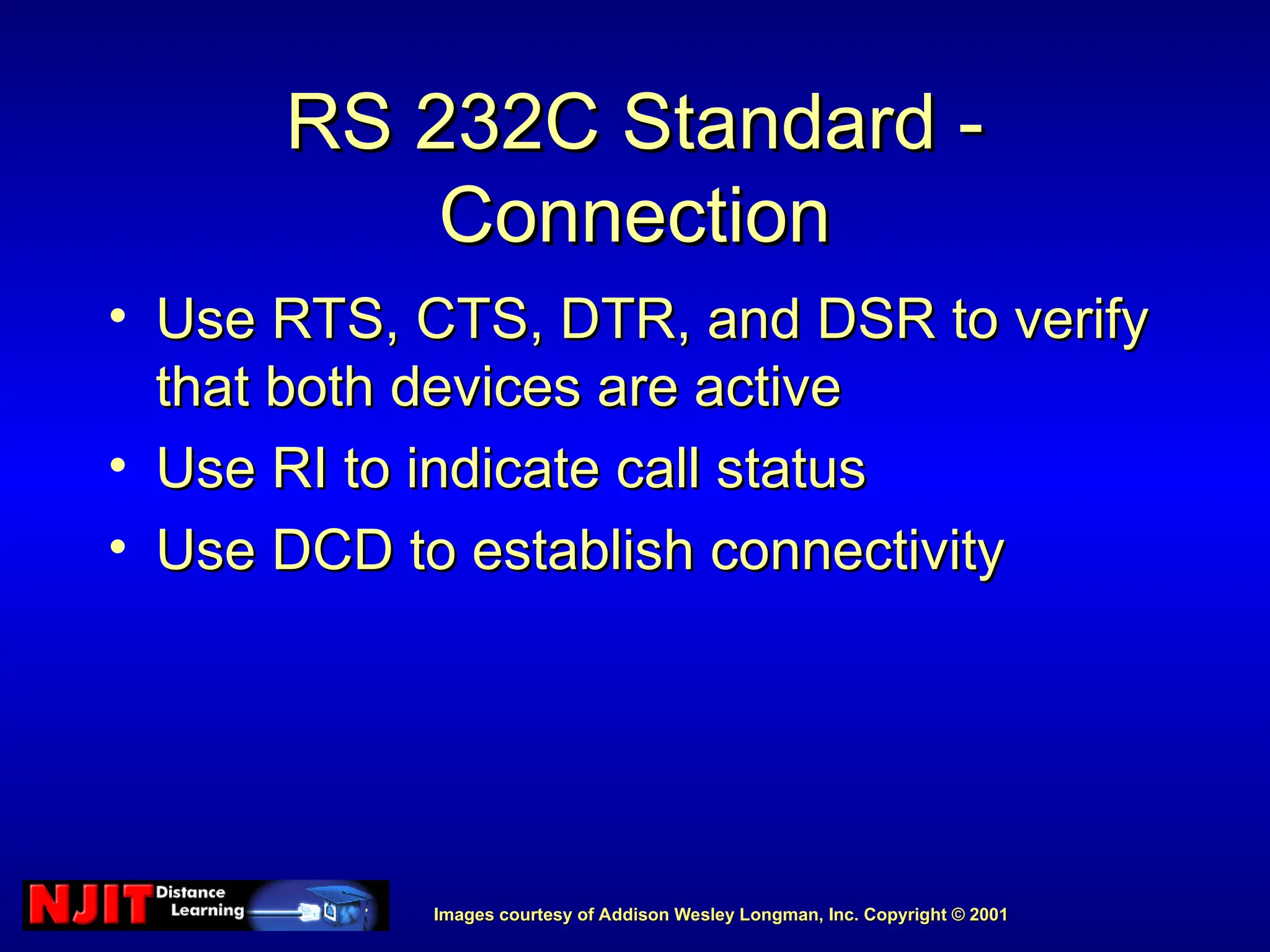

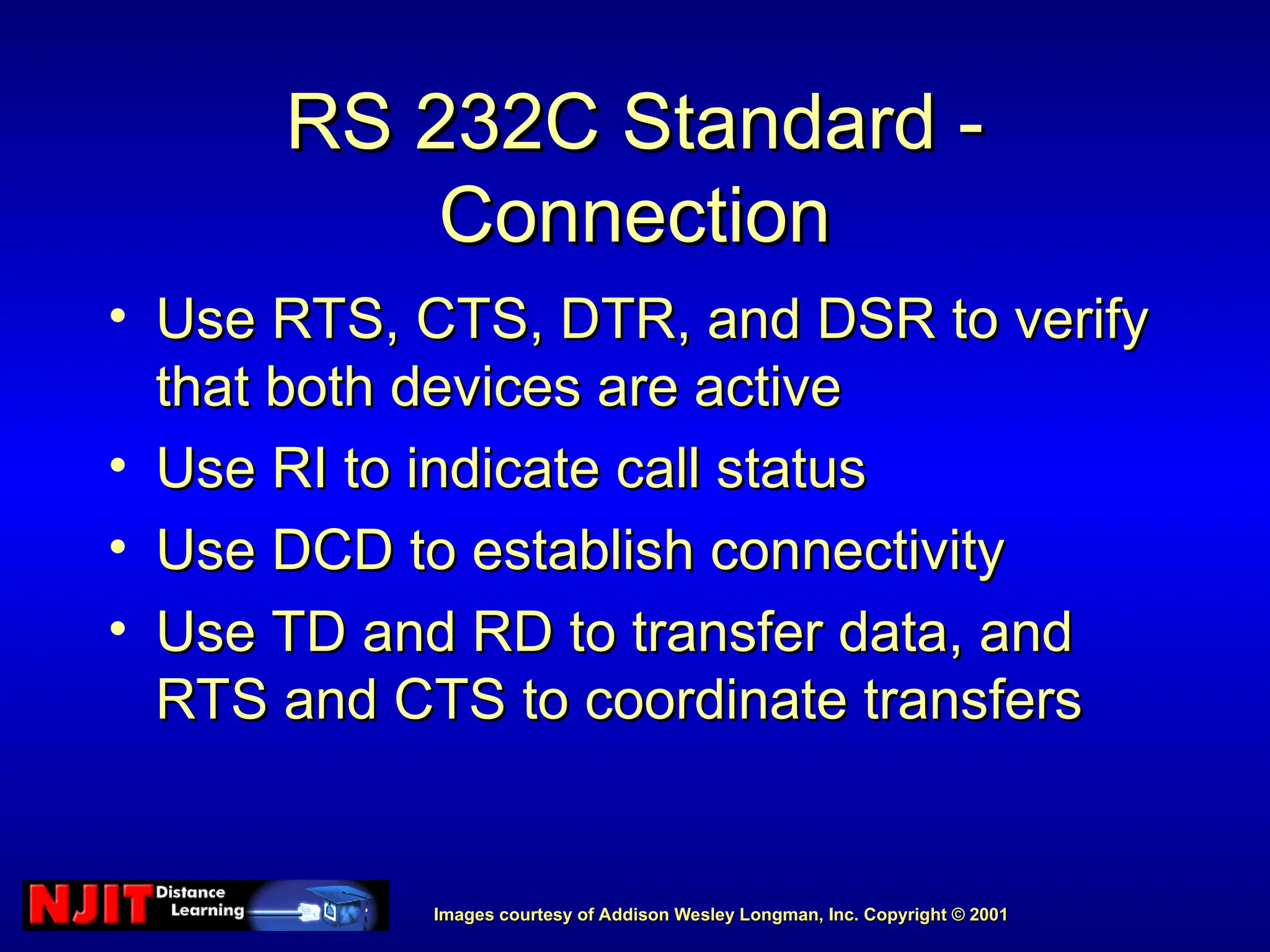

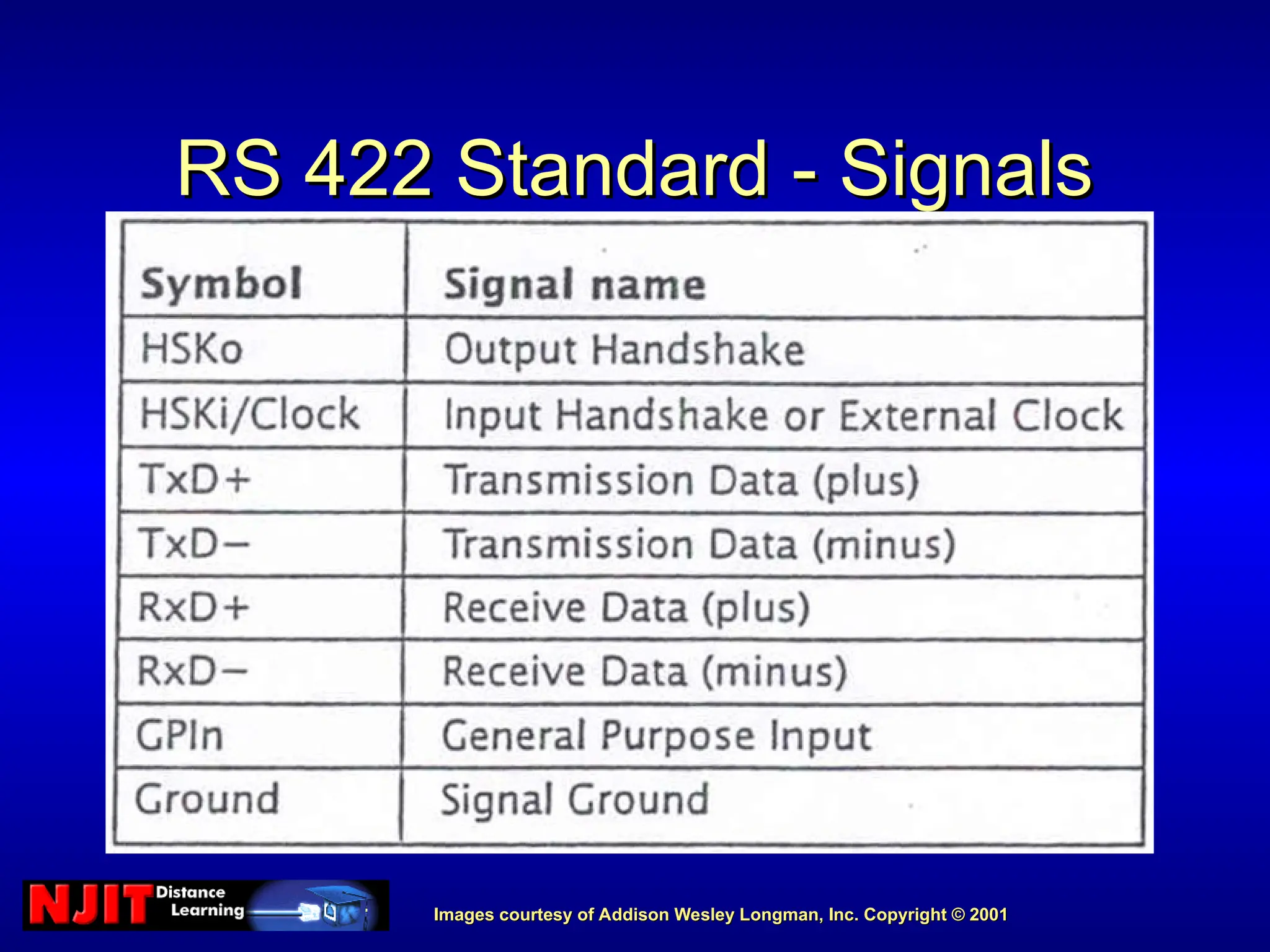

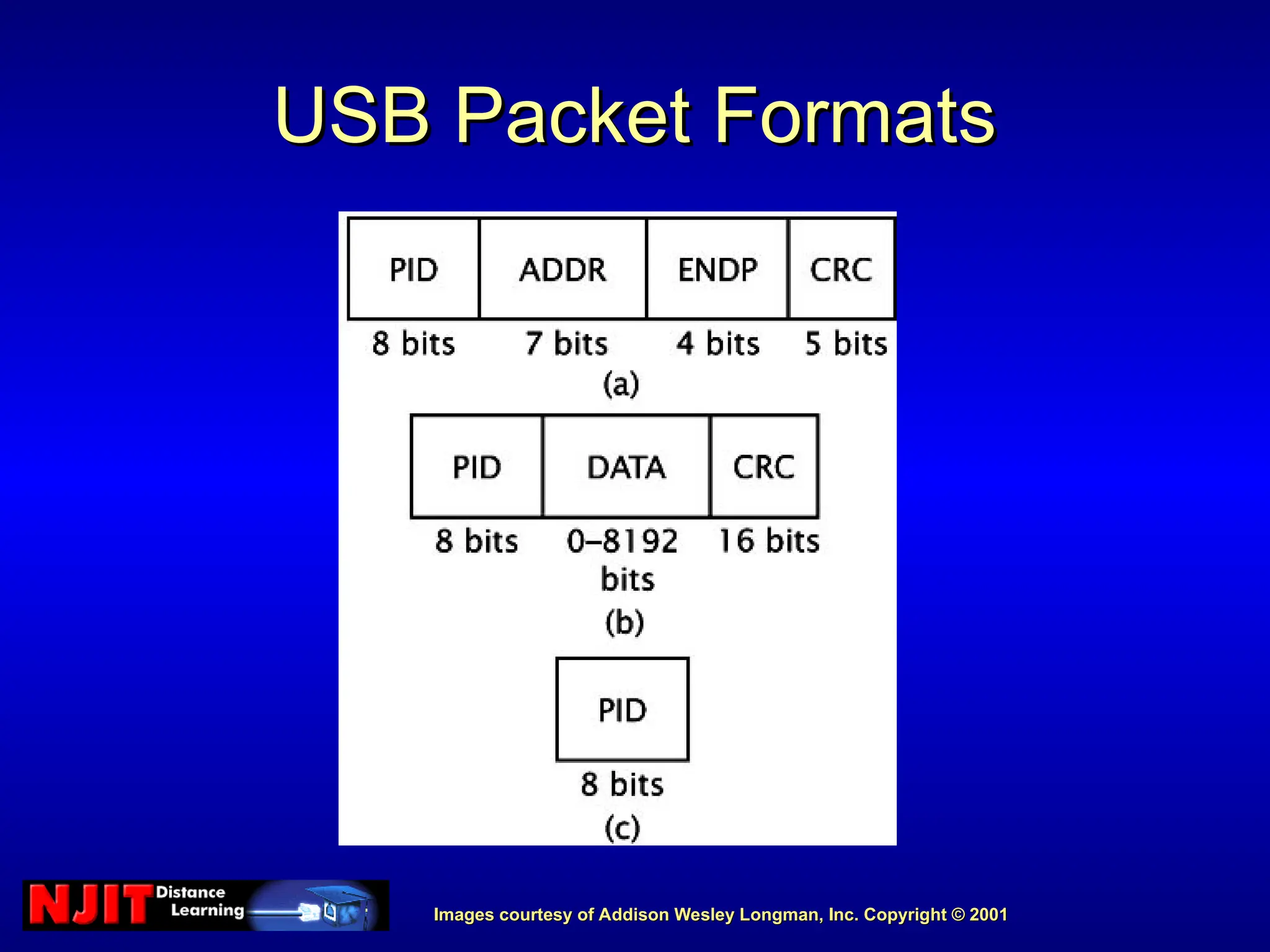

The document discusses input/output organization, including topics such as asynchronous data transfers, programmed I/O, interrupts, and direct memory access. It covers CPU modifications, control unit changes, processing of interrupts, and the functioning of I/O processors. The document also details serial communication standards, data transfer modes, and components like UART and RS-232C for synchronous and asynchronous communication.