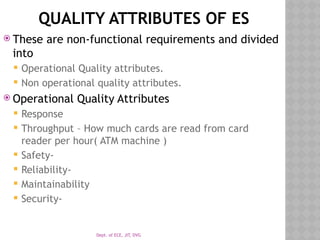

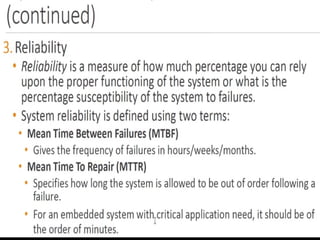

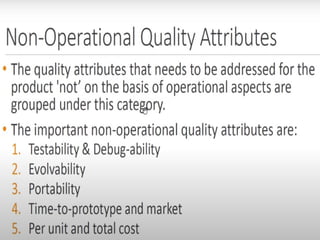

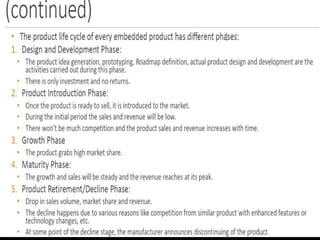

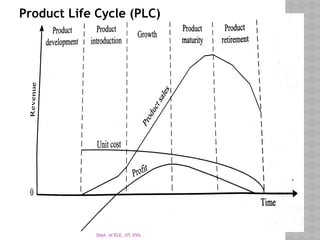

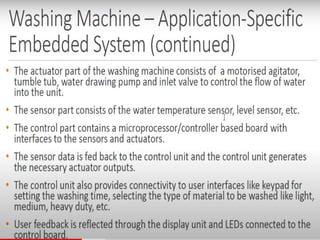

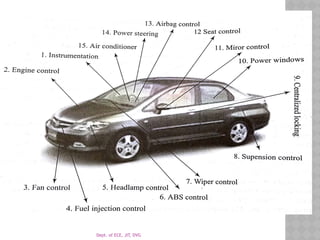

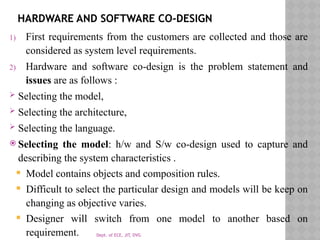

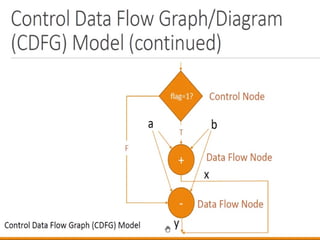

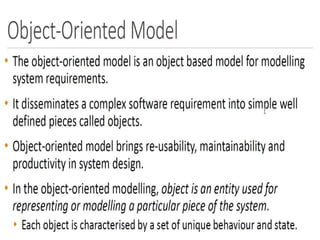

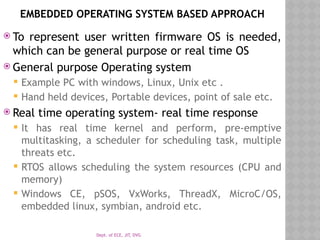

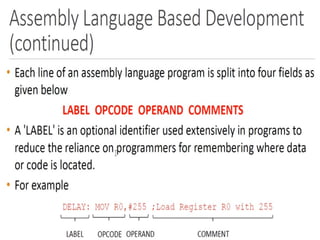

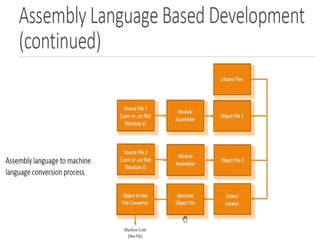

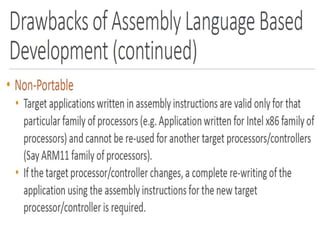

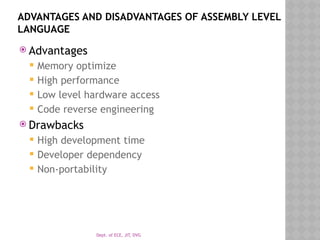

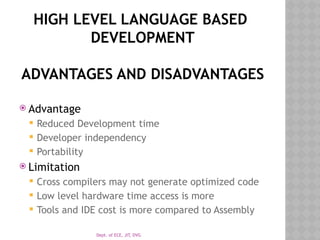

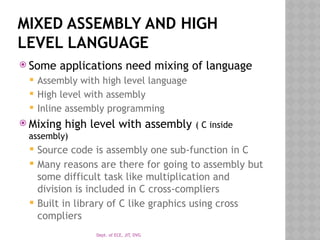

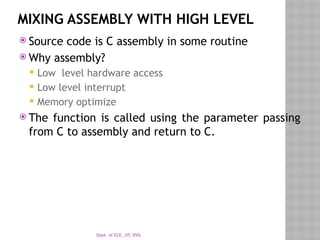

The document discusses embedded system design concepts, highlighting the unique characteristics and quality attributes of embedded systems, which include being application-specific, reactive, real-time, and capable of operating in harsh environments. It further elaborates on the importance of hardware-software co-design and various architectural models used in development. Additionally, it touches on the life cycle of products, automotive embedded systems, and the pros and cons of different programming approaches in firmware design.