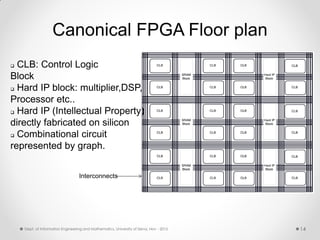

The document provides an overview of Field Programmable Gate Arrays (FPGAs), including their architecture, historical development, types, and practical applications. Key components such as Configurable Logic Blocks (CLBs) and Look-Up Tables (LUTs) are explained, along with the advantages of FPGAs like reconfigurability and improved performance per watt. The programming languages used for FPGAs, particularly Verilog and VHDL, are briefly discussed, emphasizing their importance in hardware description and circuit design.

![But.. why Use FPGA?

Application needs tailored

HW

No need to over-provision

(Like custom ASIC)

Don’t worry about mistakes

it is “Reconfigurable”

Make chip development

faster.

FPGAs provide significantly more hardware acceleration performance/watt

[1] Image Source: Xilinx SDAccel Developer Zone. http://www.xilinx.com/products/design-tools/ software-zone/sdaccel.html.

“FPGA-based accelerators can achieve up to 25x better performance per

watt and 50-75x latency improvement compared to CPU/GPU

implementations while also providing excellent I/O integration (PCI, DDR4

SDRAM interfaces, high-speed Ethernet, etc.)..”[1]

Dept. of Information Engineering and Mathematics. University of Siena. Nov - 2015 9](https://image.slidesharecdn.com/fpga12octslideshare-151113170849-lva1-app6891/85/FPGA-In-a-Nutshell-7-320.jpg)

![But.. what about Weaknesses

For a specific circuit, relative to

a custom ASIC, FPGAs use

more area, power and slower

FPGA resources are of a fixed

size and have limited flexibility

options.

But you may not have the

option for “reconfiguration”

Metric FPGAvsASIC[1] FPGAvsASIC[2]

Area 30-40X 2-20X

Delay 3-4X 1.7-3X

Dy.

Power

12X

Static

Power

5-90X 2-5X

[1] Compares Altera Stratix-II to ST Microelectronics standard cells (90nm

technology) [Kuon et. al. (TCAD`07)].

[2] Altera Corp 2006.

Dept. of Information Engineering and Mathematics. University of Siena. Nov - 2015 11](https://image.slidesharecdn.com/fpga12octslideshare-151113170849-lva1-app6891/85/FPGA-In-a-Nutshell-9-320.jpg)

![Verilog

Data Types:

Basic type: Bit vector Values: 0, 1, X (don't care), Z (high

impedance)

Example: Binary: 4'b11_10, Hex: 16'h034f, Decimal:

32'd270

Use wire to connect components: Single wire

Example: wire my_wire

Array of wires : Example: wire[7:0] my_wire)

Reg for procedural assignments:

Example reg[3:0] accum; // 4 bit “reg”)

reg is not necessarily a hardware register

Dept. of Information Engineering and Mathematics. University of Siena. Nov - 2015 26](https://image.slidesharecdn.com/fpga12octslideshare-151113170849-lva1-app6891/85/FPGA-In-a-Nutshell-24-320.jpg)

![HLS: Key Aspect

Scheduling: Defines the HW’s finite state machine

How to assign the computations of a program into the hardware

time steps?

Or Which operations can be scheduled in the same time step?

Or Which operations are dependent on others?

SDC[1]: System of Difference Constraints : formulate scheduling

as a mathematical optimization problem (linear program (LP)).

Variables: For each operation(op) to schedule, create a

variable(var). var will hold the cycle # in which each op is

scheduled.

1. Cong, Zhang, “An efficient and versatile scheduling algorithm based on SDC formulation”. DAC 2006: 433-438.

Dept. of Information Engineering and Mathematics. University of Siena. Nov - 2015 39](https://image.slidesharecdn.com/fpga12octslideshare-151113170849-lva1-app6891/85/FPGA-In-a-Nutshell-37-320.jpg)

![ Constraints:

Dependency Constraints : The subtract can only happen after

the add and shift,

Clock Period Constraints : For each chain of dependant

operations in DFG, find the path delayD.

Resource Constraints: Allow up to 2 load/store operations in a

cycle

Binding: e.g. Bind the following scheduled operations.

Loop Pipelining : Overlap execution of adjacent loop iterations.

Can be combined with loop unrolling

for (int i = 0; i < N; i++) {

a[i] = b[i] + c[i]

}

Each iteration requires:

• 2 loads from memory

• 1 store

• No dependencies between iterations

HLS: Key Aspect

Dept. of Information Engineering and Mathematics. University of Siena. Nov - 2015 40](https://image.slidesharecdn.com/fpga12octslideshare-151113170849-lva1-app6891/85/FPGA-In-a-Nutshell-38-320.jpg)