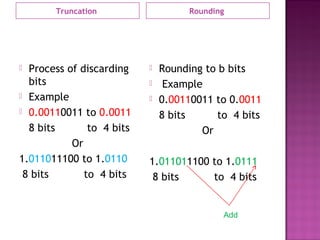

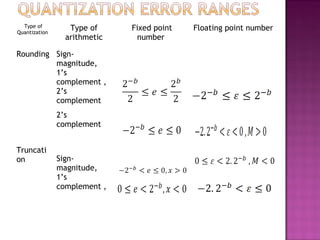

1. DSP algorithms are realized using special or general purpose digital hardware where numbers are stored using a finite number of bits. Quantization errors are introduced during truncation or rounding of coefficients and numbers.

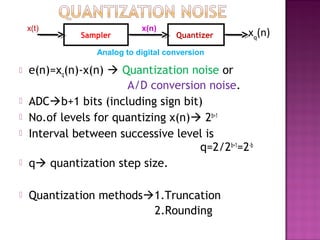

2. There are three main types of quantization errors: input quantization error from A/D conversion, product quantization error from multiplier outputs being rounded to a finite number of bits, and coefficient quantization error that deviates the frequency response from the desired response.

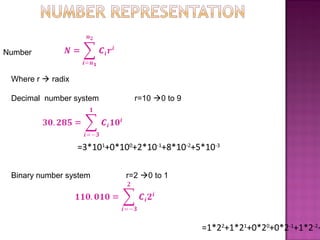

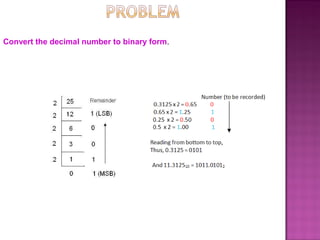

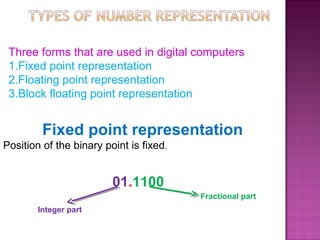

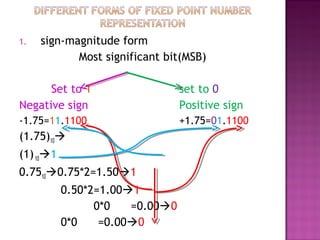

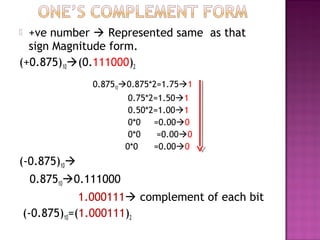

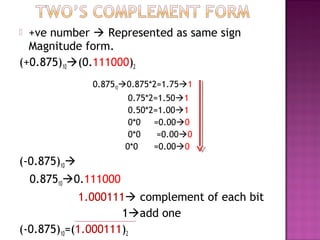

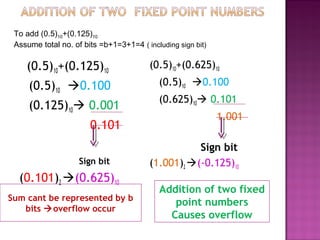

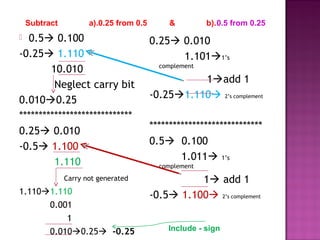

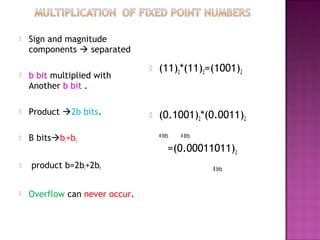

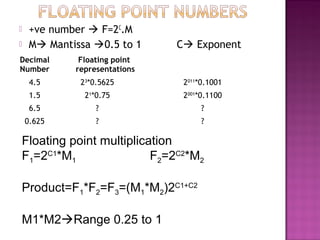

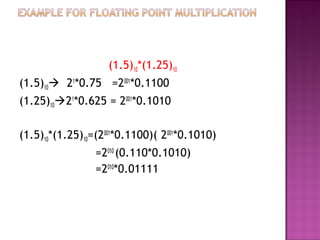

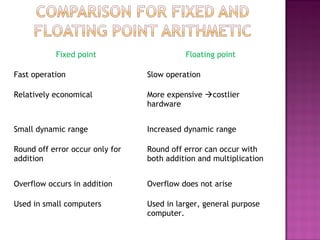

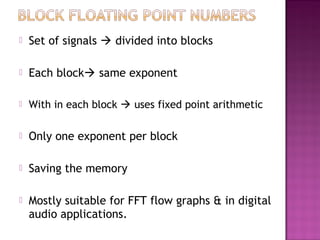

3. Fixed point and floating point representations are used to represent numbers in digital computers, with fixed point using a fixed binary point and floating point having a variable binary point to increase dynamic range at the cost of more complex hardware.