This document contains 5 sample question papers from previous years' examinations for a Digital Electronics Circuit course. Each paper contains 4-5 questions testing various concepts in digital logic design including:

- Boolean algebra simplification and logic minimization techniques

- Code conversions (binary to gray, decimal to BCD)

- Combinational logic circuits (multiplexers, decoders, adders)

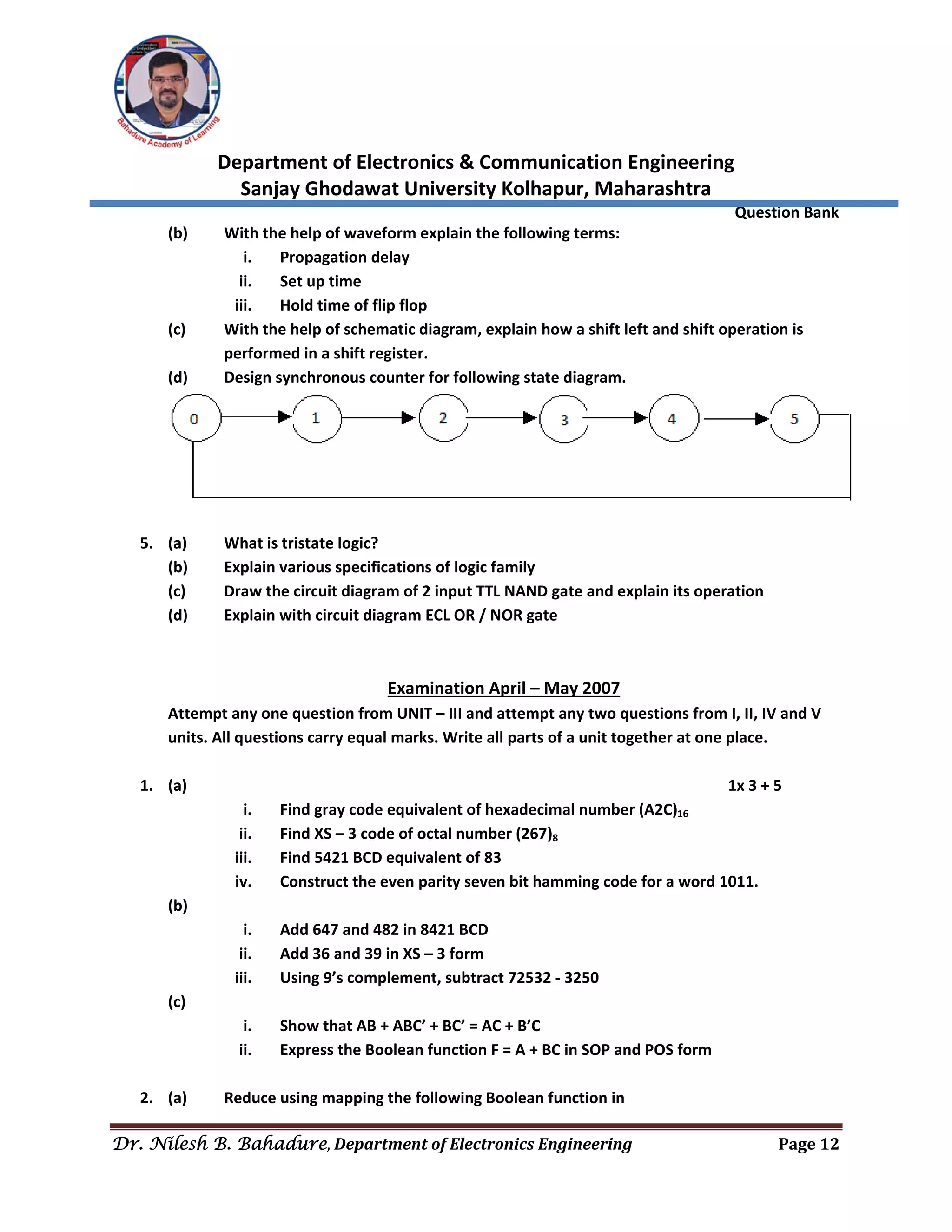

- Sequential logic circuits (latches, flip-flops, counters)

- Logic families and their characteristics (TTL, CMOS, ECL)