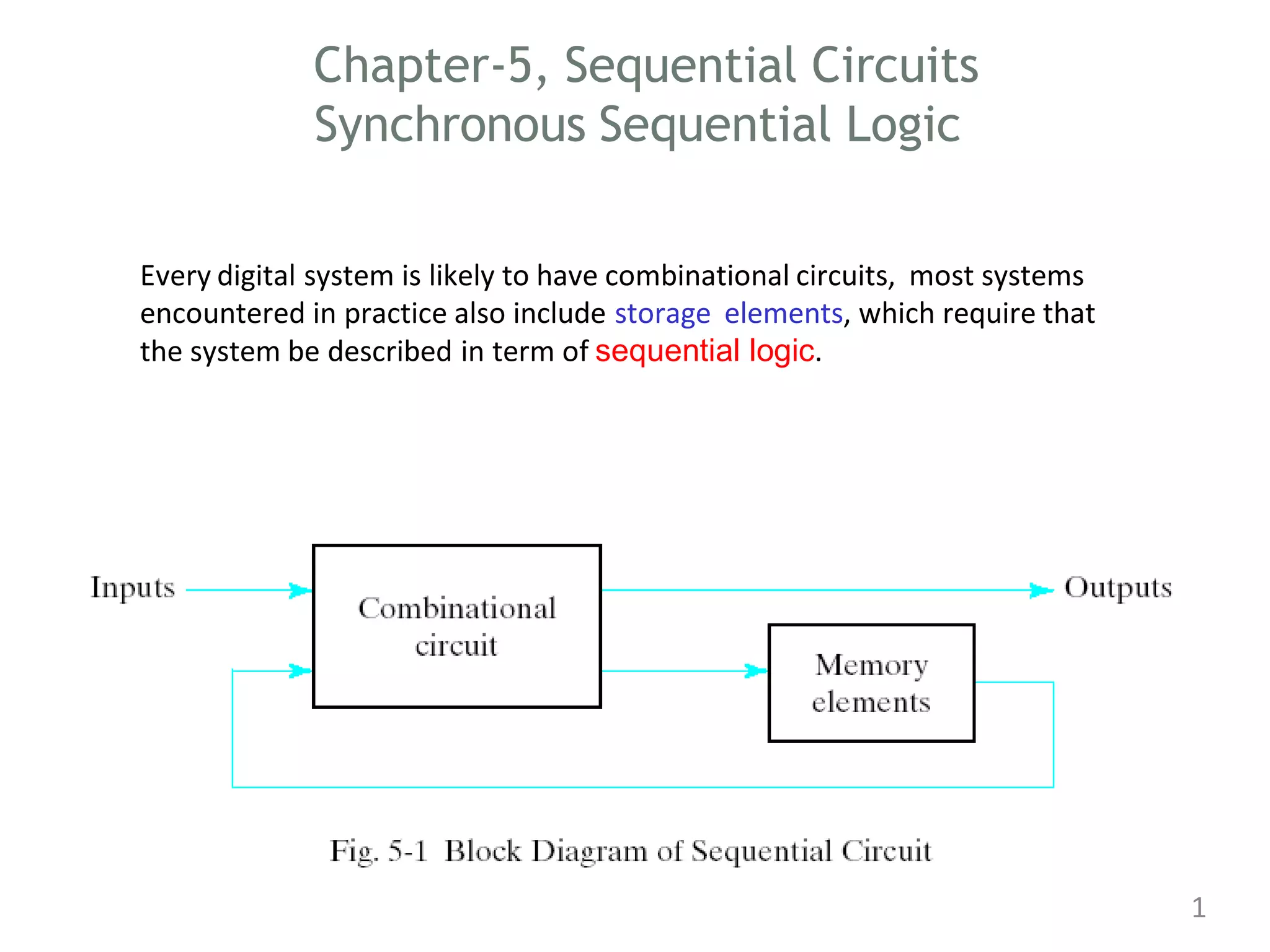

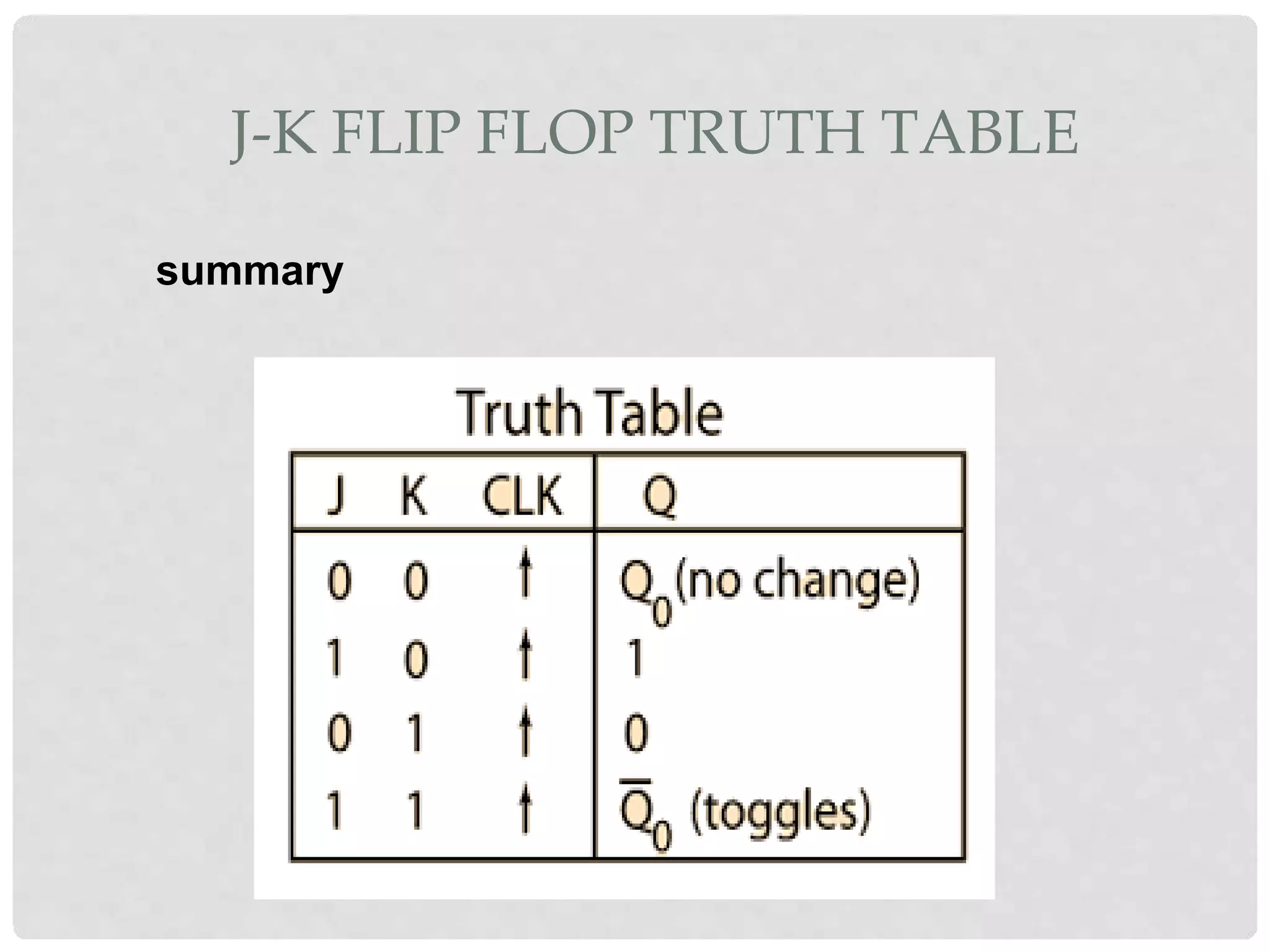

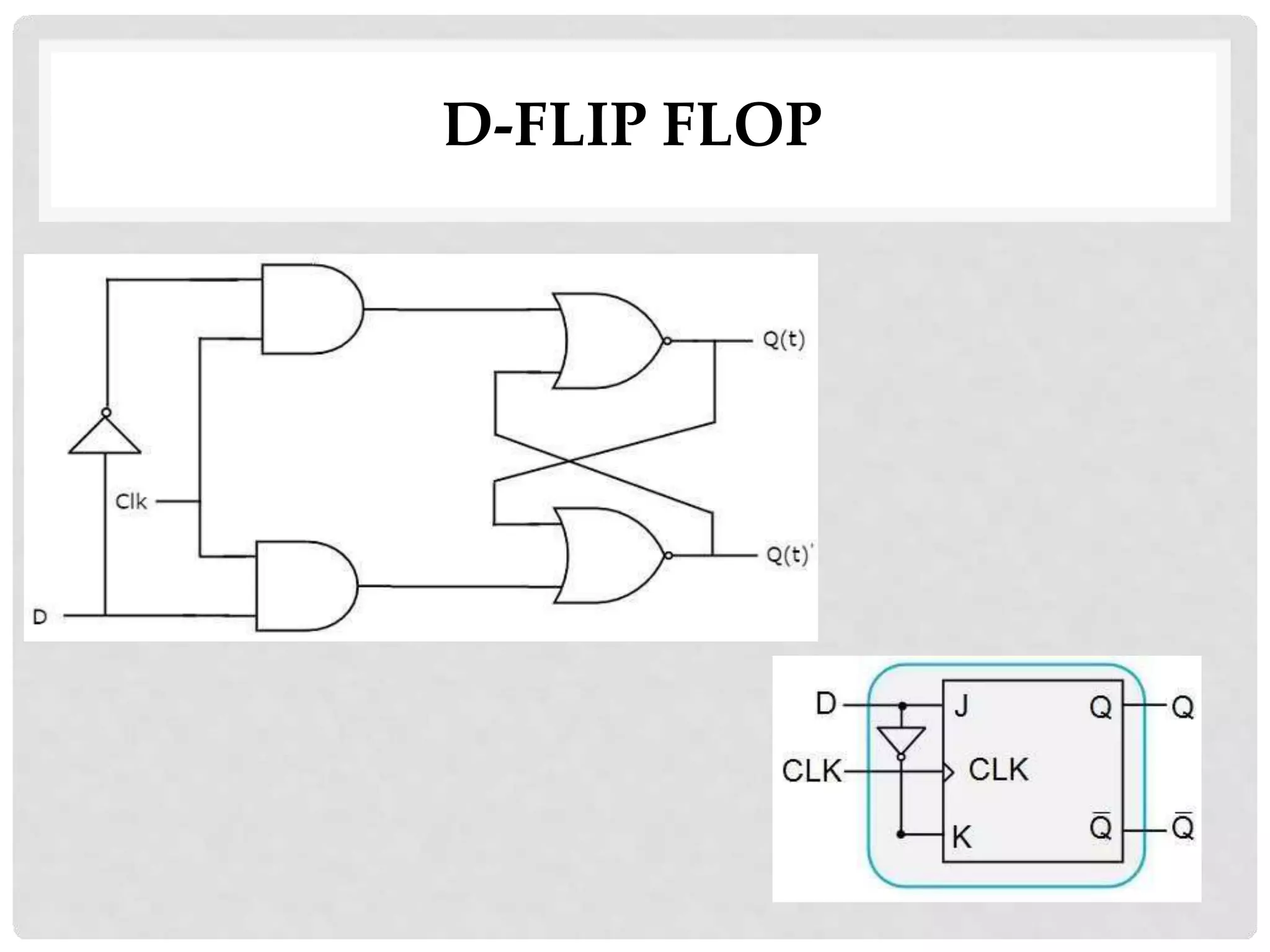

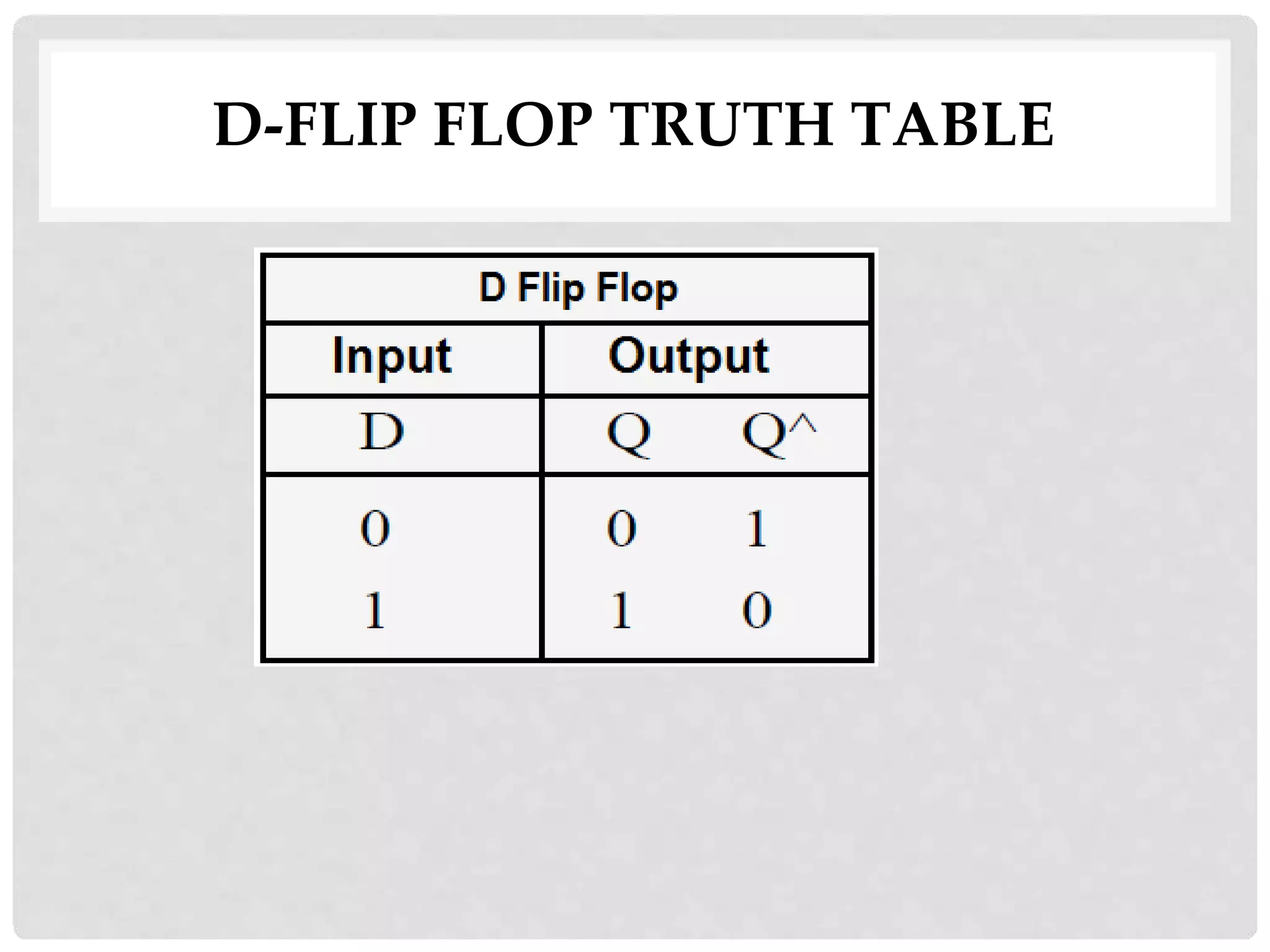

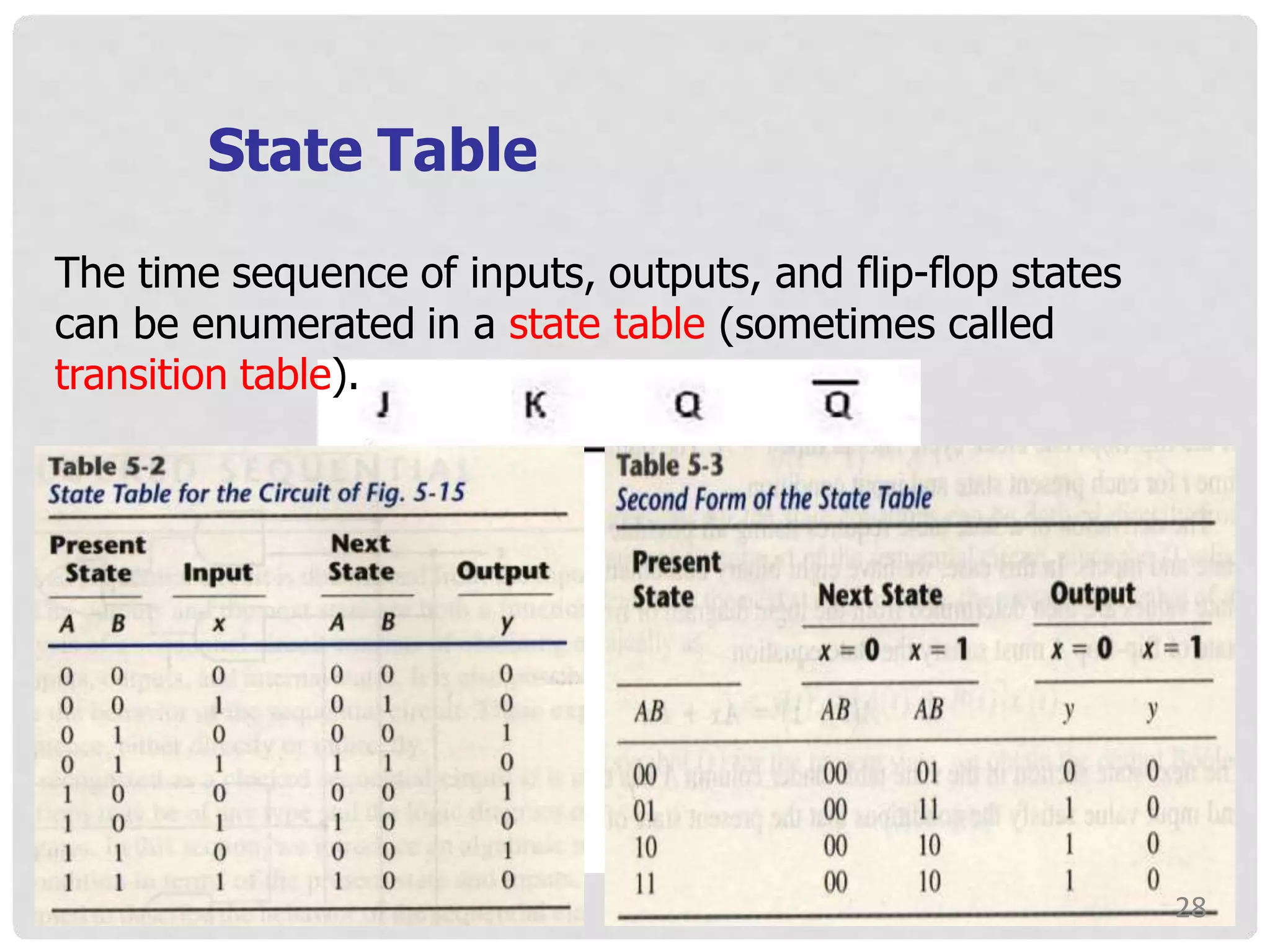

The document discusses sequential logic and flip-flops. It begins by defining sequential logic and introducing flip-flops. It then discusses different types of flip-flops including SR, JK, D, and T flip-flops. It describes their operation, truth tables, and how they are constructed using logic gates. The document also covers triggering methods for flip-flops including master-slave and edge triggering. Finally, it discusses modeling sequential circuits using state equations, state tables, and state diagrams.