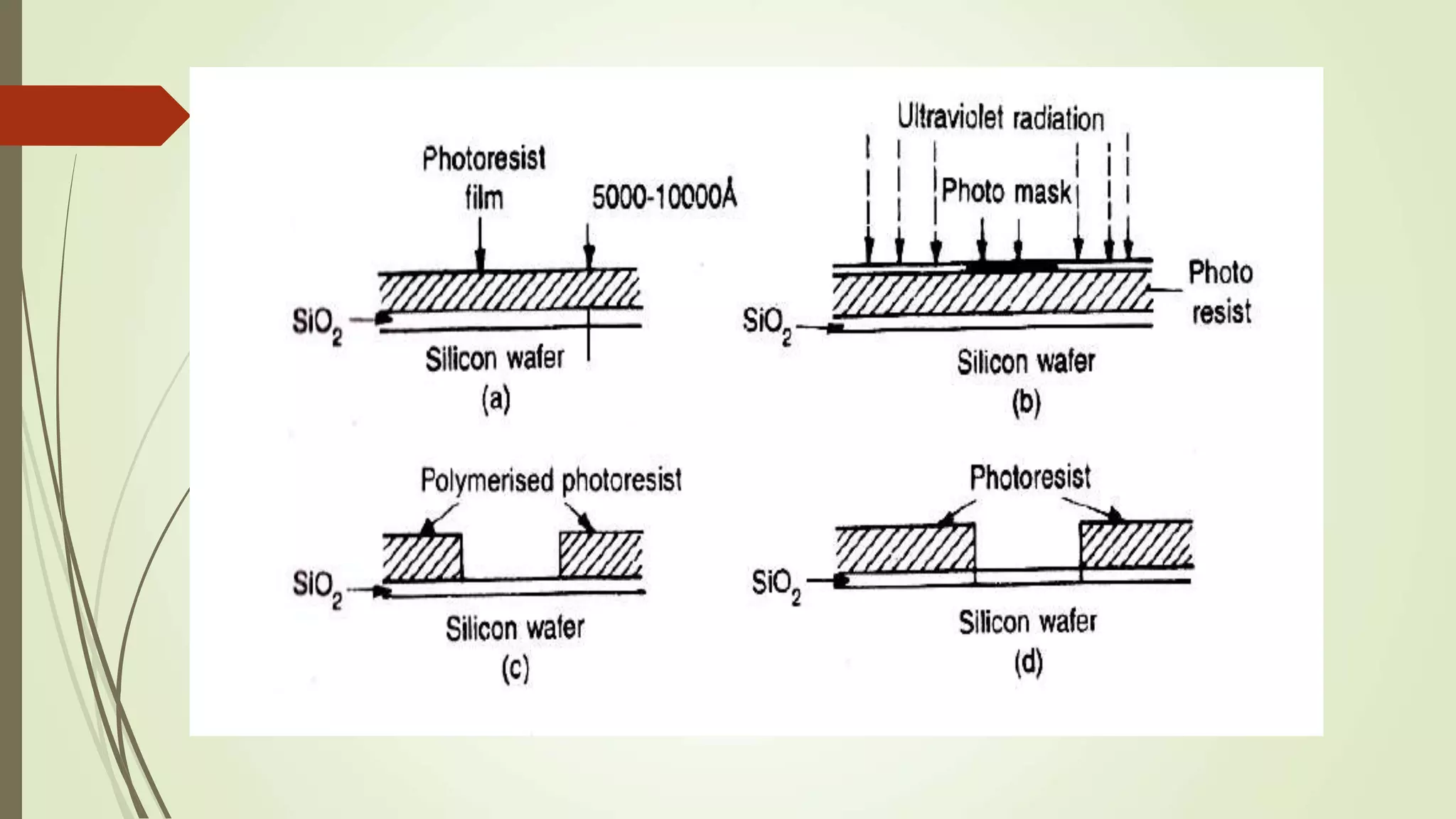

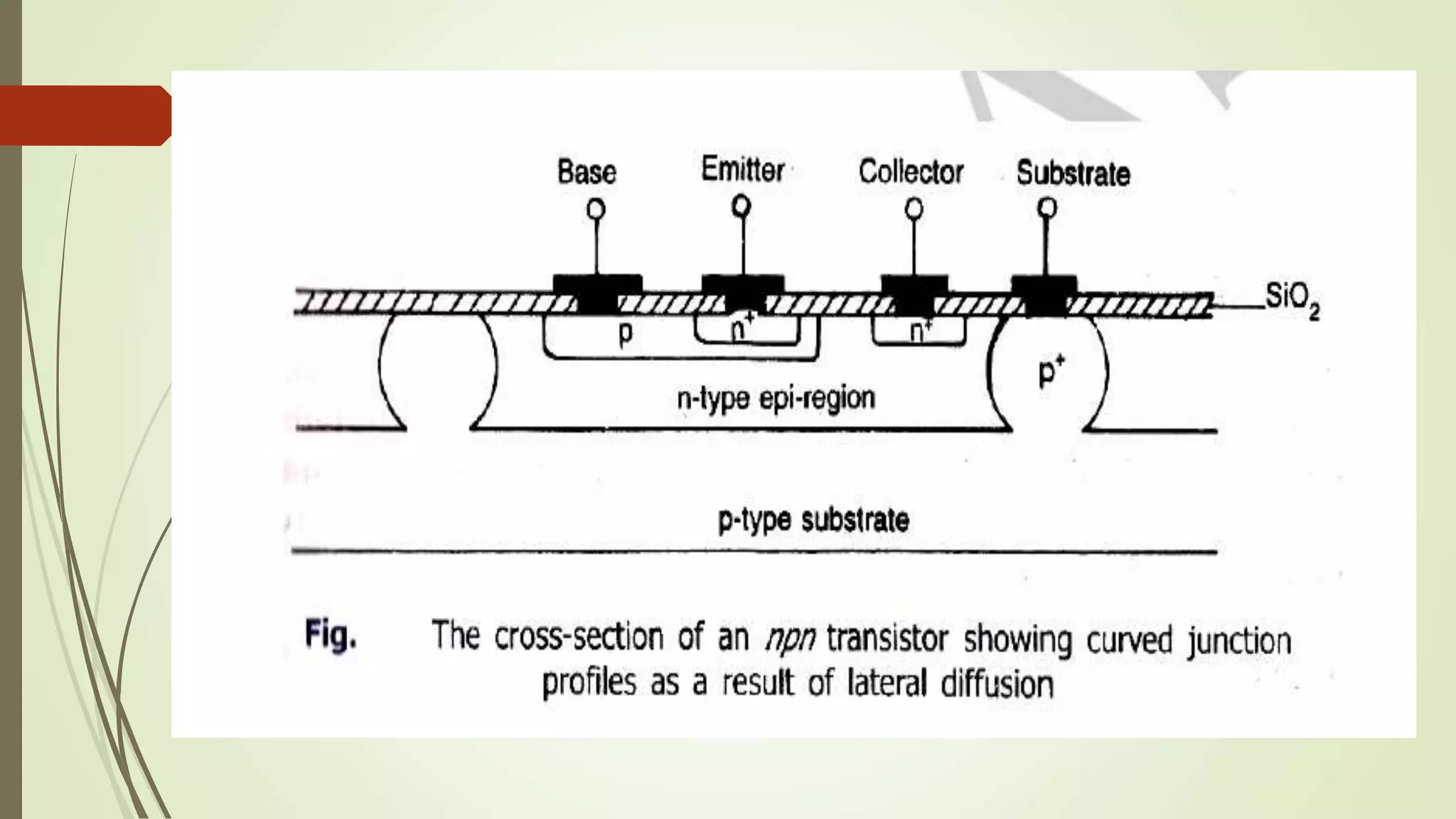

This document provides information on various processes involved in integrated circuit fabrication, including epitaxial growth, oxidation, photolithography, diffusion, ion implantation, isolation techniques, and metallization. Epitaxial growth is used to grow silicon layers on substrates with the same crystal structure. Oxidation grows a silicon dioxide layer for protection and selective doping. Photolithography and etching are used to pattern doped regions. Diffusion and ion implantation introduce impurities. Isolation techniques like PN junctions and dielectric layers separate components. Metallization deposits aluminum for interconnections.