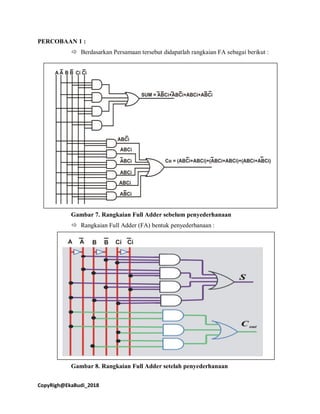

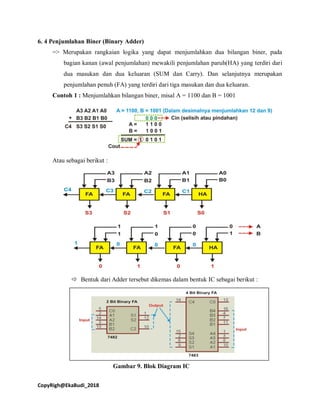

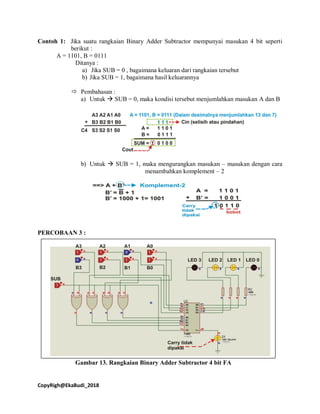

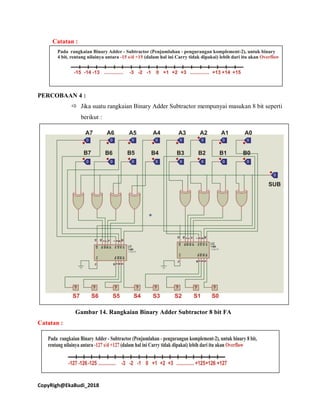

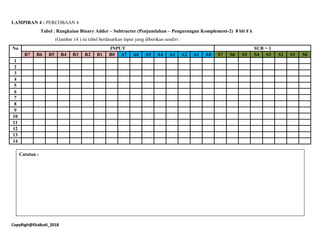

Dokumen ini membahas rangkaian kombinasional aritmatik, termasuk operasi penjumlahan dan pengurangan biner, serta representasi bilangan biner bertanda dan cara kerja unit aritmetika dan logika (ALU) dalam komputer. Diperkenalkan berbagai rangkaian logika seperti adder dan subtractor dalam konteks pengolahan bilangan biner. Selain itu, dijelaskan tentang masalah overflow dan penggunaan metode komplemen untuk bilangan bertanda.