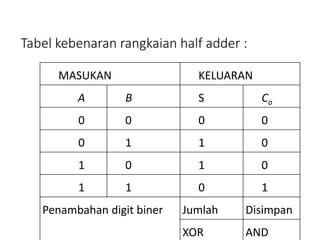

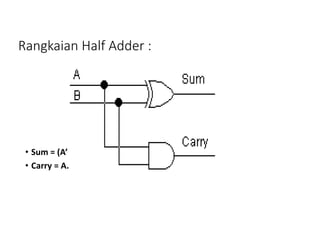

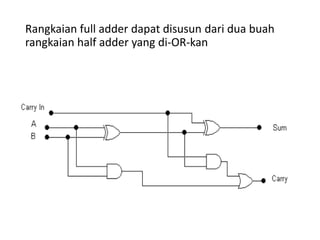

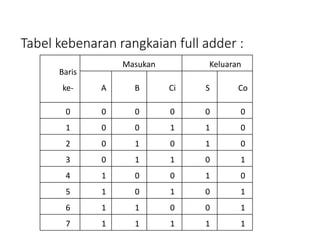

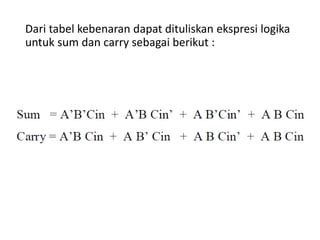

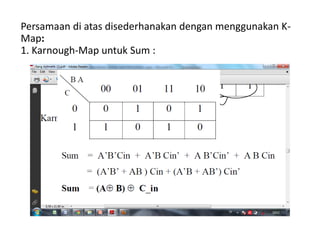

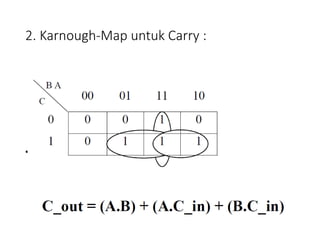

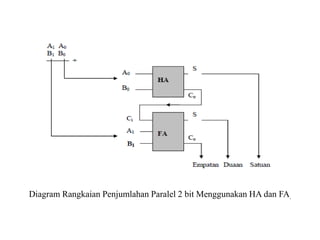

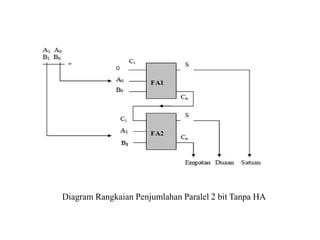

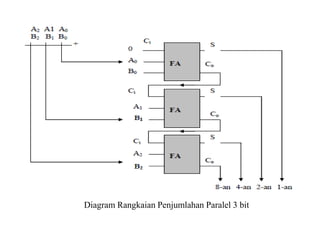

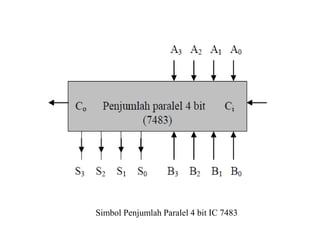

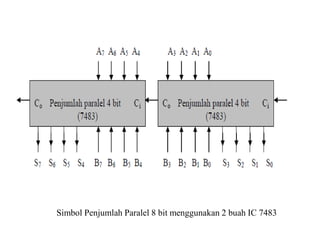

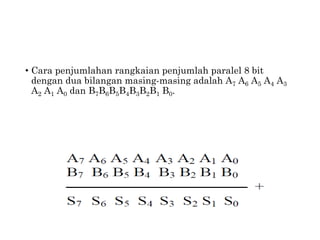

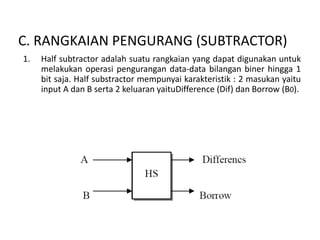

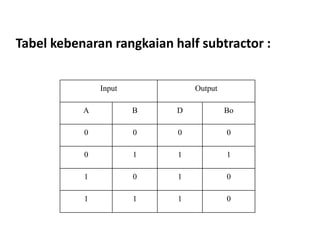

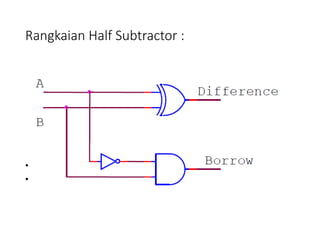

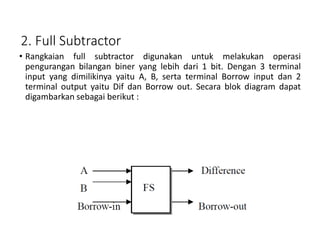

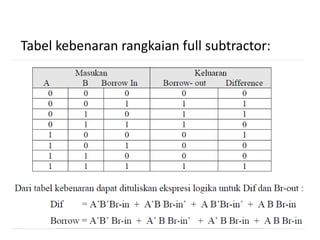

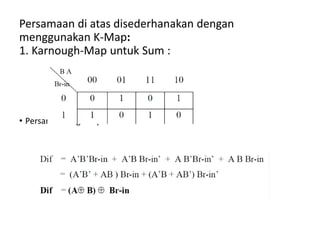

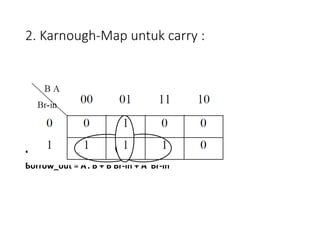

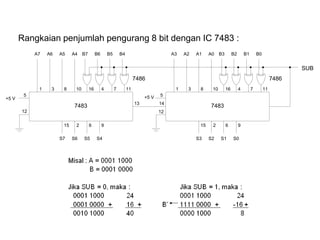

Dokumen ini membahas tentang rangkaian penjumlahan dan pengurangan bilangan biner menggunakan adder dan subtractor. Adder terdiri dari half adder dan full adder yang digunakan untuk menjumlahkan dua bilangan biner, sedangkan subtractor terdiri dari half subtractor dan full subtractor untuk mengurangkan dua bilangan biner. Dokumen ini juga menjelaskan penjumlahan dan pengurangan paralel menggunakan rangkaian adder dan subtractor untuk bilangan biner lebi