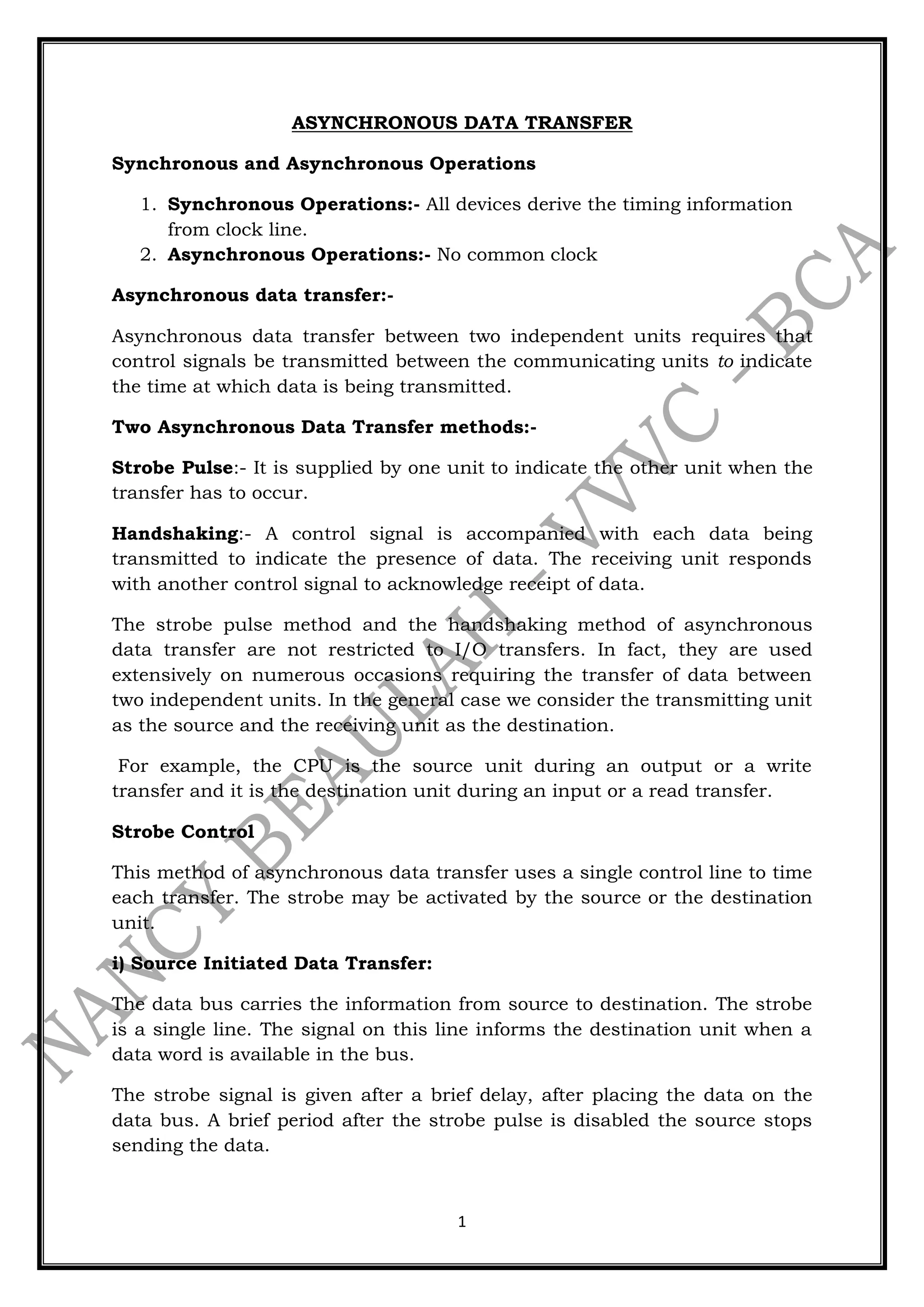

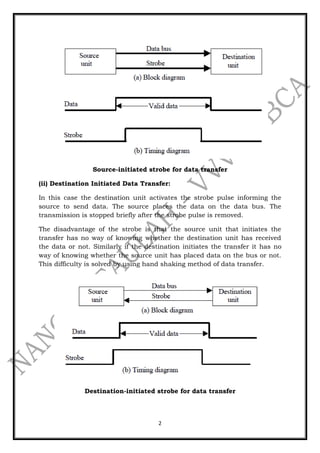

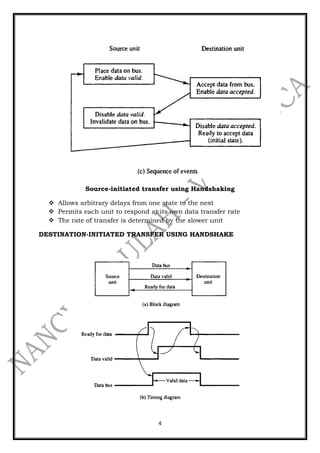

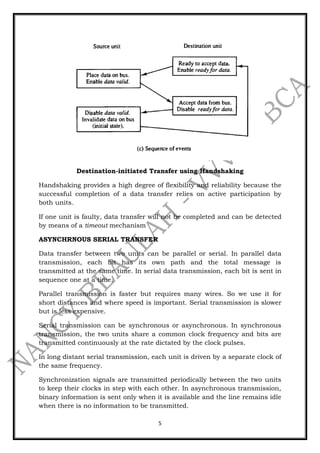

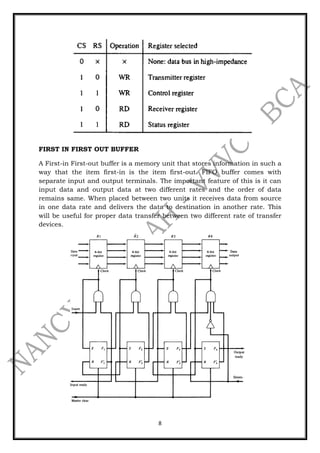

This document discusses asynchronous data transfer methods between independent units without a common clock. It describes two main methods: strobe pulse and handshaking. Strobe pulse uses a single control line to time transfers but the transmitting unit has no confirmation the data was received. Handshaking adds a second control signal so units can confirm receipt. It then discusses asynchronous serial transfer which transmits bits sequentially using start, data, and stop bits to identify characters without a shared clock. First-in first-out (FIFO) buffers are also summarized as allowing input and output of data at different rates while preserving order.