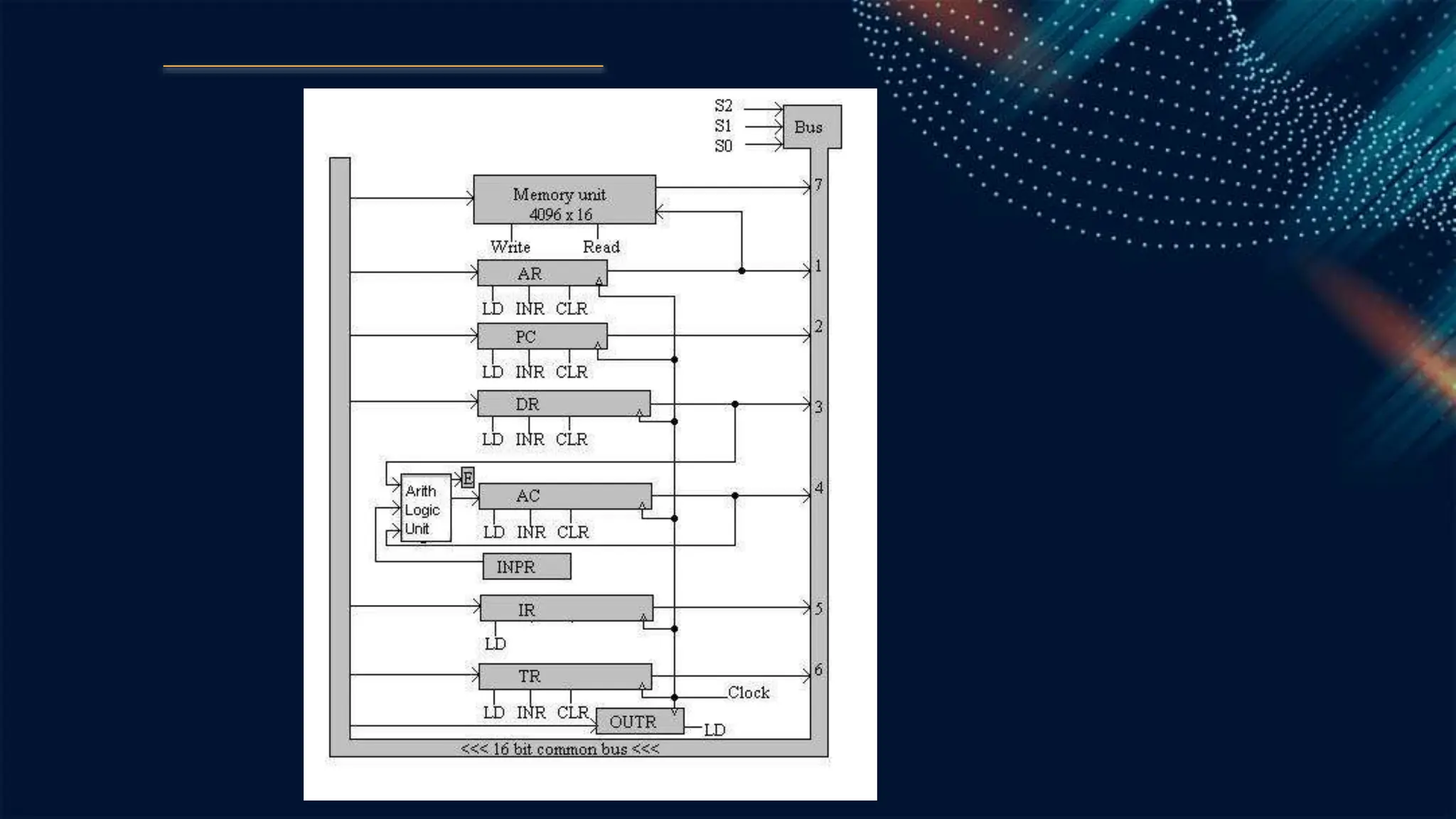

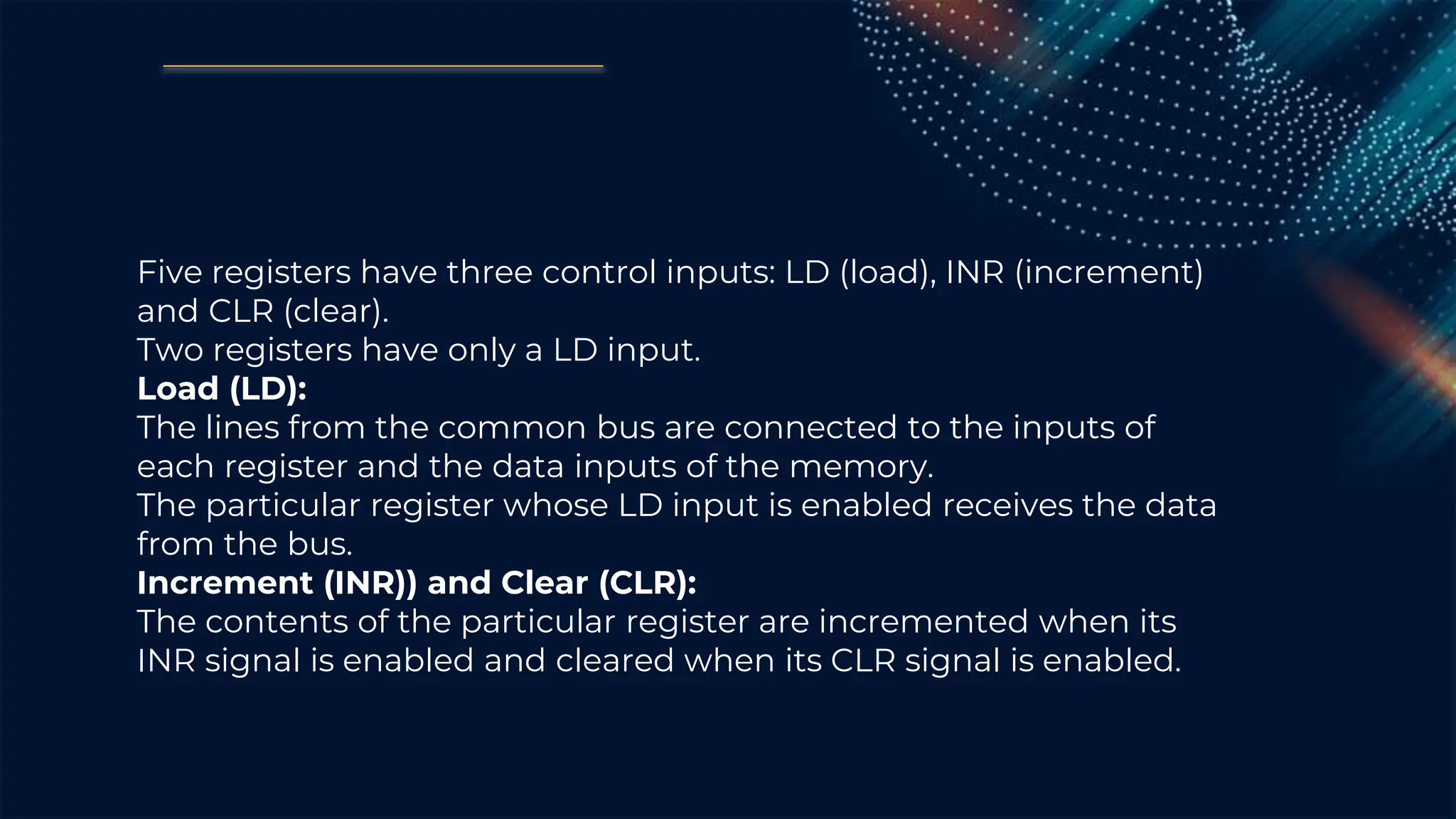

The document summarizes the common bus system used in basic computer architecture. It describes how the common bus provides a shared path for transferring information between the memory unit and registers, including the address register, program counter, data register, accumulator, instruction register, temporary register, input register, and output register. It explains the functions of each register and how they interface with the common bus, memory unit, and other components using selection inputs and control signals like load, increment, and clear to read from or write to the bus.