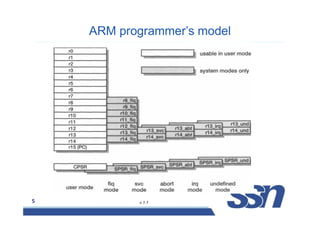

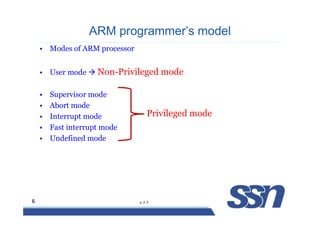

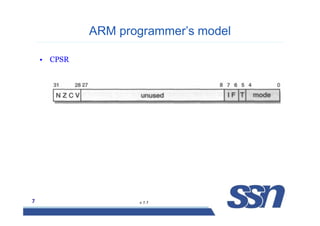

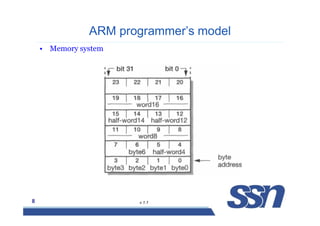

The document discusses the ARM programmer's model. It describes the register set used in ARM including the general purpose registers, program counter, and current program status register. It also covers the memory system and exceptions handling in ARM. When exceptions occur, the current state is saved by copying the program counter and program status register values. The processor then switches to exception mode and the program counter is set to the vector address for the exception handler.