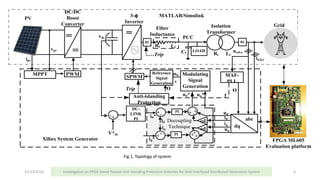

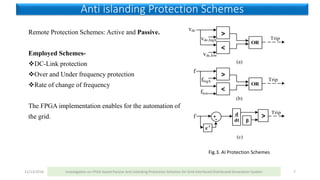

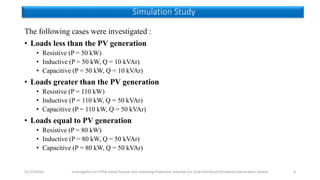

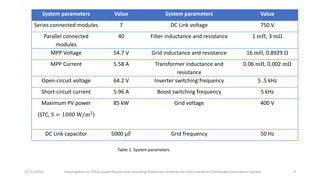

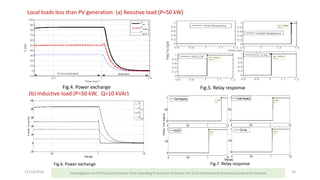

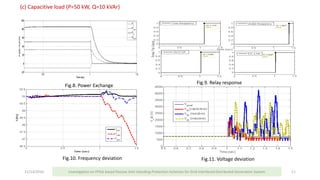

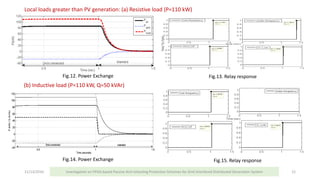

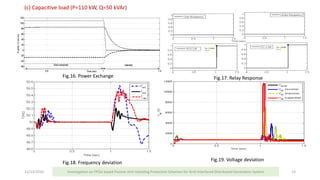

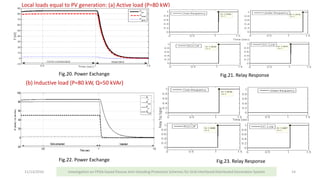

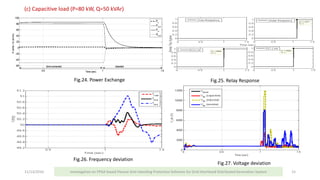

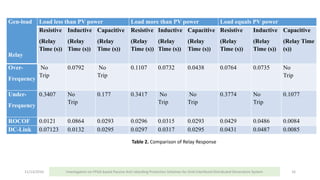

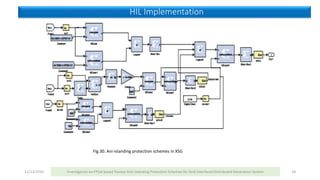

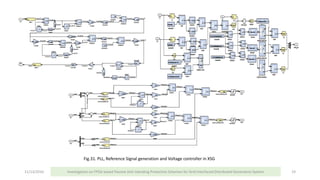

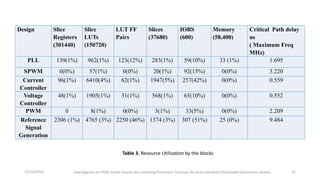

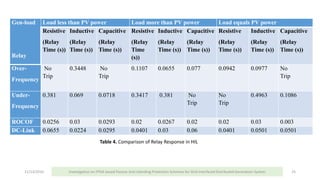

The document discusses investigation of FPGA-based passive anti-islanding protection schemes for grid-interfaced distributed generation systems. It outlines the system topology, inverter control, anti-islanding protection schemes, simulation studies under varying load conditions, hardware-in-loop co-simulation, and concludes the schemes were effective in detection and conform to simulations. Resource utilization and experimental validation on an FPGA platform are also presented.

![References

11/13/2016 Investigation on FPGA based Passive Anti-Islanding Protection Schemes for Grid Interfaced Distributed Generation System 28

[1] Craig Abbey, Yves Brissette, and Philippe Venne, “An autoground system for anti-islanding protection of distributed

generation,” IEEE Transactions on Power & Energy Systems, vol. 29,no. 2, pp. 873-880,2014.

[2] Soummya Kar and Subhransu R Samantaray,“Data-mining-based intelligent anti-islanding protection relay for

distributed generations,” IET Generation, Transmission & Distribution,vol.8, no.4, pp.629-639,2014.

[3] Antonis G Tsikalakis and Nikos D Hatziargyriou, ,“Operation of microgrids with demand side bidding and

continuity of supply for critical loads,” European Transactions on Electrical Power, vol.21.,No.2, PP.1238-1254, 2011.

[4] J A Pecas Lopes, N Hatziargyriou, J Mutale, P Djapic, and N Jenkins,“Integrating distributed generation into electric

power systems: A review of drivers, challenges and opportunities,” Electric power systems

research, vol.77,no.9,pp.1189-1203,2007.

[5] Morris Brenna, Federica Foiadelli, Paola Petroni, Gianluca Sapienza,and Dario Zaninelli,“Distributed Generation

Regulation for Intentional Islanding in Smart Grids,” Proceedings of Innovative Smart Grid Technologies,

IEEE PES,pp.1-6,2012.

[6] IEEE Std. 1547-2003, “IEEE Standard for Interconnecting Distributed Resources With the Electric Power System,”

[7] Mehrnoosh Vatani,Turaj Amraee, Ali Mohammad Ranjbar, and Babak Mozafari,“Relay logic for islanding detection

in active distribution systems,” IET Generation, Transmission & Distribution, vol. 9, no.12, pp.1254-1263,2015

[8] Nahla E Zakzouk,Mohamed A Elsaharty,Ahmed K Abdelsalam,Ahmed A Helal, and Barry W Williams, ,“Improved

performance low-cost incremental conductance PV MPPT technique,” IET Renewable Power Generation,2016.](https://image.slidesharecdn.com/singaporefinal1-161119022507/85/Anti-islanding-28-320.jpg)

![[9] Dong Dong, Bo Wen, Dushan Boroyevich, Paolo Mattavelli, and Yaosuo Xue, ,“Analysis of phase-locked

loop low-frequency stability in three-phase grid-connected power converters considering impedance

interactions,” IEEE Transactions on Industrial Electronics,vol.62 ,no.1,pp.310-321,2015

[10] S.J.Huang and F.S.Pai,“Design and operation of grid connected phototvoltaic system with power factor

control and active islanding detection,” IEEE Proceedings on Generation, Transmission,

Distribution,vol.48,No.2,2001.

[11] Rajasekar Selvamuthukumaran and Rajesh Gupta, “Rapid prototyping of power electronics converters for

photovoltaic system application using Xilinx System Generator,” IET Power Electronics,vol.7,no.9,pp.2269

2278,2014, 2011.

11/13/2016 Investigation on FPGA based Passive Anti-Islanding Protection Schemes for Grid Interfaced Distributed Generation System 29](https://image.slidesharecdn.com/singaporefinal1-161119022507/85/Anti-islanding-29-320.jpg)