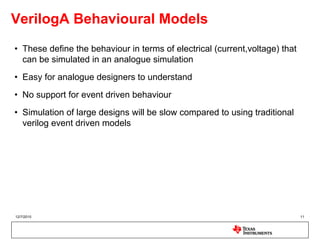

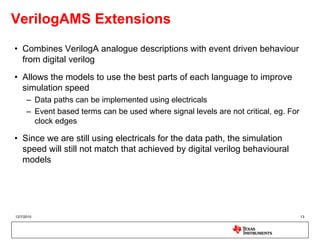

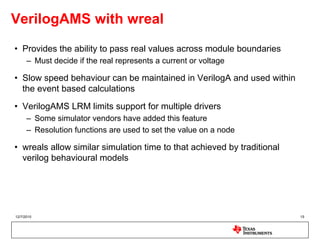

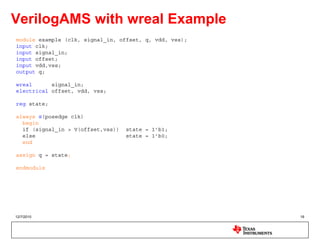

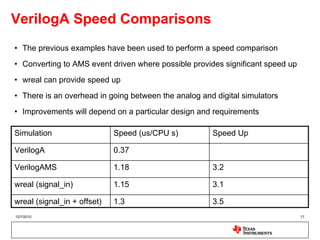

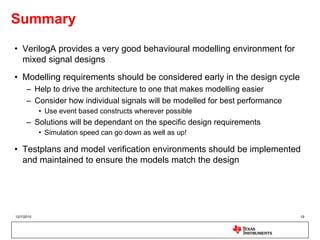

VerilogA provides an environment for mixed-signal behavioral modeling but simulations can be slow. VerilogAMS and using "wreal" values allows combining event-driven and analog modeling for improved speed. Behavioral models must be validated against transistor implementations through regular testing outlined in a testplan to ensure models match the design over time.