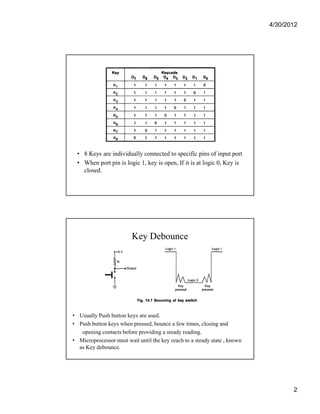

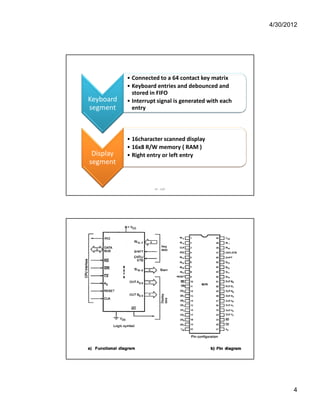

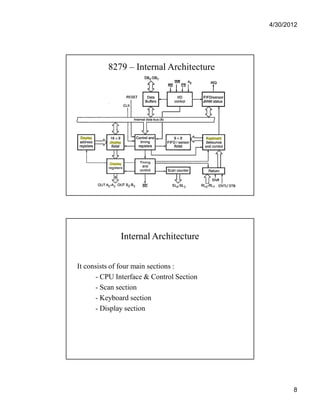

This document provides information about the Intel 8279 keyboard/display controller chip. It describes the chip's architecture and functions. The chip interfaces with both a keyboard and display. It can operate keyboards in two modes - two key lockout or N-key rollover. It also controls a 16 character scanned display. The document outlines the chip's internal blocks, registers, and input/output pin functions for interfacing with a keyboard, display and microprocessor.