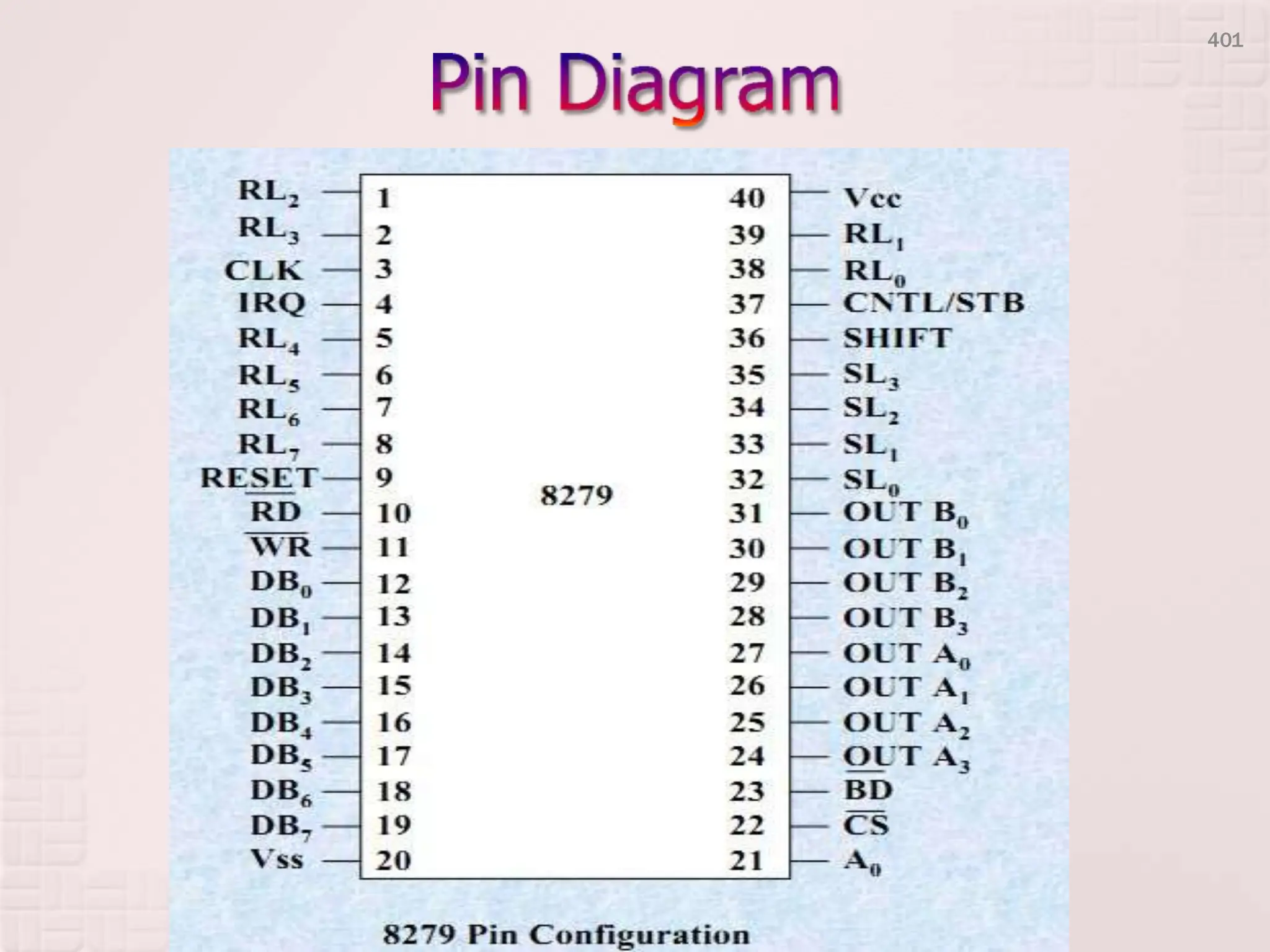

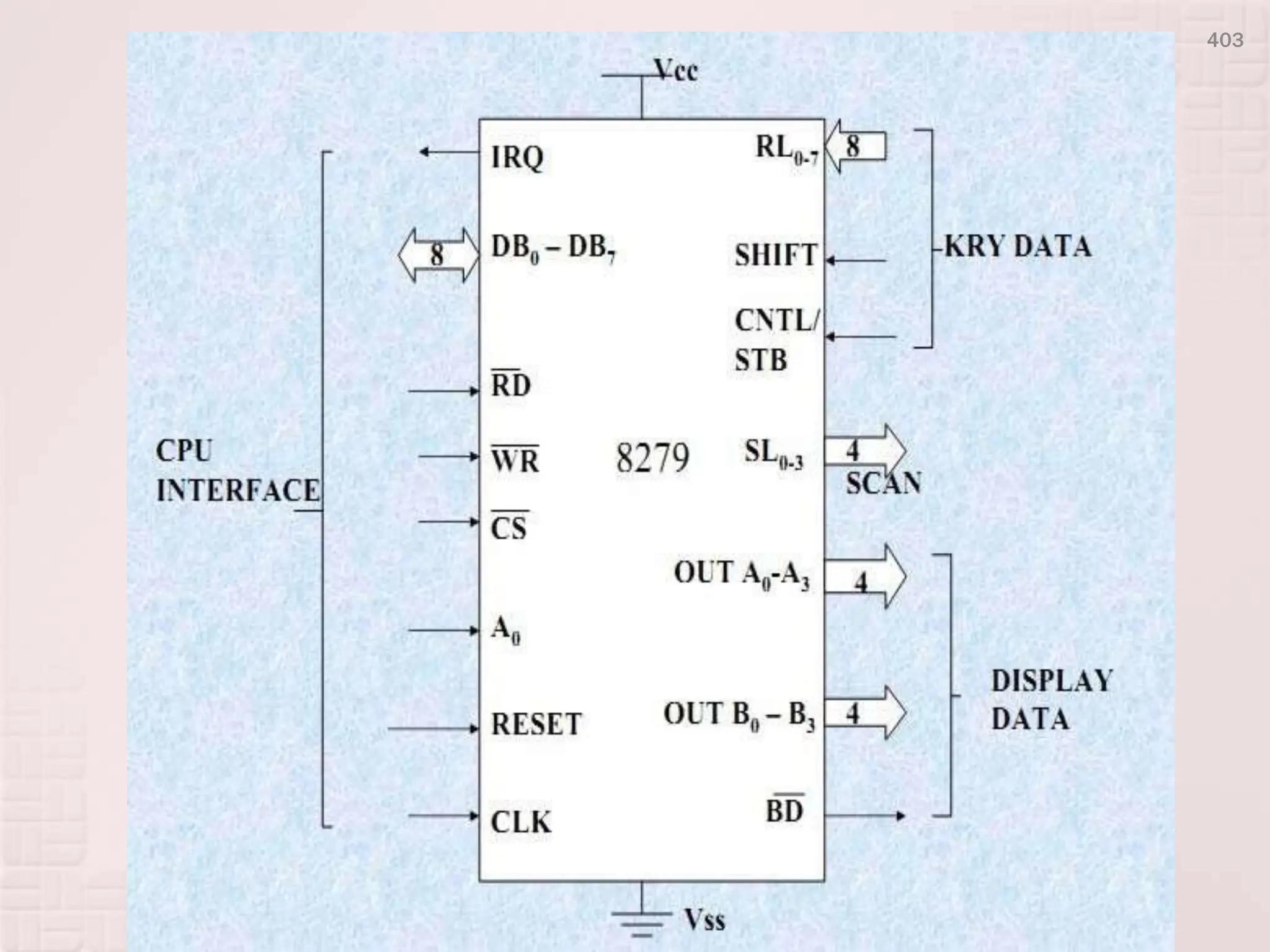

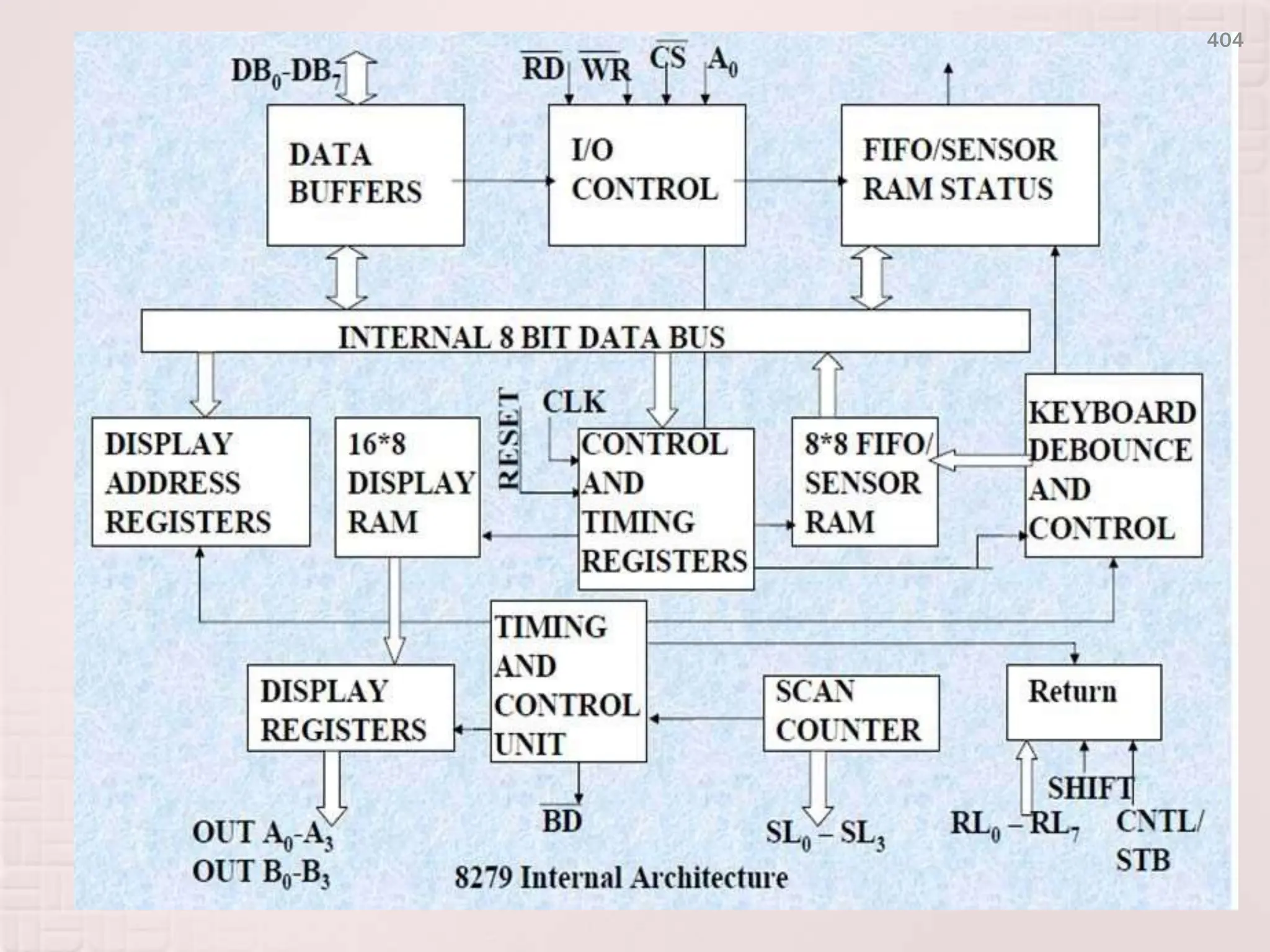

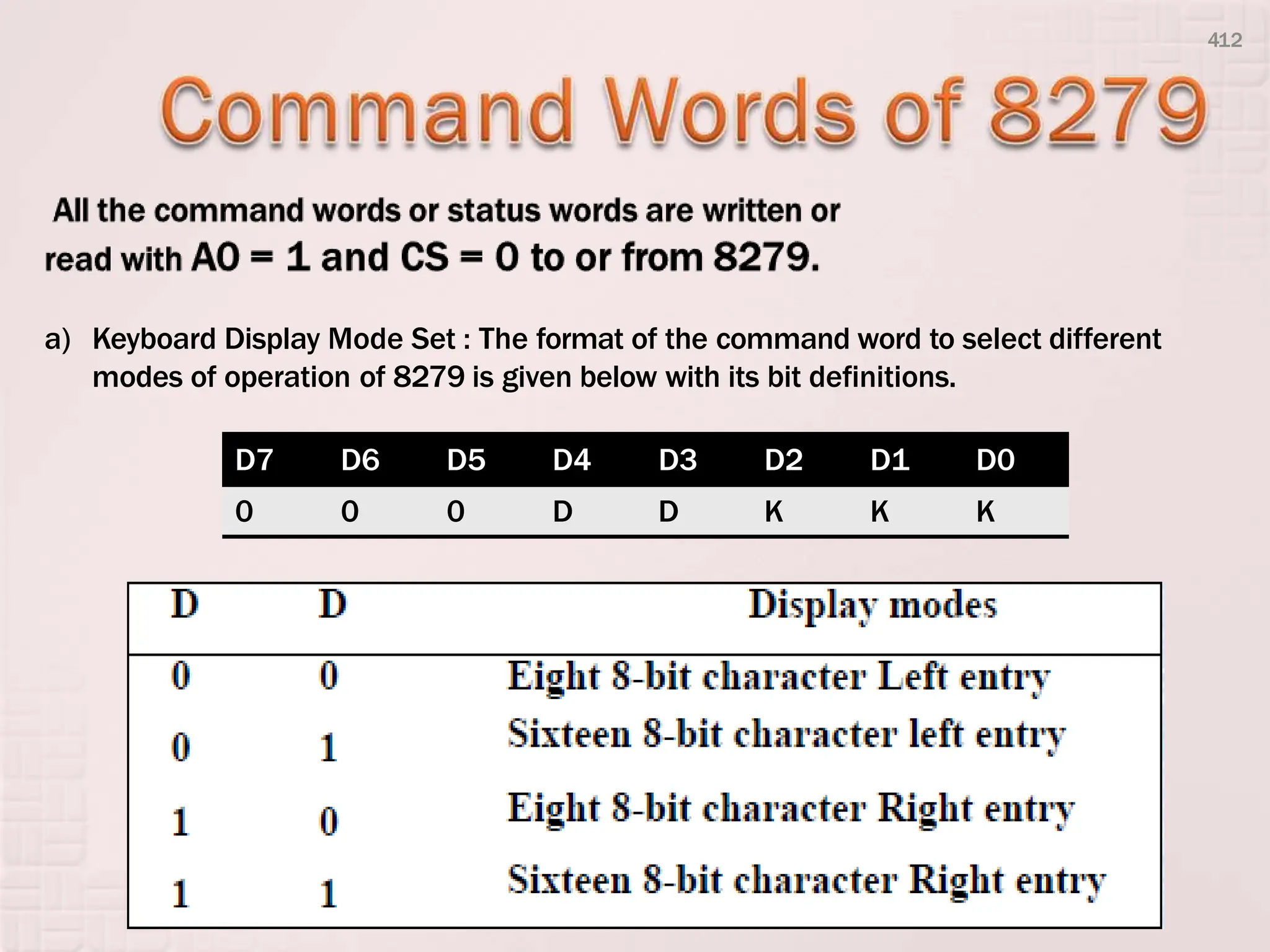

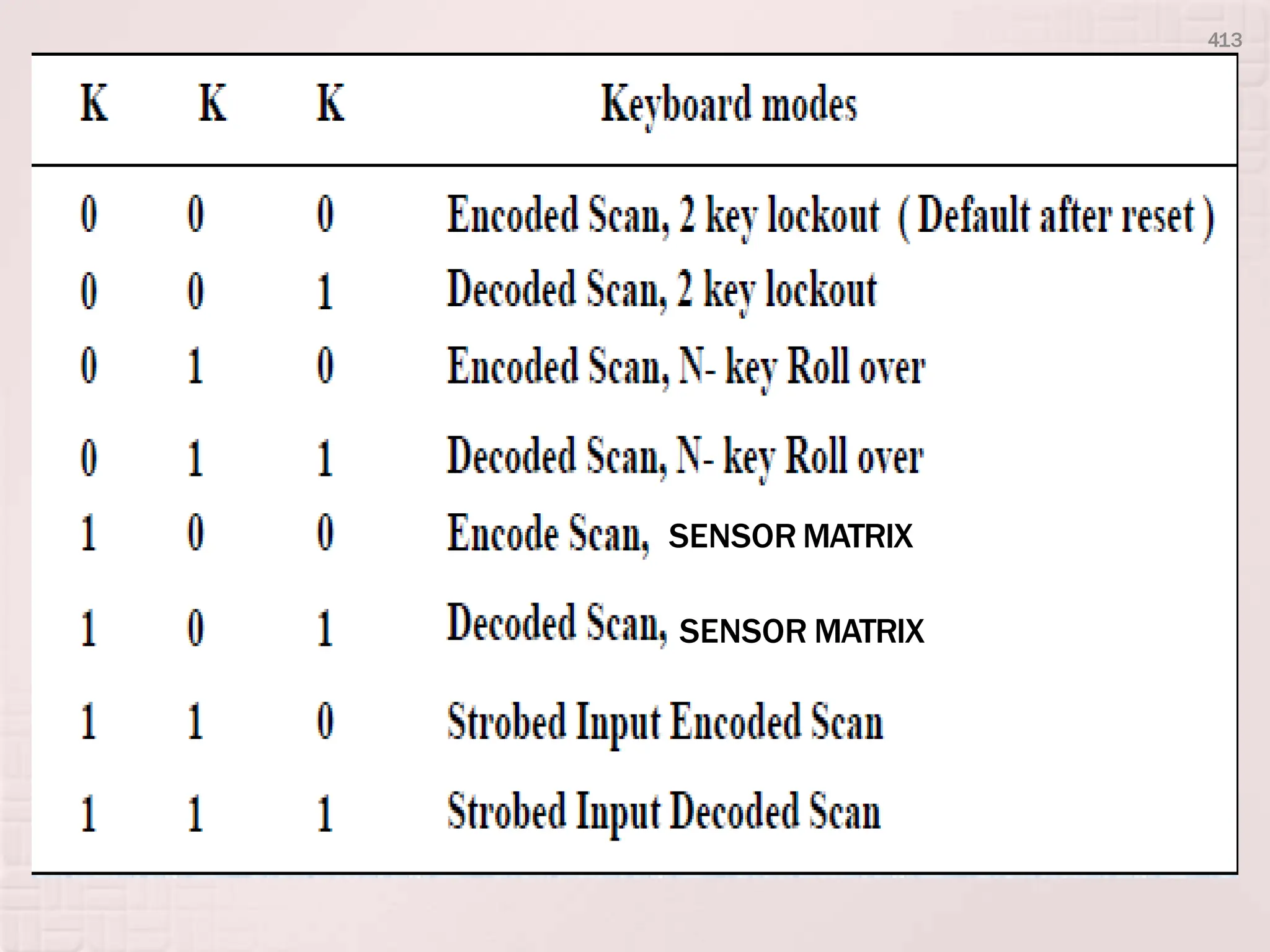

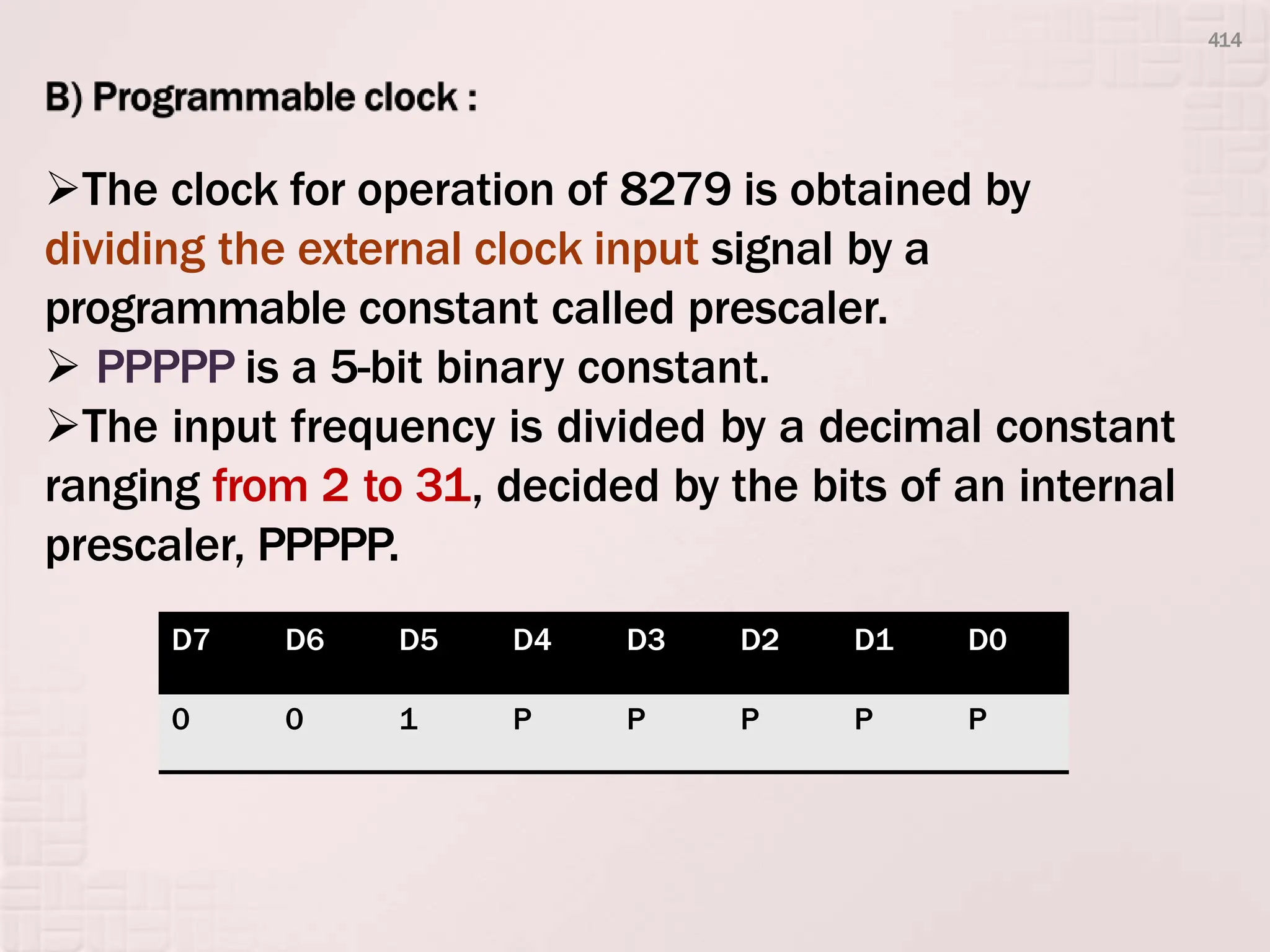

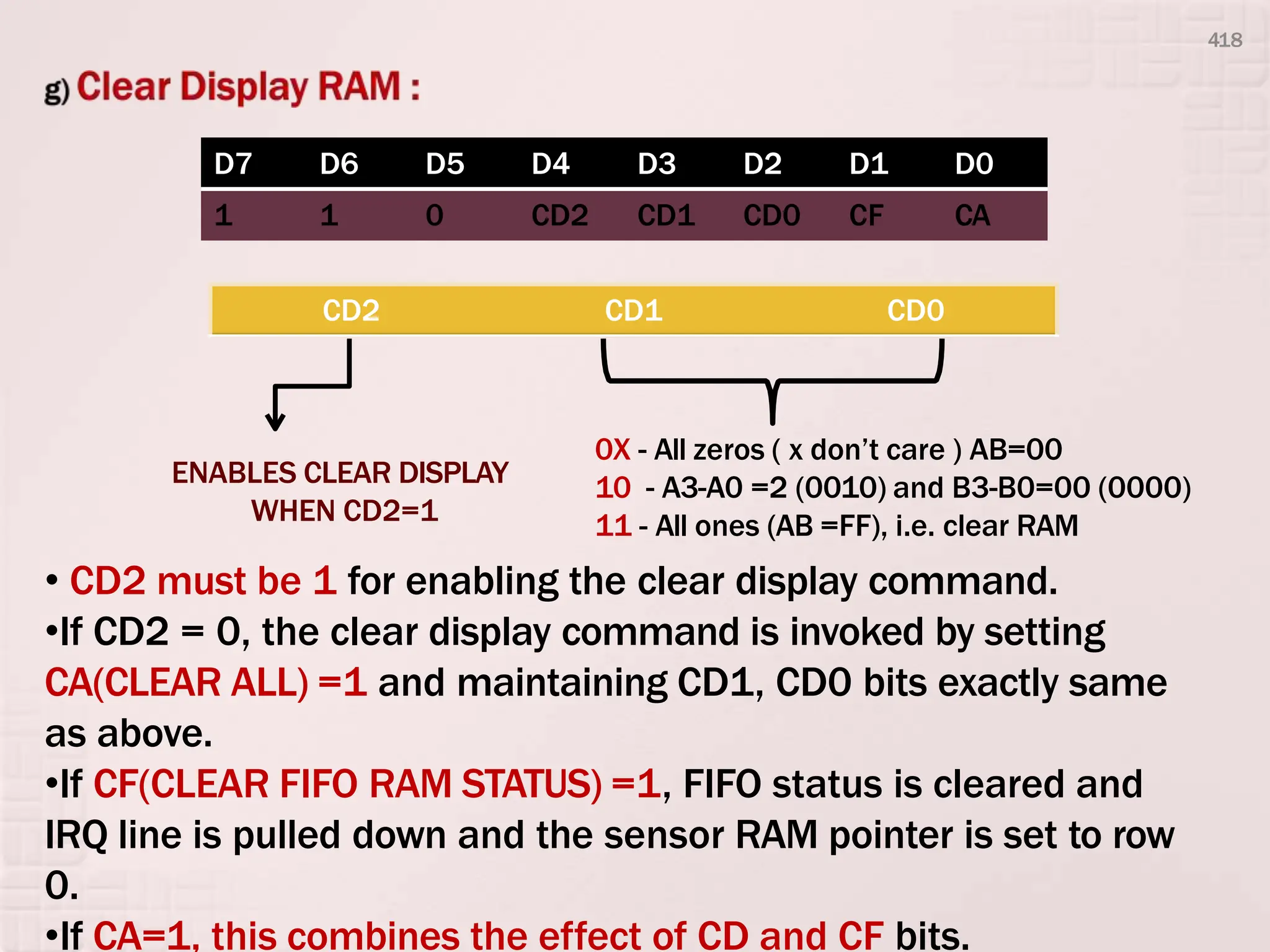

The document provides an overview of the Intel 8279 keyboard/display controller, detailing its features such as an 8-character keyboard FIFO, a 16x8 display RAM, and the operations of the keyboard and display sections. It describes how the keyboard can operate in modes like 2-key lockout and n-key rollover, as well as how data is transferred between the controller and the CPU. The document also covers command word definitions for setting up operations and controlling the display and FIFO operations.