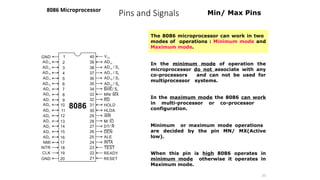

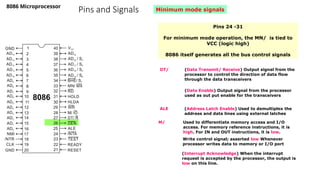

The document provides a comprehensive overview of microprocessor generations, detailing the evolution from the first generation in the early 1970s to the fifth generation with Pentium 3. It describes the architecture and components of the Intel 8086 microprocessor, including the bus interface unit, execution unit, registers, and pin configurations, along with their operational modes. Furthermore, it outlines the minimum and maximum mode operations of the 8086, emphasizing the control signals needed for memory and I/O interfacing.

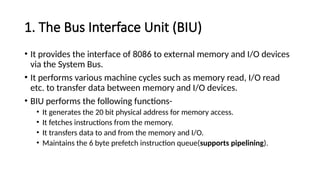

![General Purpose Register

• AX register: This is the accumulator. It is of 16 bits and is divided into two 8-bit registers AH and AL to also

perform 8-bit instructions. It is generally used for arithmetical and logical instructions .

• BX register: The base register. It is of 16 bits and is divided into two 8-bit registers BH and BL to also

perform 8-bit instructions. It is used to store the value of the offset.

Example: MOV BL, [500] (BL = 500H)

• CX register: Counter register. It is of 16 bits and is divided into two 8-bit registers CH and CL to

also perform 8-bit instructionsIt holds count for instructions like loop, rotate, shift and string

operations.

Example:

• DX register: Data register. It is of 16 bits and is divided into two 8-bit registers DH and DL to also

perform 8-bit instructions. It is used with AX to hold 32 bit values during multiplication and division.

MOV CX, 0005 LOOP](https://image.slidesharecdn.com/module1co2-241102132137-54651322/85/Module-1-Computer-Organization-2-pptx-14-320.jpg)

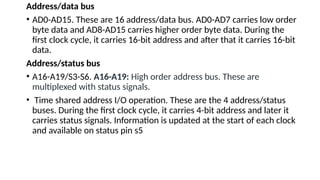

![Addressing Modes : Memory Access

8086 Microprocessor

To access memory we use these four registers: BX,

SI, DI, BP

Combining these registers inside [ ] symbols, we can

get different memory locations (Effective Address,

EA)

Supported combinations:

[BX + SI]

[BX + DI]

[BP + SI]

[BP + DI]

[SI]

[DI]

d16 (variable offset only)

[BX]

[BX + SI + d8]

[BX + DI + d8]

[BP + SI + d8]

[BP + DI + d8]

[SI + d8]

[DI + d8]

[BP + d8]

[BX + d8]

[BX + SI + d16]

[BX + DI + d16]

[BP + SI + d16]

[BP + DI + d16]

[SI + d16]

[DI + d16]

[BP + d16]

[BX + d16]

BX

BP

SI

DI

+ disp](https://image.slidesharecdn.com/module1co2-241102132137-54651322/85/Module-1-Computer-Organization-2-pptx-59-320.jpg)

![Accessing data from commonly used I/O mapped devices or

ports is done using these addressing modes.

Example

IN AL,

[09H]

PORT adder = 09H (AL) ← (PORT)

The content of the port with address 09H is moved to the AL register

Input/Output

Mode](https://image.slidesharecdn.com/module1co2-241102132137-54651322/85/Module-1-Computer-Organization-2-pptx-60-320.jpg)