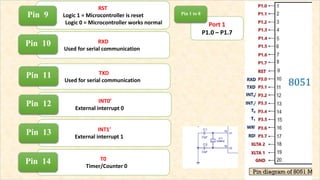

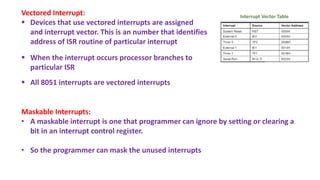

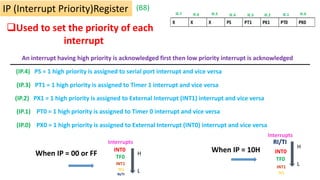

The document provides an overview of fundamentals related to microcontrollers including the 8051 microcontroller. It defines common terms like binary number, bit, byte, word, bus, register, integrated circuit, and microprocessor. It then discusses the 8051 microcontroller specifically, covering its memory organization, I/O ports, timers, interrupts, and special function registers. The document is intended as a revision guide for understanding basic microcontroller concepts centered around the popular 8051 microcontroller.