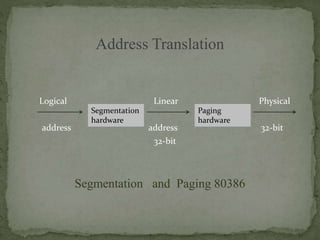

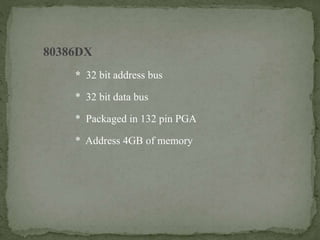

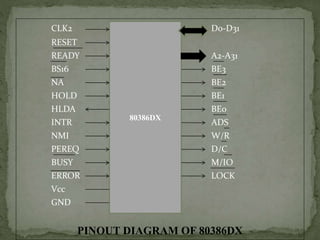

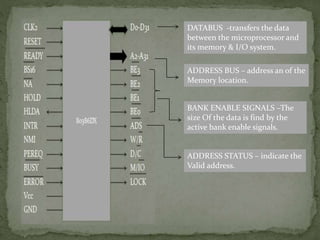

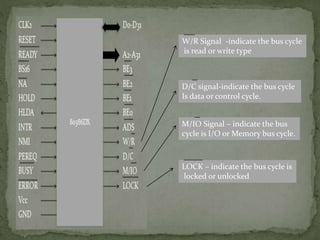

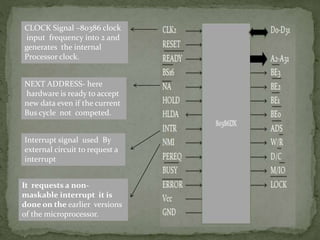

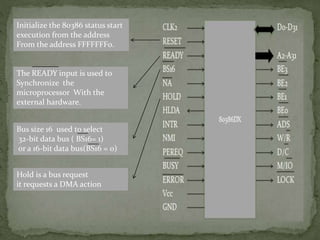

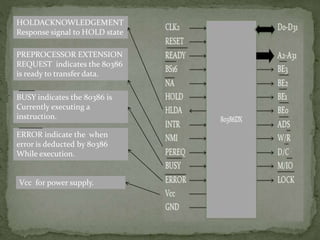

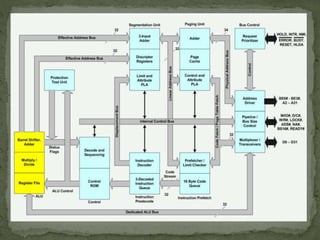

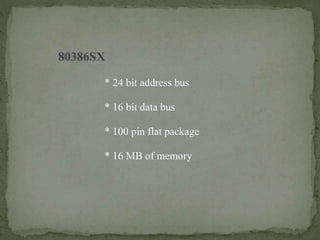

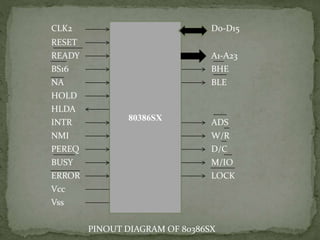

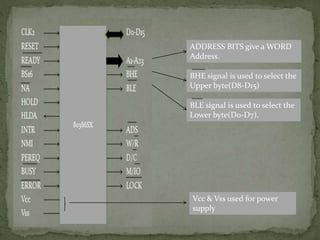

The document summarizes the Intel 80386 microprocessor, which was introduced in 1985. It discusses the key features and architecture of both the 80386DX and 80386SX versions. The 80386 was Intel's first 32-bit microprocessor and supported addressing up to 4GB of physical memory and 64TB of virtual memory using segmentation and paging. It had several operating modes and instruction sets to support multitasking and memory protection in protected mode.