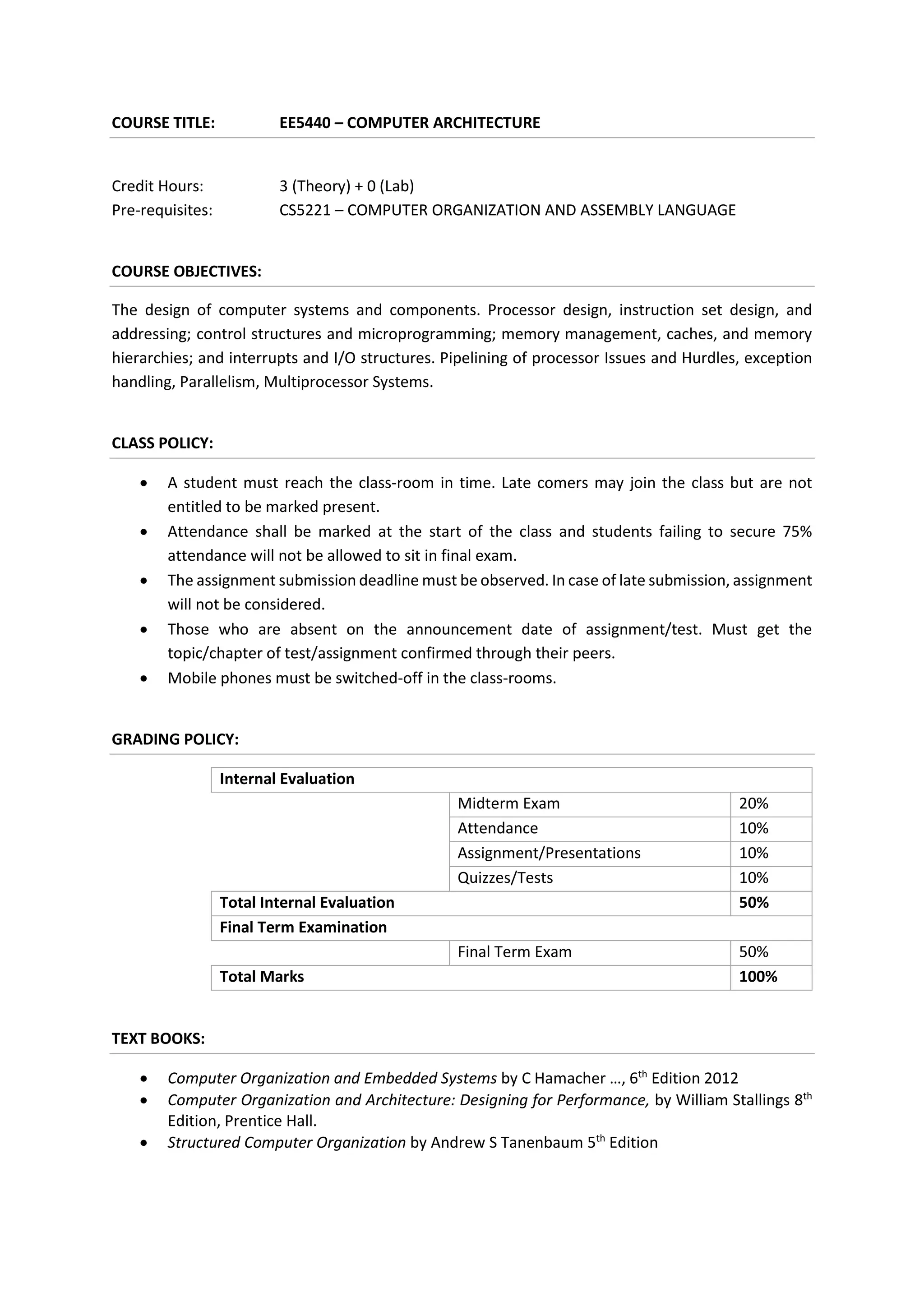

This document outlines the course objectives, policies, and schedule for EE5440 - Computer Architecture, a 3-credit course with prerequisites in Computer Organization. The course objectives cover processor design, instruction sets, addressing, control structures, memory hierarchies, pipelining, parallelism, and multiprocessor systems. Course policies require timely attendance of at least 75% of classes and adherence to assignment deadlines. Grading will be based 50% on a midterm and final exam, and 50% on assignments, presentations, quizzes, and attendance. The course will cover topics like basic computer structure, instruction set architecture, I/O systems, processor design, arithmetic, memory systems, caches, and virtual memory over 16 weekly classes