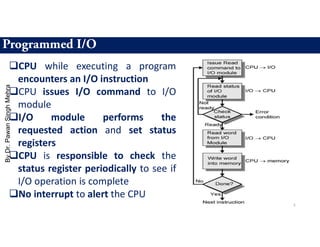

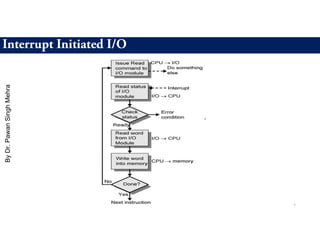

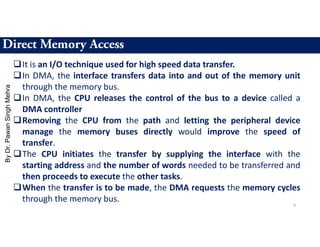

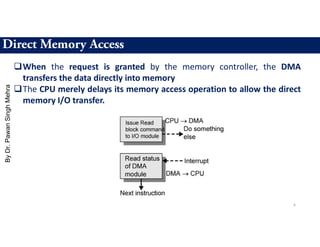

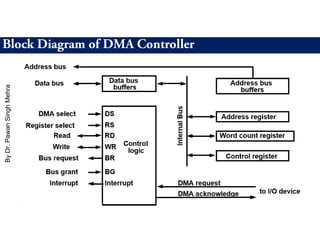

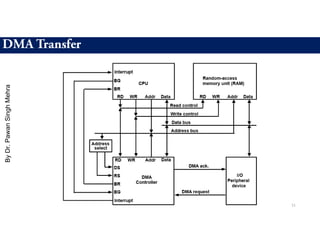

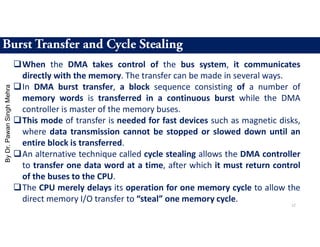

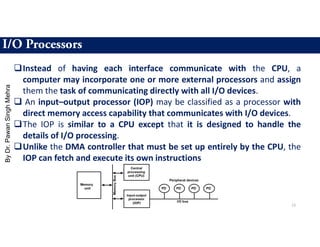

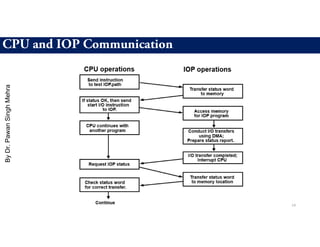

This document outlines various modes of input/output (I/O) organization in computer architecture, covering programmed I/O, interrupt-driven I/O, and direct memory access (DMA). It describes the processes involved in each mode, highlighting the differences in CPU involvement and efficiency. The document also discusses I/O processors and their role in facilitating faster data transfer between devices and memory.