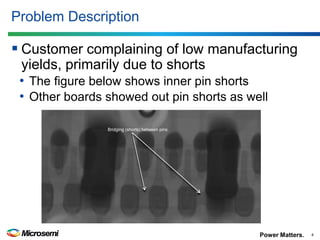

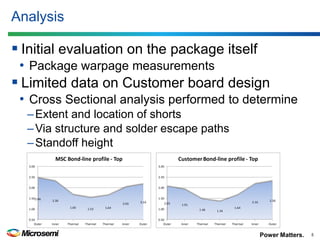

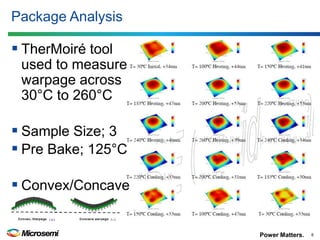

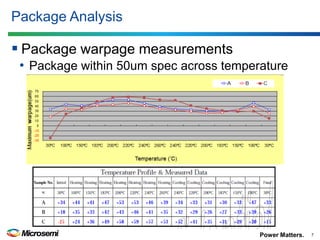

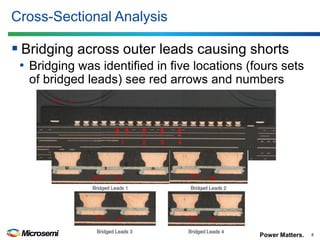

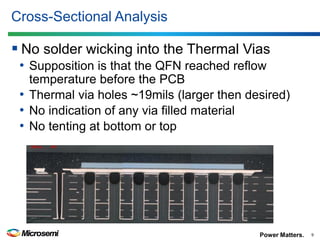

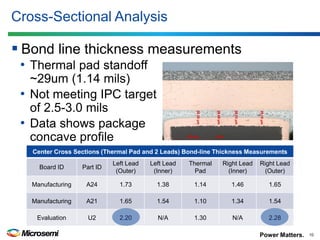

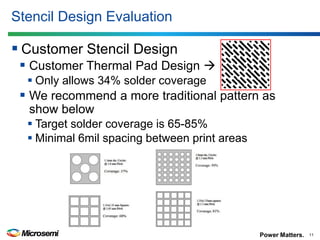

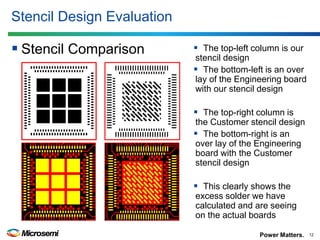

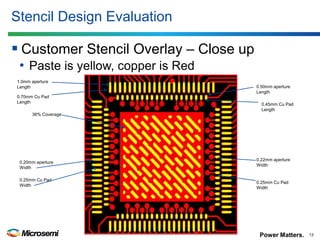

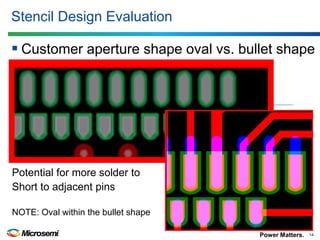

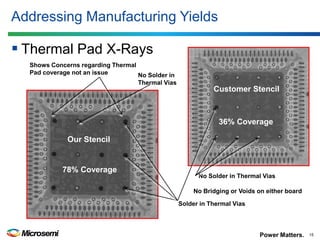

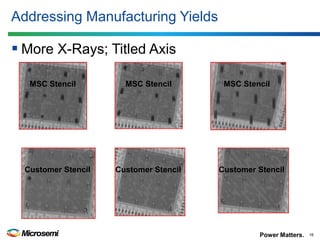

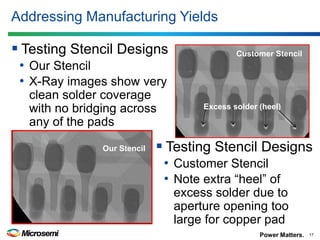

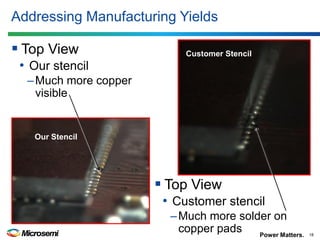

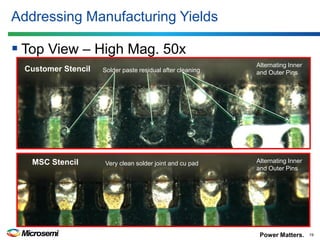

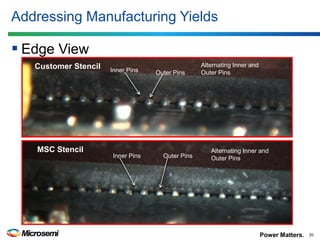

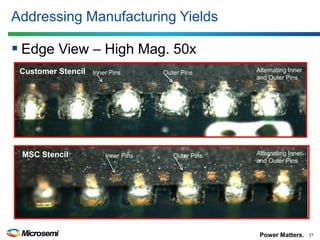

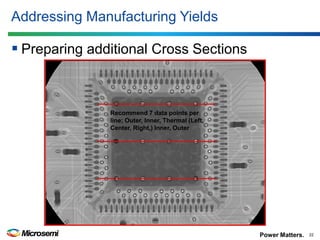

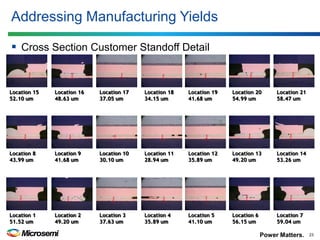

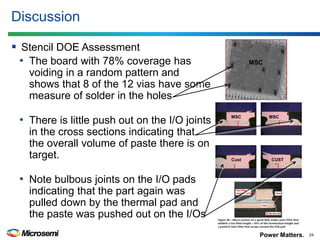

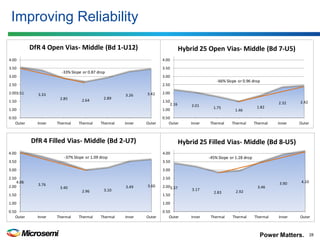

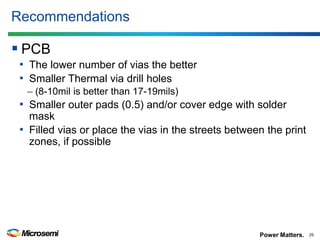

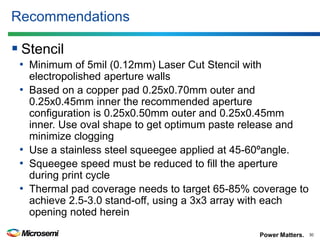

This document discusses improving manufacturing yields and reliability for a QFN package. It found that the customer's stencil design led to excess solder causing shorts between pins. Analysis showed the package itself was not an issue. Redesigning the stencil apertures to better match the pad sizes and using a crosshatch pattern for the thermal pad improved solder coverage and increased standoff height to meet reliability targets. Testing different stencil designs validated that the redesigned stencil addressed the shorting issues and improved manufacturing yields.