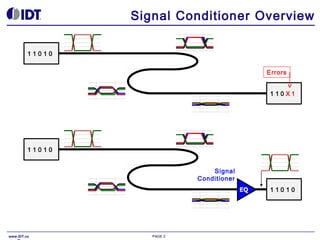

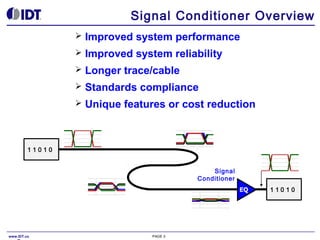

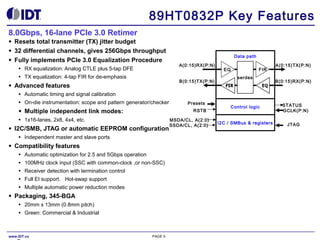

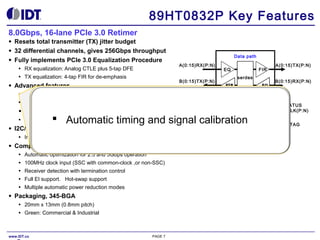

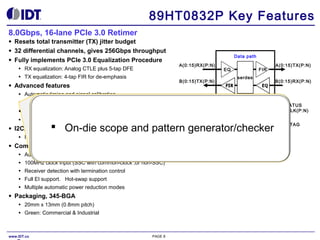

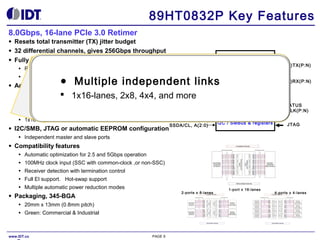

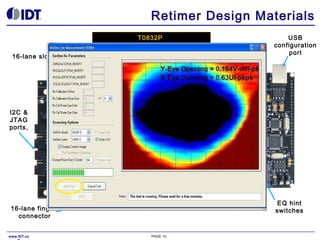

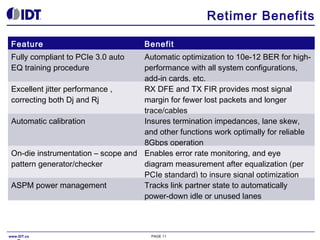

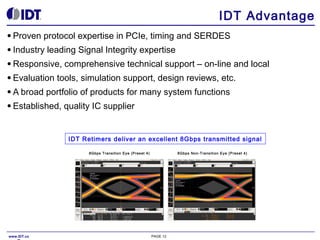

The document details the 89HT0832P, an 8.0Gbps, 16-lane PCIe 3.0 retimer designed to enhance signal integrity and system performance for high-performance computing and telecom applications. Key features include automatic equalization procedures, advanced equalization techniques, and on-die instrumentation for monitoring signal quality. Additionally, the retimer supports multiple link configurations and offers power management features to optimize performance and reduce energy consumption.