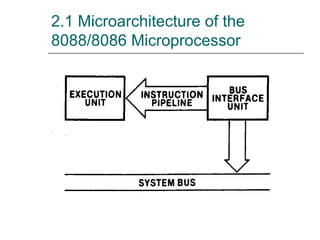

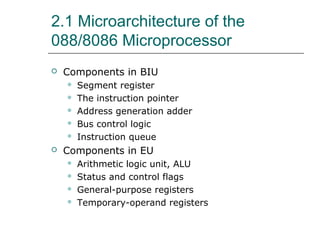

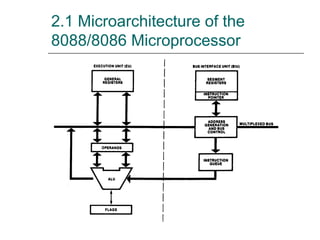

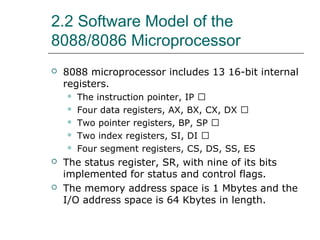

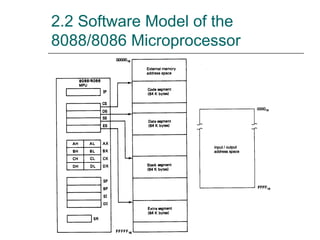

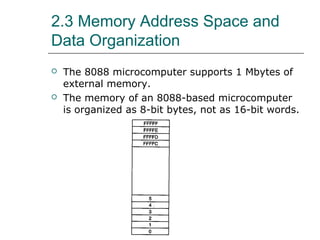

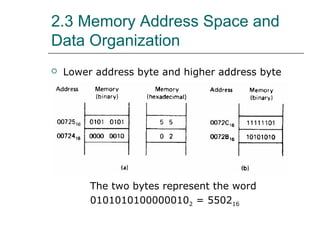

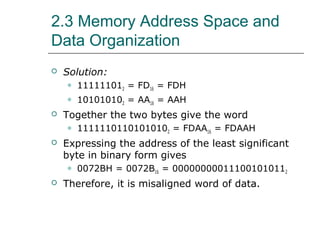

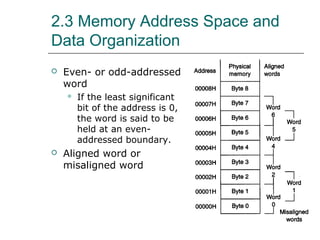

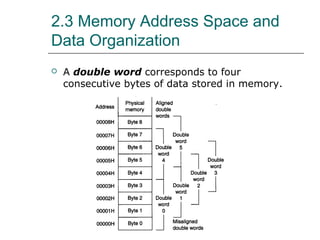

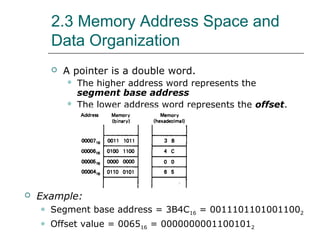

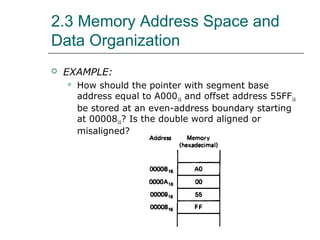

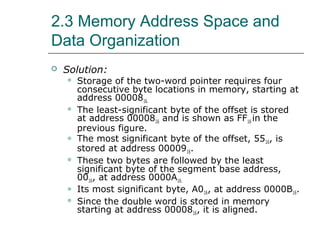

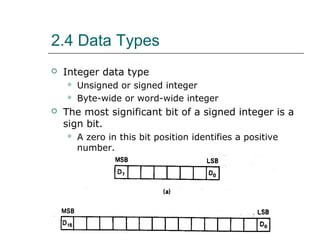

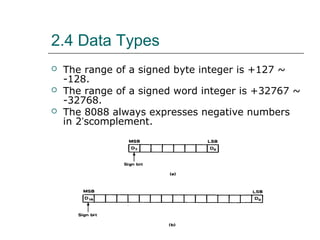

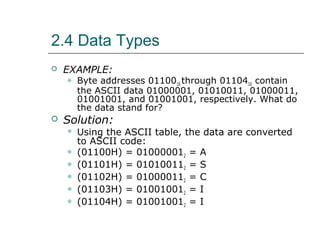

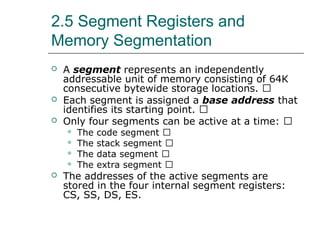

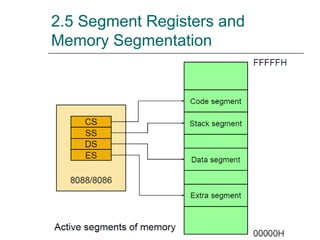

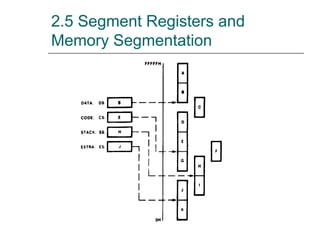

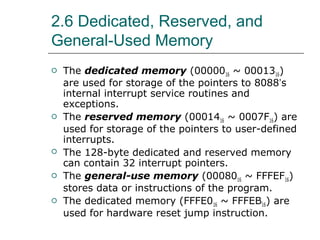

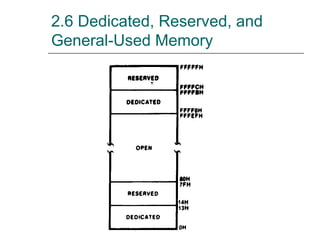

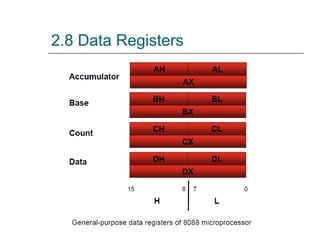

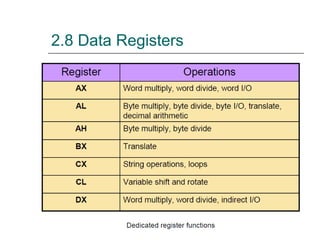

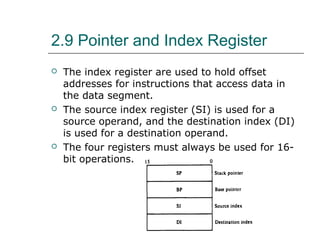

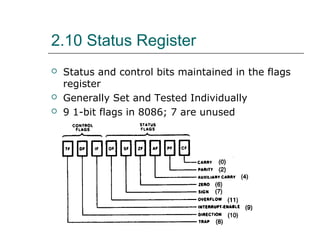

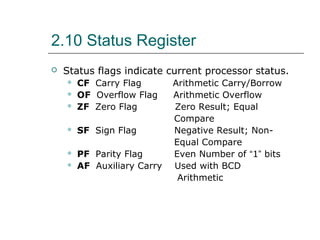

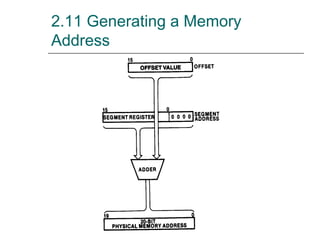

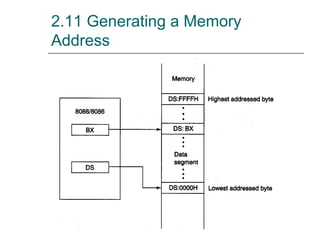

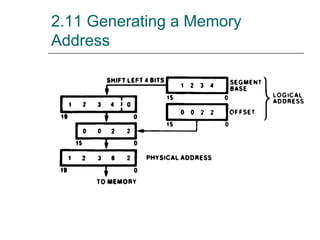

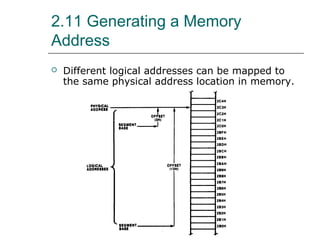

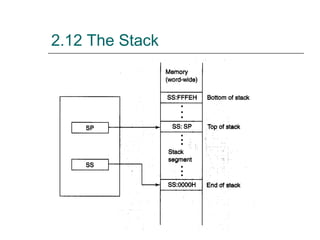

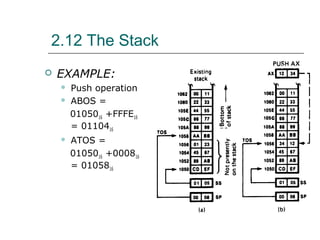

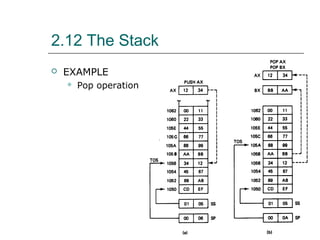

This document describes the software architecture of the Intel 8088 and 8086 microprocessors. It covers topics such as the microarchitecture, memory addressing, registers, data types, segmentation, the stack, and input/output. The 8088/8086 use segmentation to access up to 1MB of memory using segment registers and offsets. They contain various registers for data, pointers, indexes, and status flags. Memory is addressed by combining a segment base with an offset to generate a physical address.