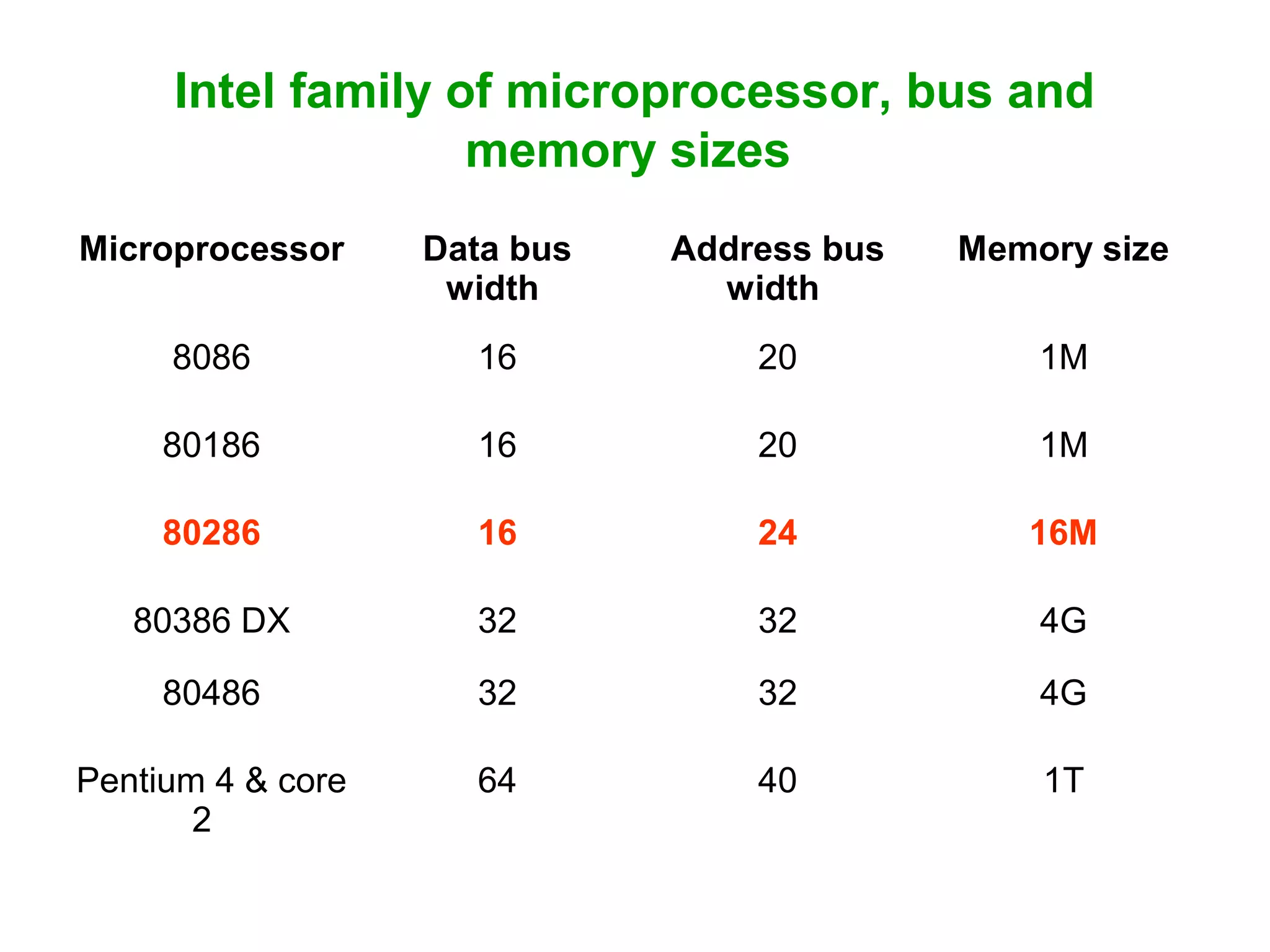

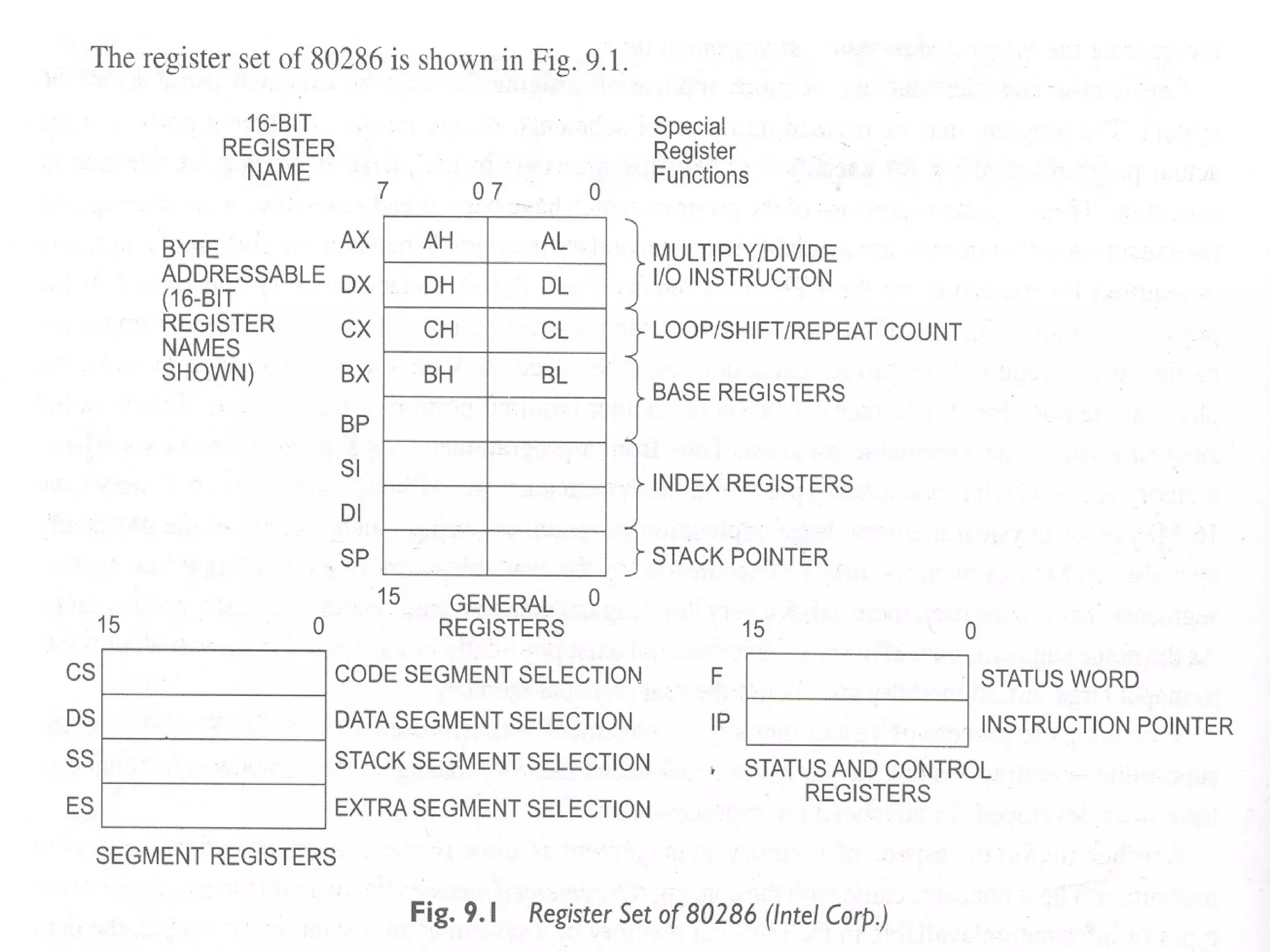

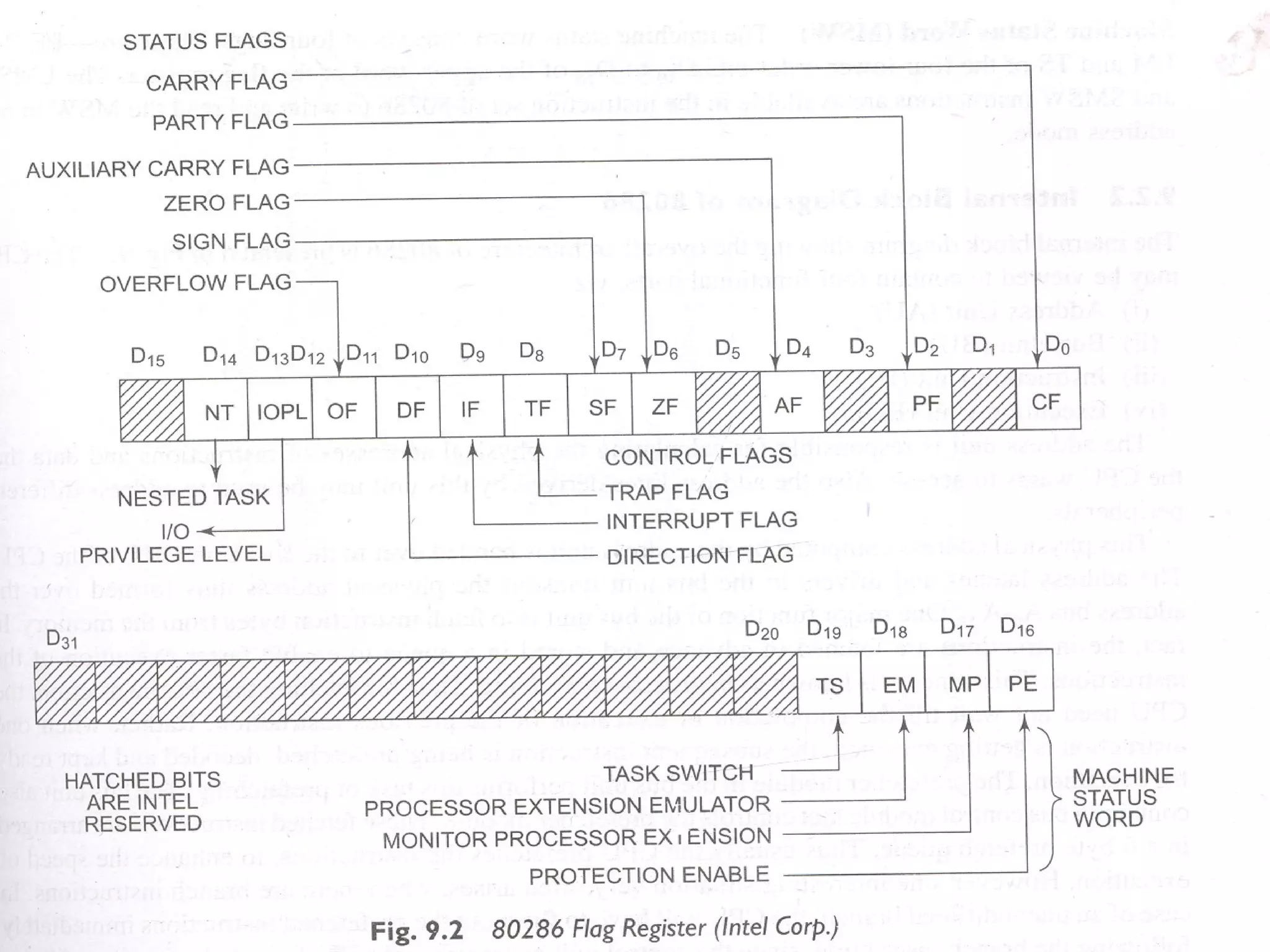

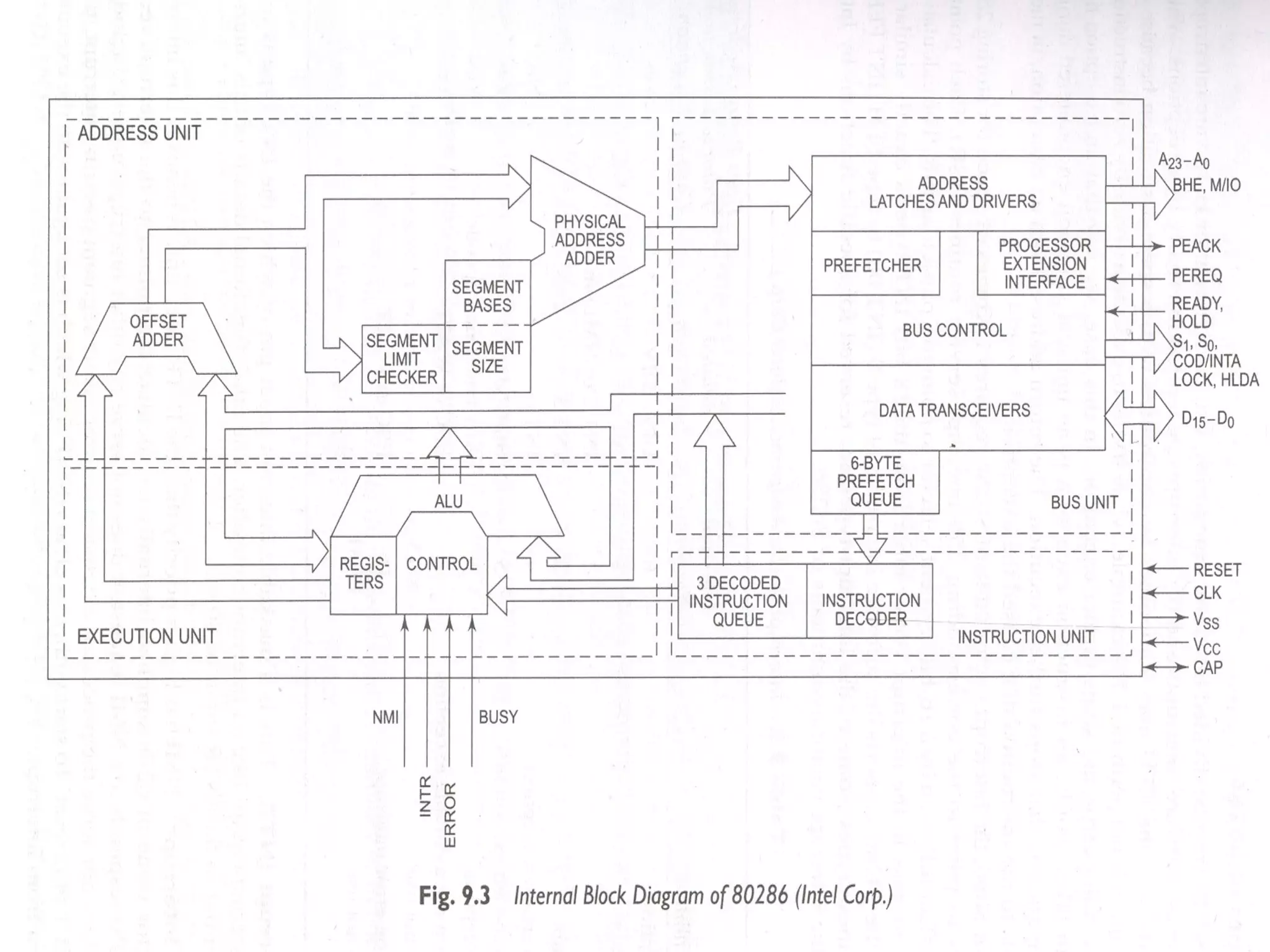

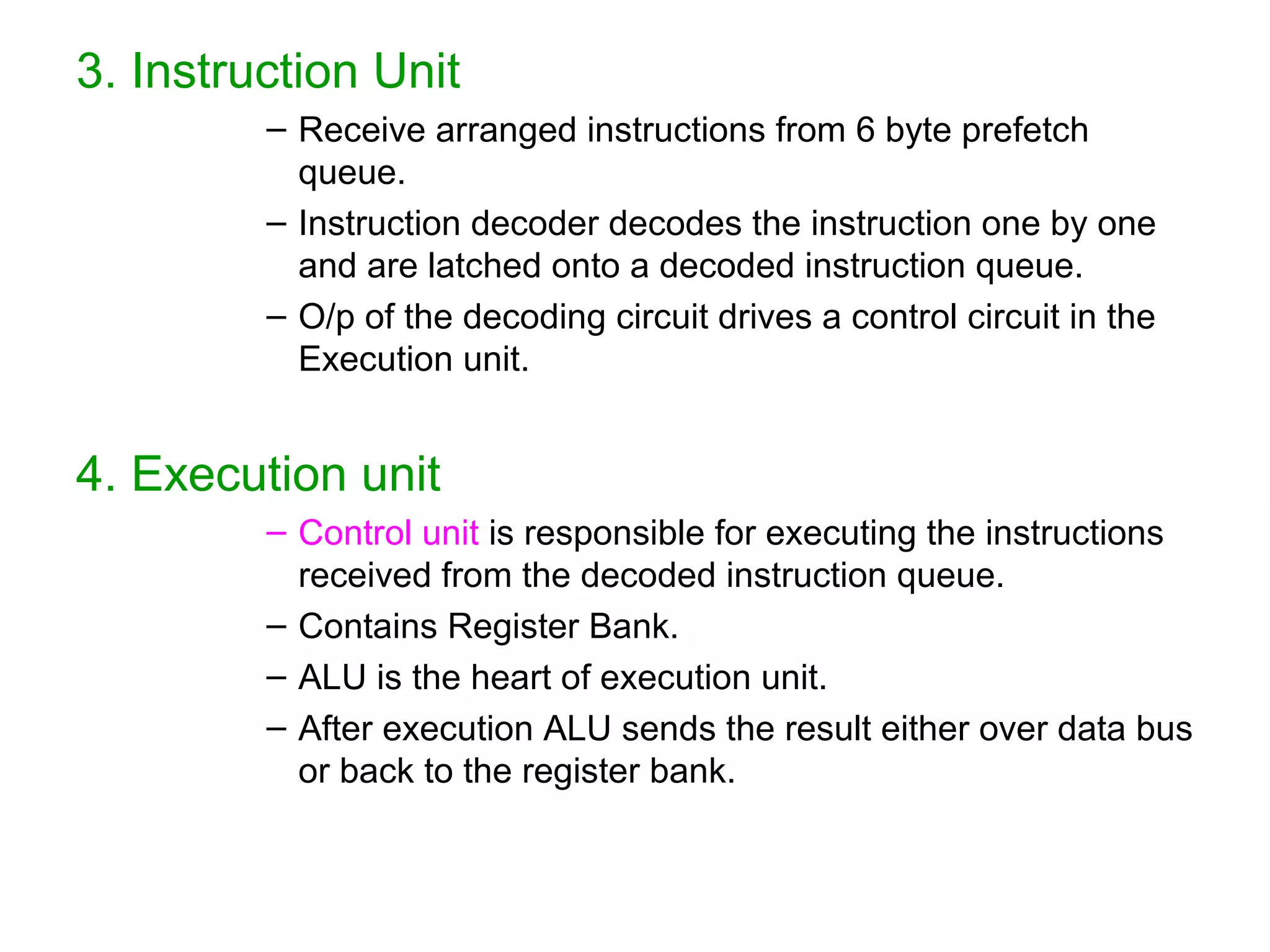

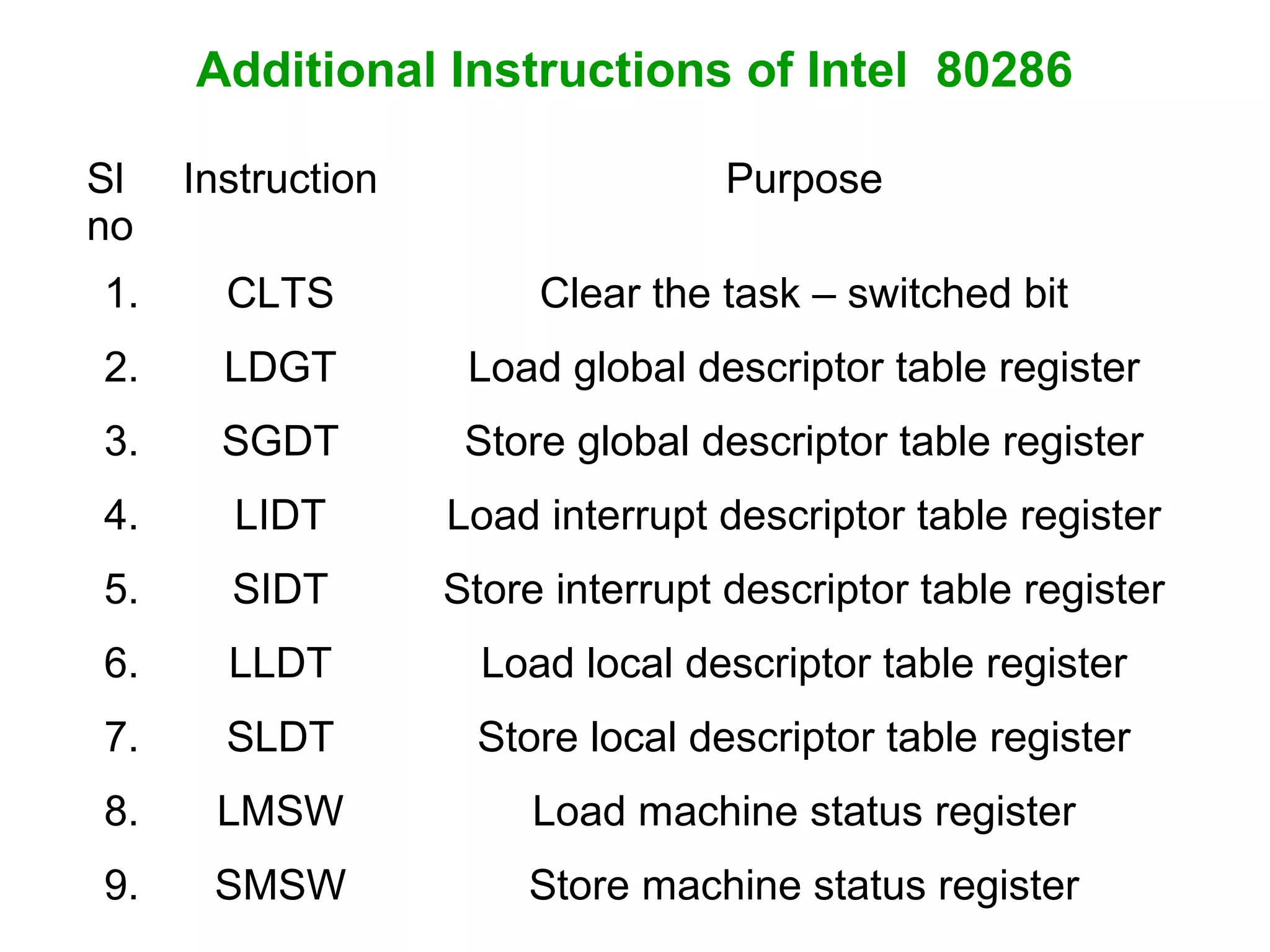

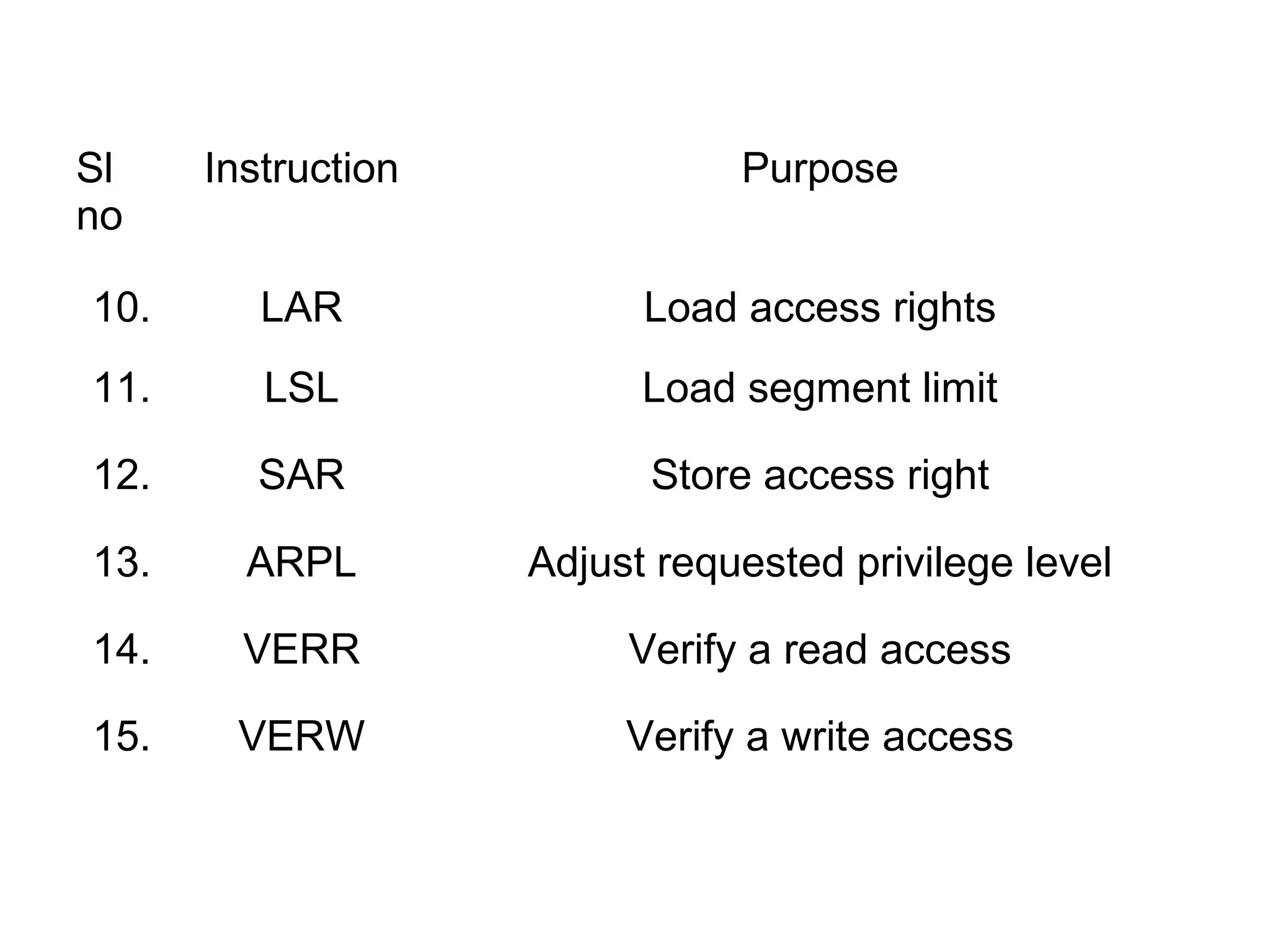

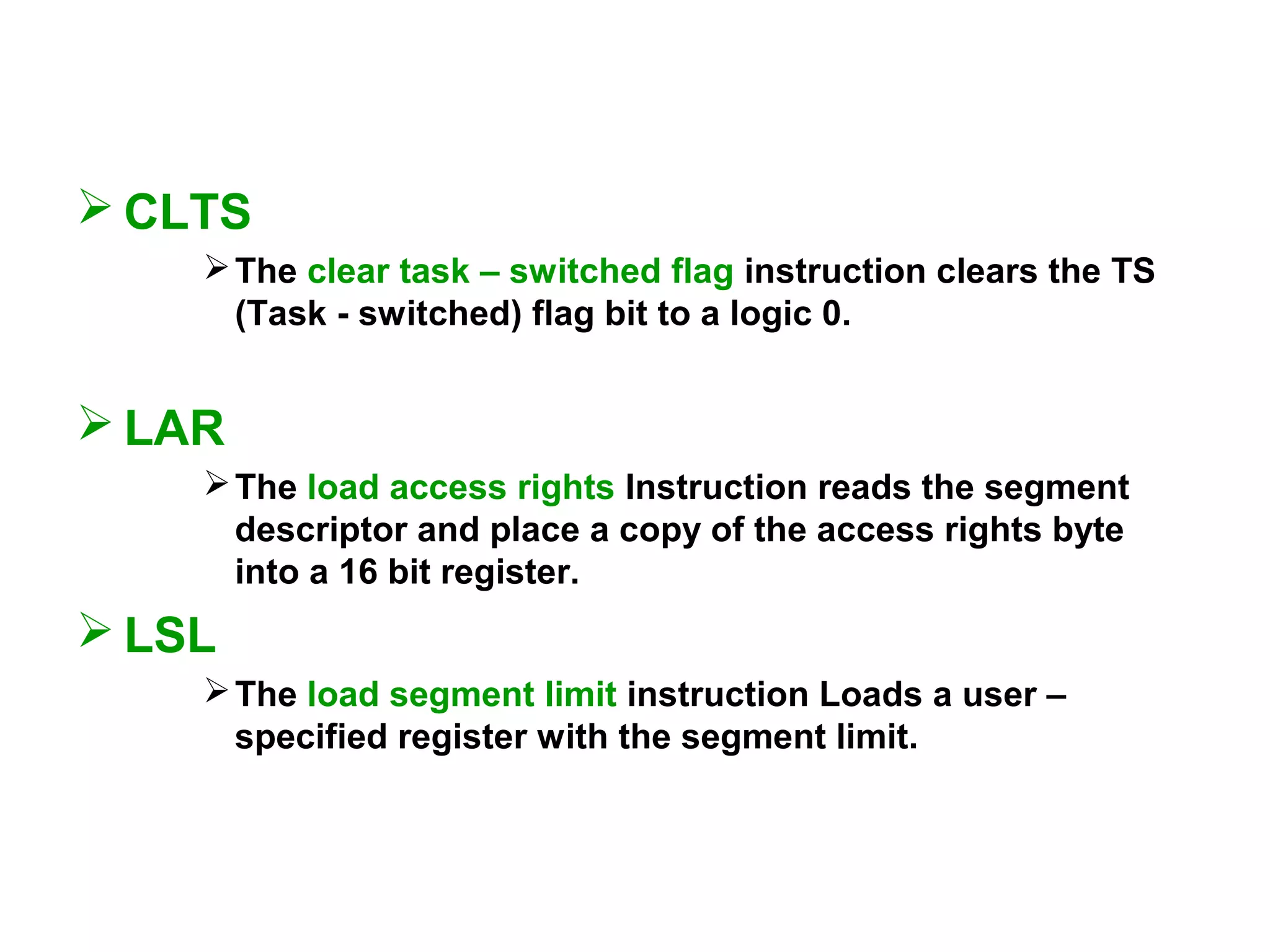

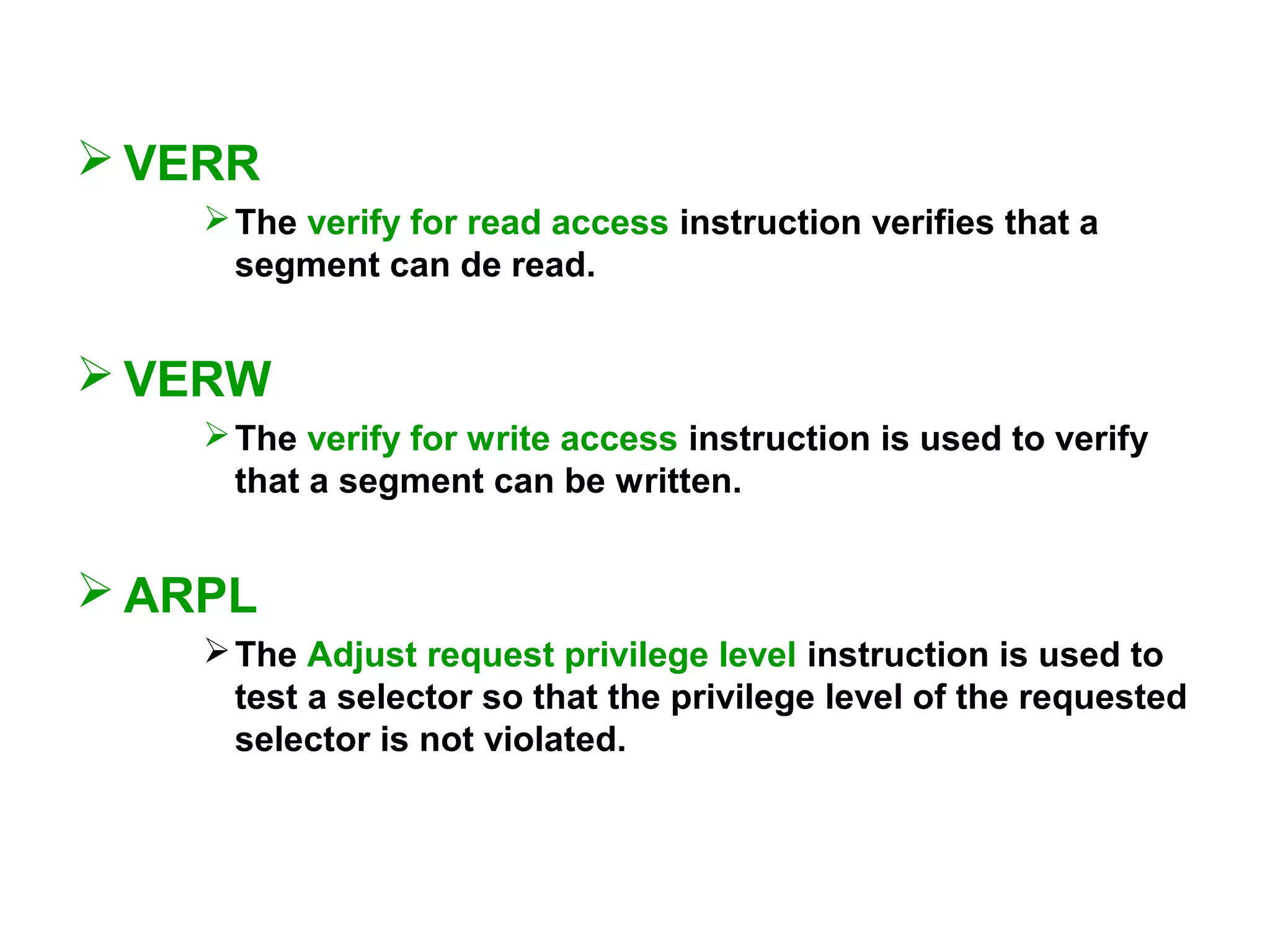

The Intel 80286 is the first microprocessor with memory management and protection abilities. It has a 16-bit data bus, 24-bit address bus, and can address up to 16MB of physical memory. Key features include virtual memory management, protection abilities through its integrated memory management unit, and two operating modes - real address mode and protected virtual address mode. The 80286 also introduced additional instructions for memory management and protection compared to earlier Intel processors.