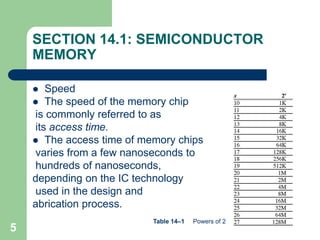

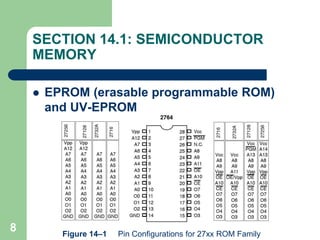

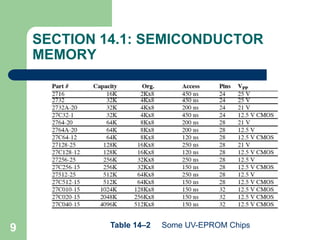

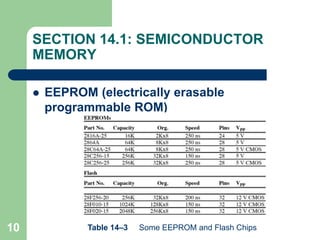

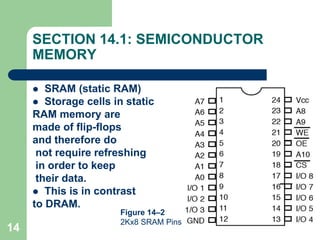

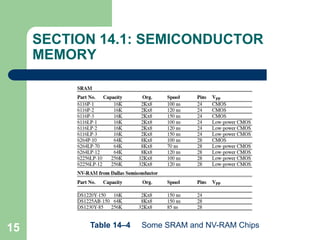

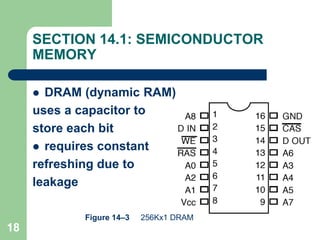

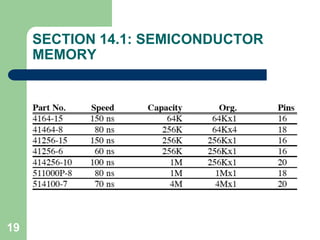

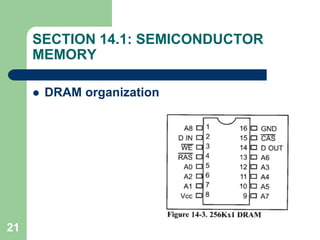

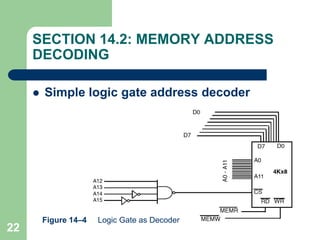

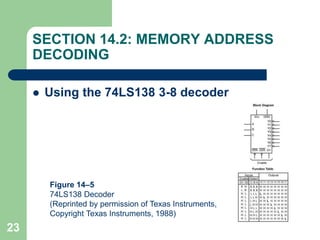

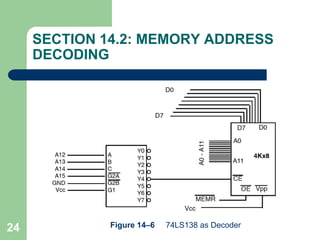

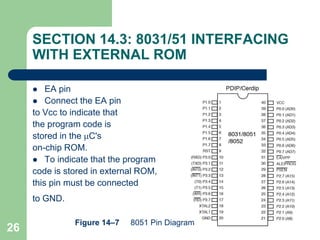

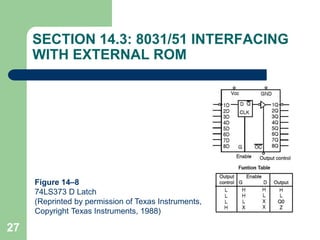

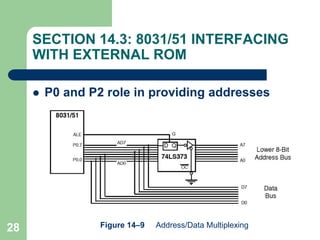

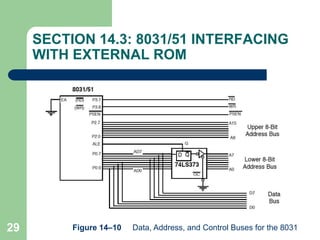

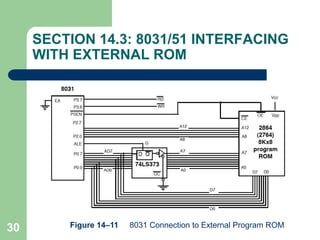

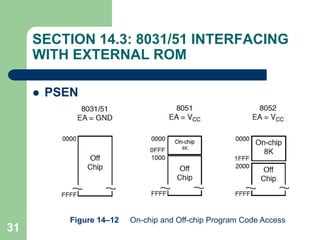

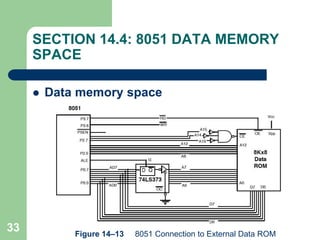

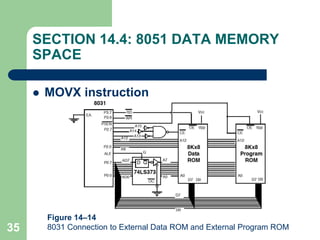

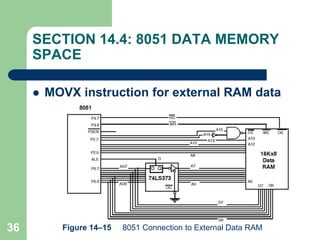

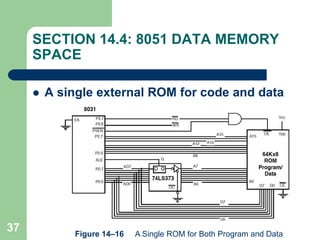

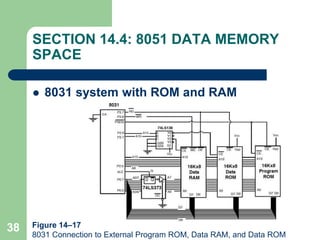

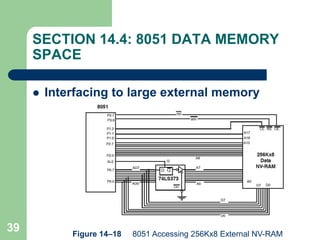

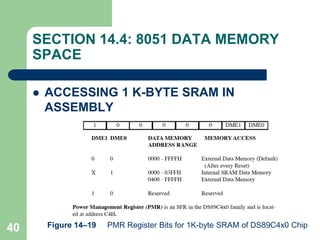

This document discusses interfacing the 8051 microcontroller to external memory. It covers different types of semiconductor memories like ROM, RAM, EEPROM, flash memory and their characteristics. It explains how the 8051 accesses external program ROM and data memory through address decoding, multiplexing address and data lines and using control signals like EA, PSEN and RD. Examples of interfacing circuits are shown to connect the 8051 to external ROM, RAM and large memory. Assembly code examples are provided to access 1Kbyte SRAM.