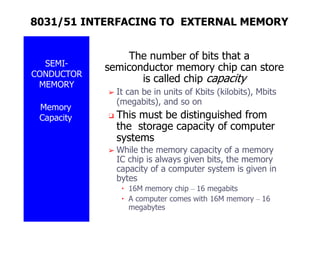

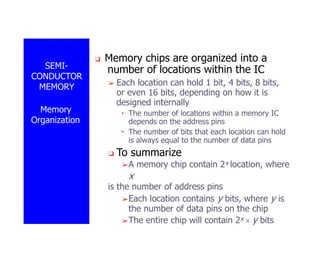

This document discusses different types of semiconductor memory, including ROM, RAM, and their variations. It explains key concepts like memory capacity, organization, speed, and checksum bytes. Specific memory types covered include PROM, EPROM, EEPROM, Flash memory, SRAM, DRAM, and mask ROM. The document provides examples to illustrate memory specifications like number of address pins, data pins, and capacity calculations.