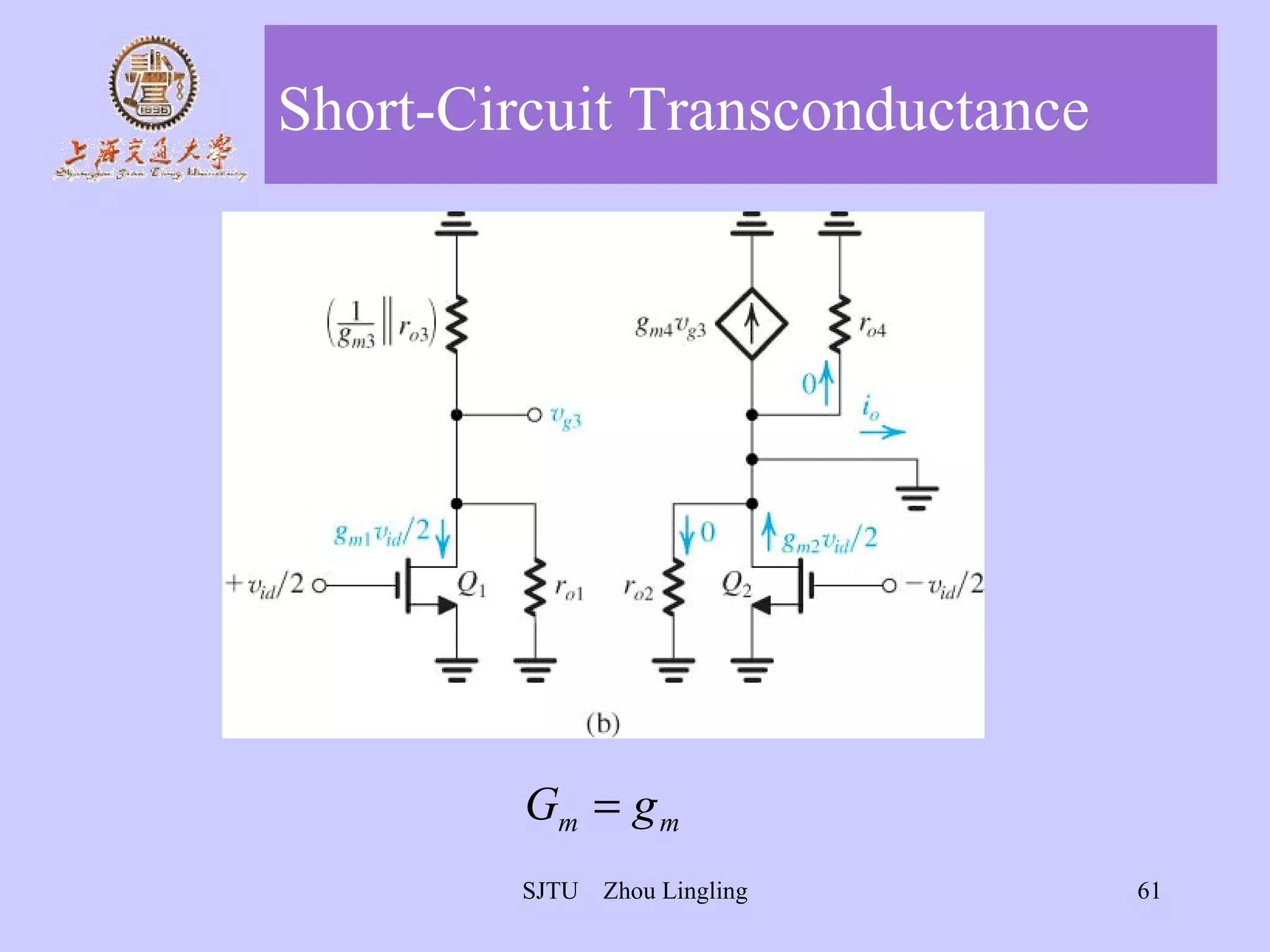

The document discusses differential amplifiers, including their advantages, basic operation, and analysis of key parameters like differential gain, common-mode gain, and common-mode rejection ratio. It covers both MOS and BJT-based differential pairs, examining their linear and nonlinear operation. It also describes techniques to improve performance, such as using active loads and converting the differential output to a single-ended output.