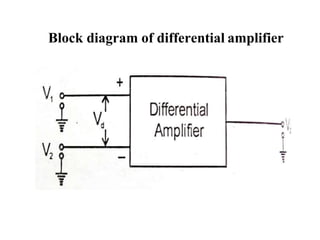

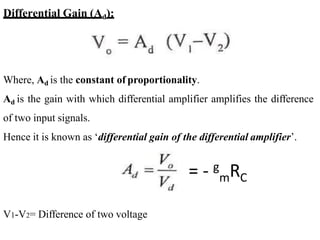

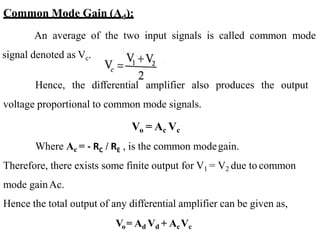

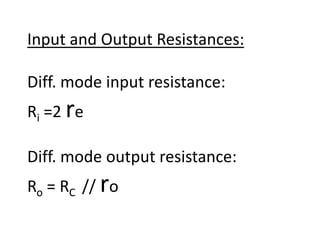

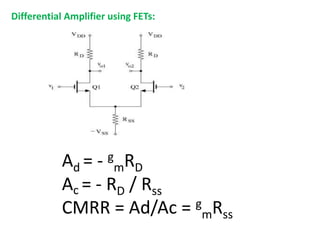

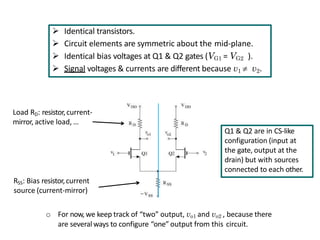

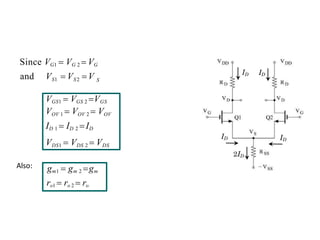

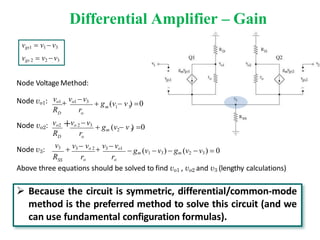

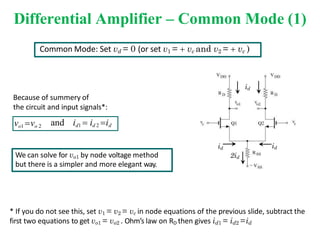

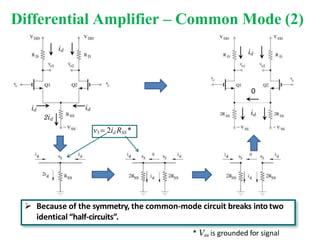

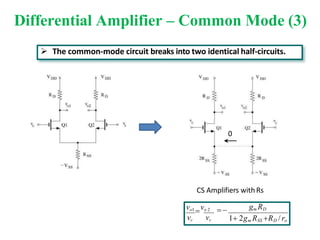

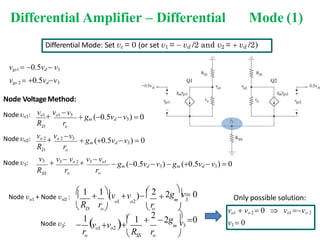

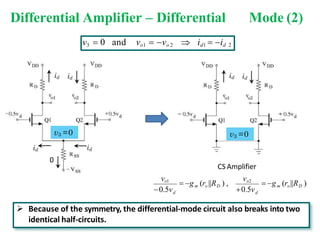

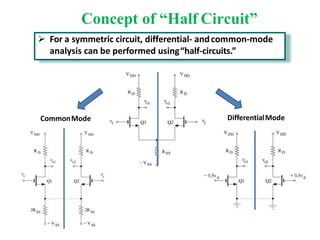

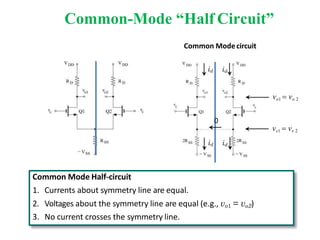

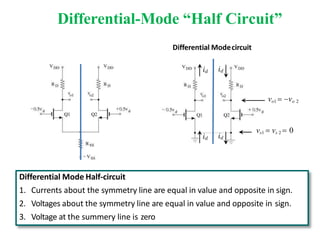

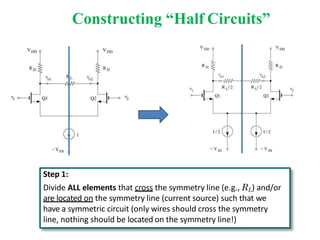

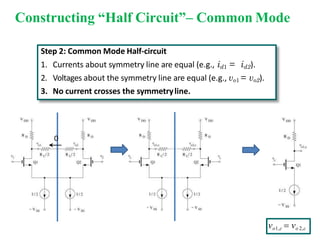

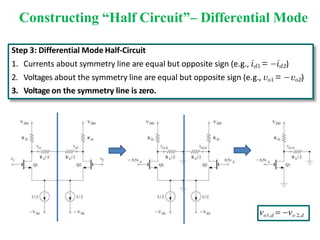

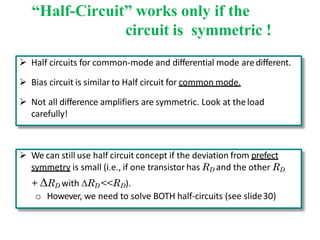

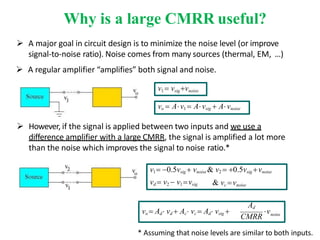

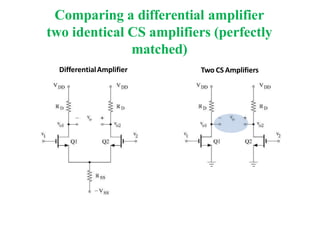

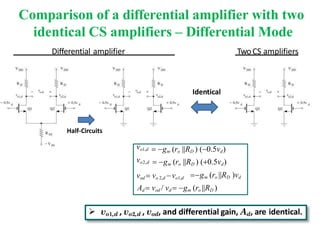

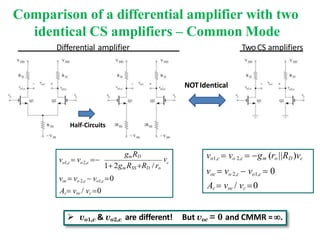

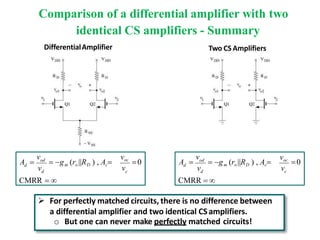

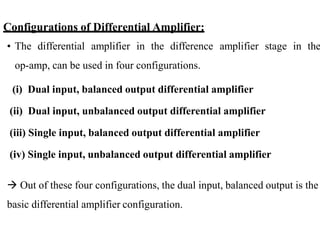

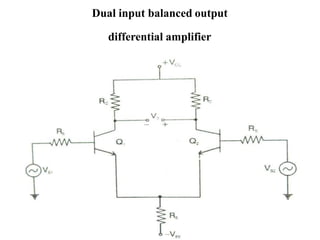

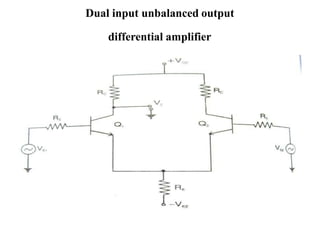

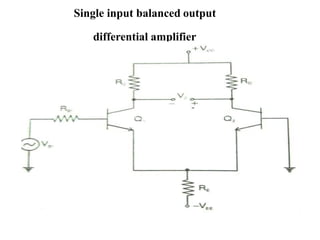

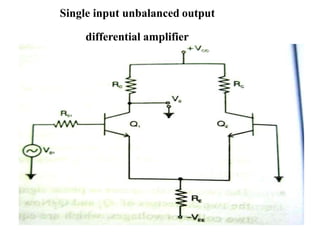

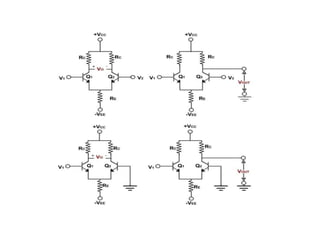

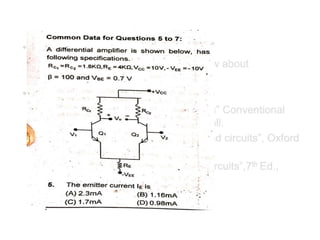

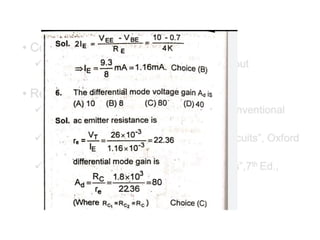

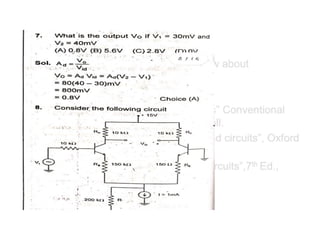

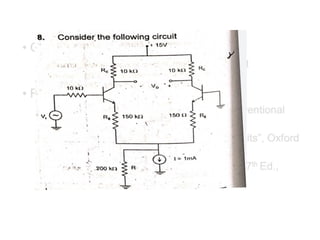

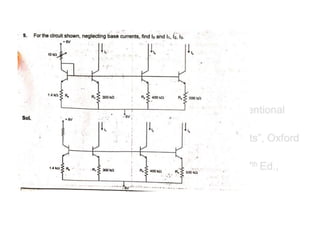

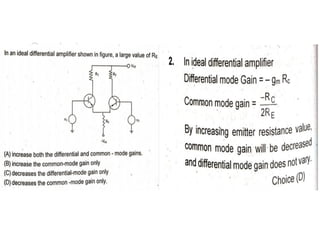

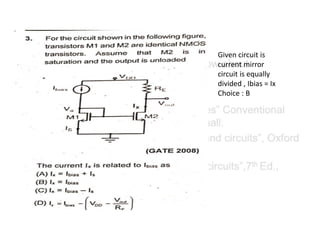

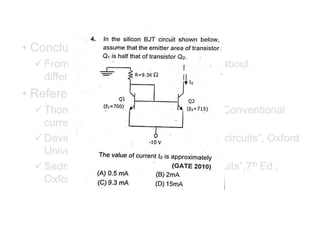

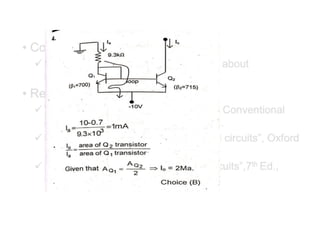

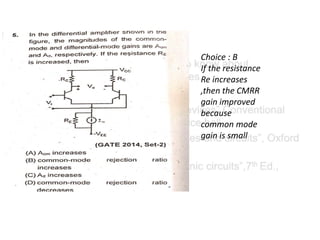

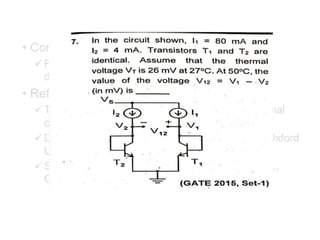

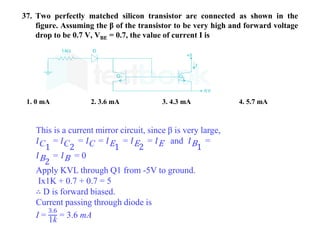

The document discusses differential amplifiers. It begins by defining a differential amplifier as a circuit that amplifies the difference between two input signals. It then provides block diagrams and equations showing how the differential amplifier output is proportional to the difference of the two inputs. The document discusses concepts such as differential gain, common mode gain, common mode rejection ratio, and input and output resistances. It provides examples of differential amplifiers using field-effect transistors and discusses their operation. Finally, it compares a differential amplifier to two identical common-source amplifiers and discusses various configurations of differential amplifiers.