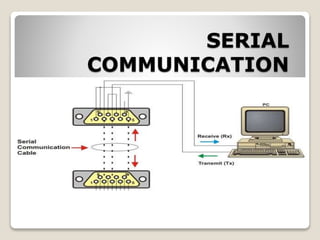

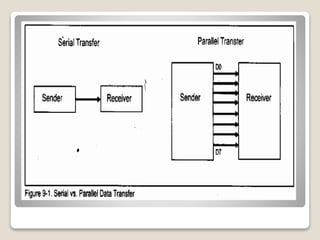

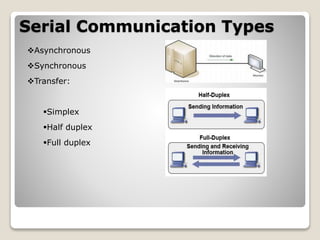

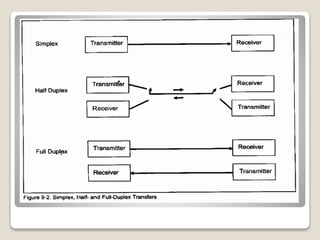

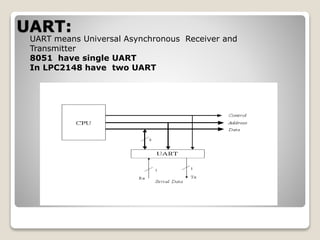

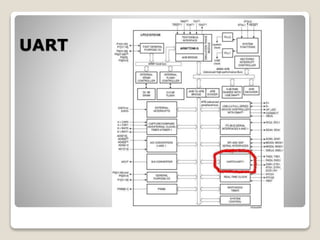

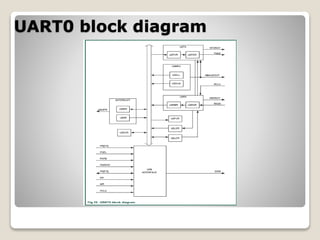

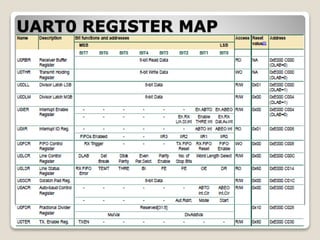

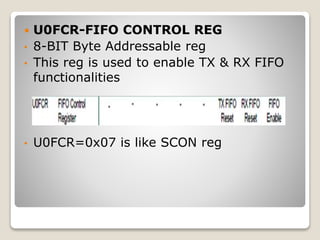

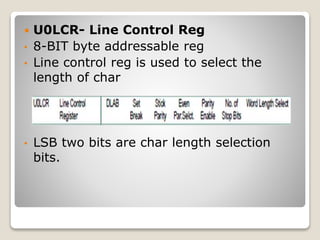

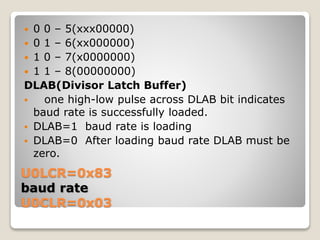

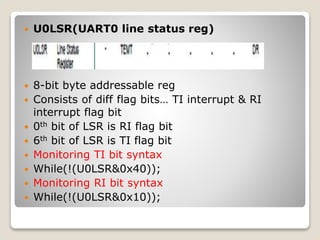

The document discusses serial communication and UART in LPC2148 microcontroller. It describes that serial communication transmits data one bit at a time over one line, compared to parallel which uses multiple lines. It then explains the different types of serial communication and provides details about the UART block and registers in LPC2148 used for serial communication like UART0, its pin descriptions, register map including FIFO control, line control, divisor latch, transmit/receive buffers and line status registers.