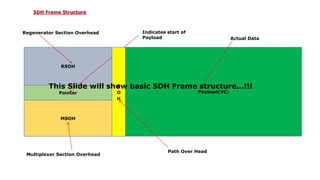

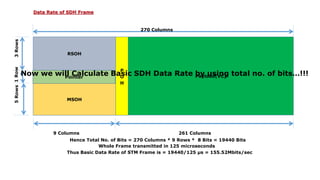

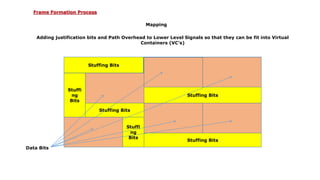

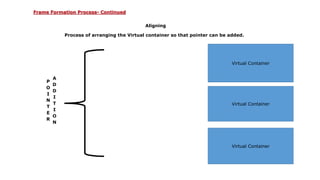

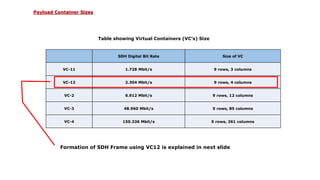

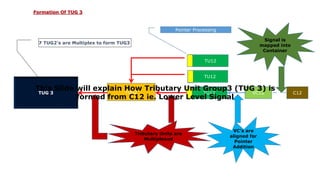

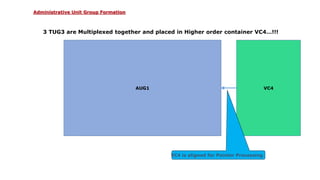

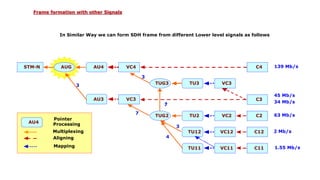

The document discusses the frame structure of Synchronous Digital Hierarchy (SDH). It explains that an SDH frame is transmitted every 125 microseconds and contains 9 rows and 270 columns of bytes for a total of 19,440 bits. This equates to a basic data rate of 155.52 megabits per second. The frame contains sections for regenerator and multiplexer section overhead as well as a payload area. Lower level signals can be mapped and multiplexed into the payload area through a process that includes mapping, aligning, pointer processing and multiplexing.