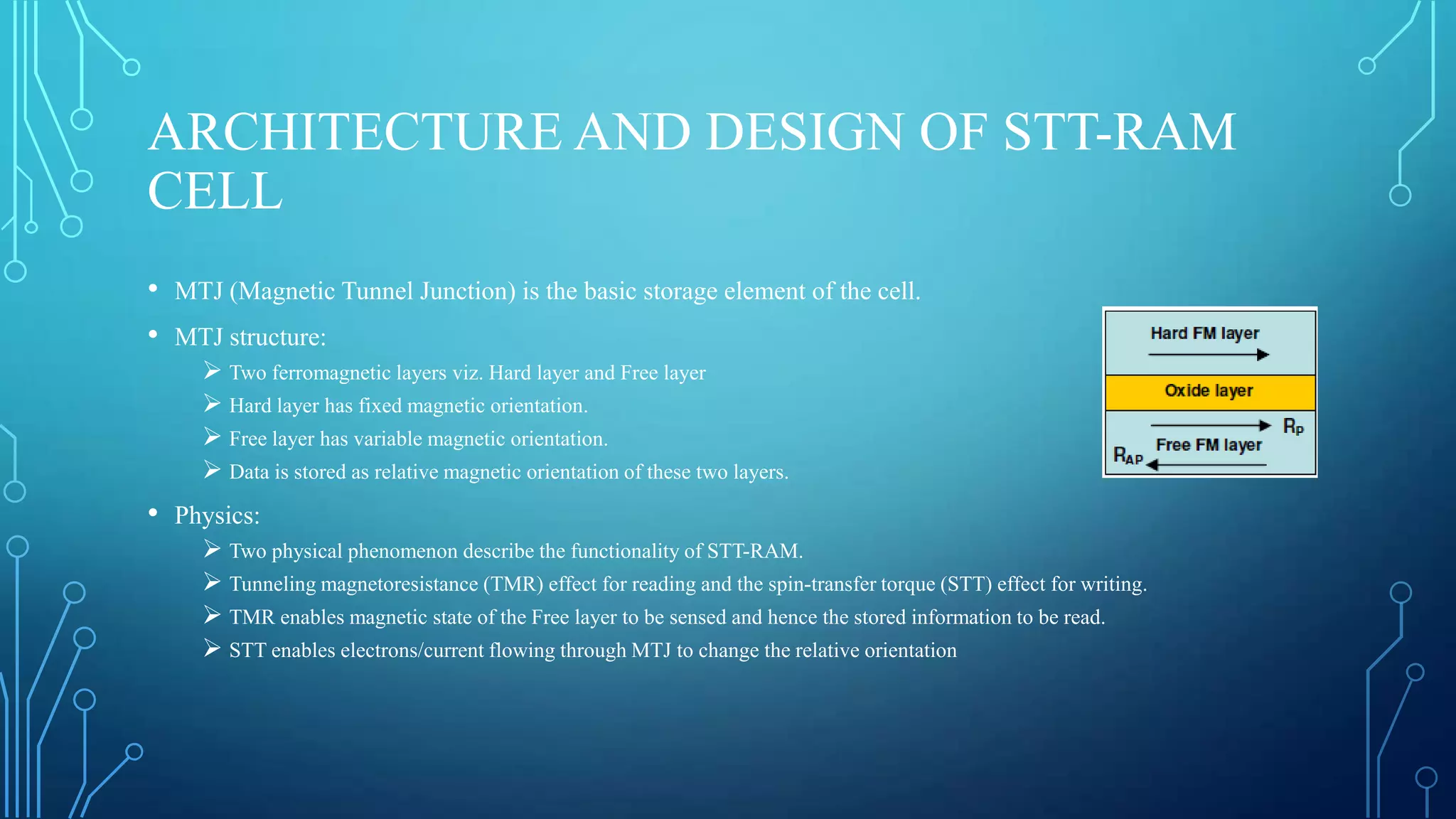

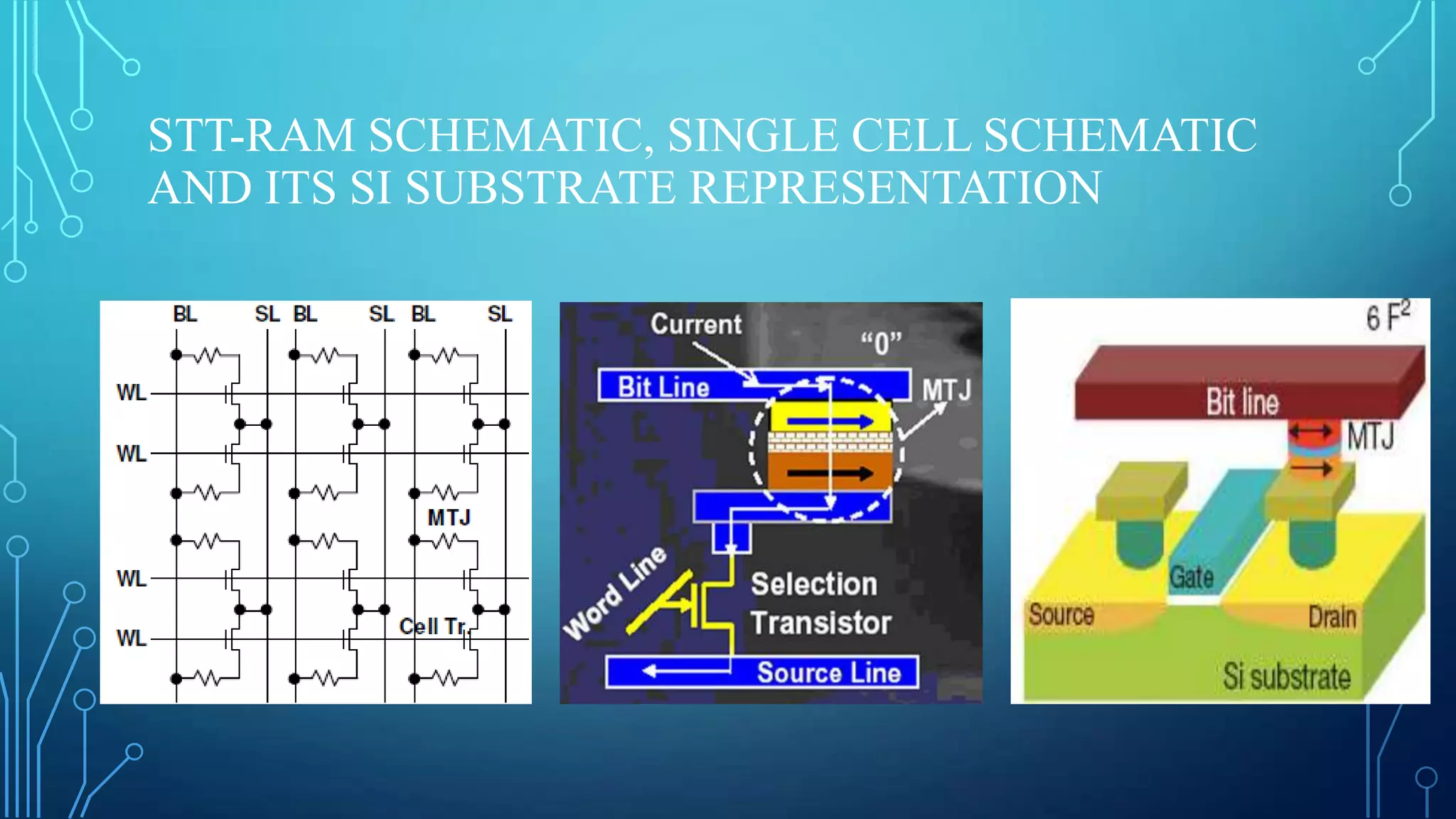

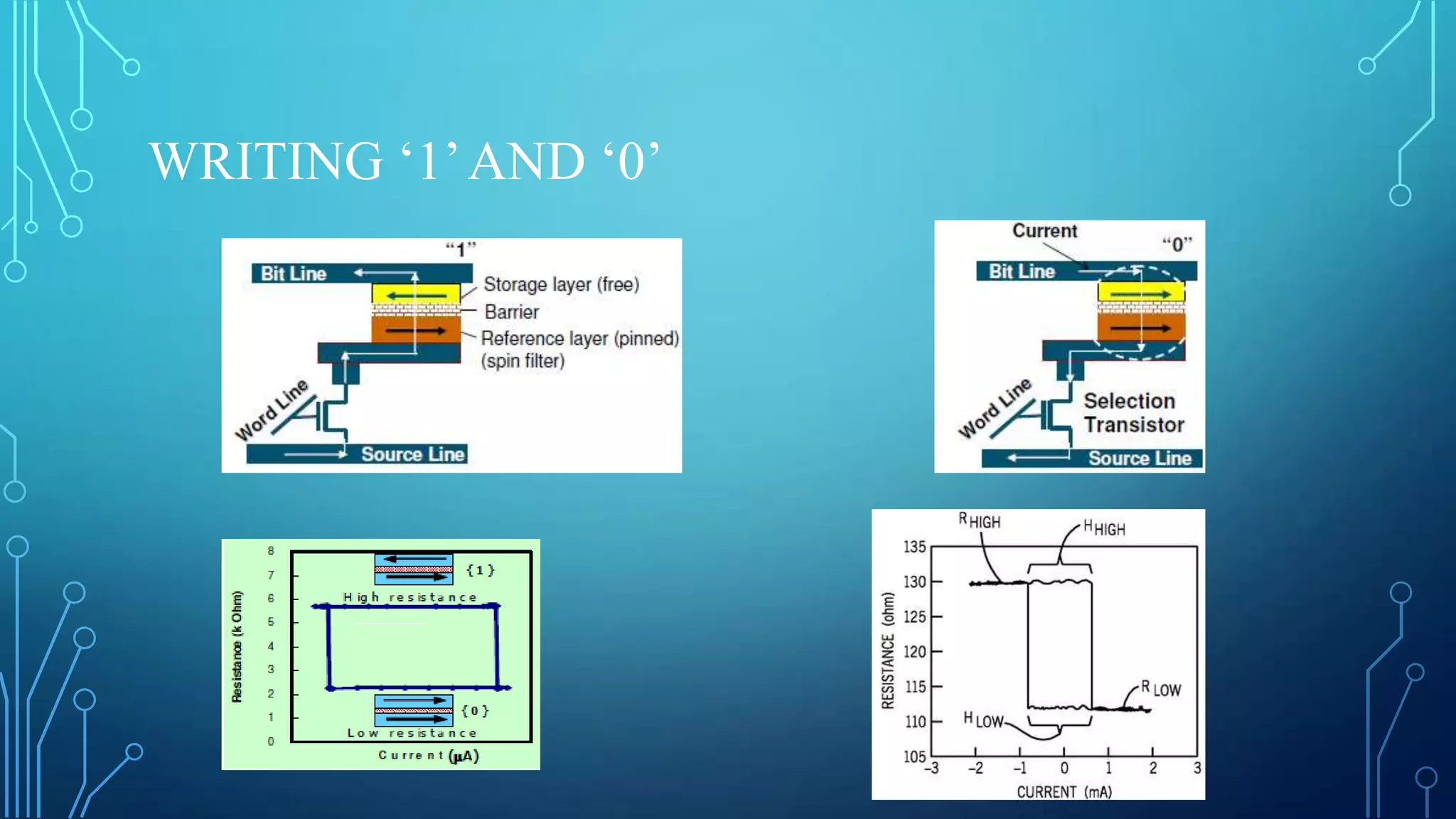

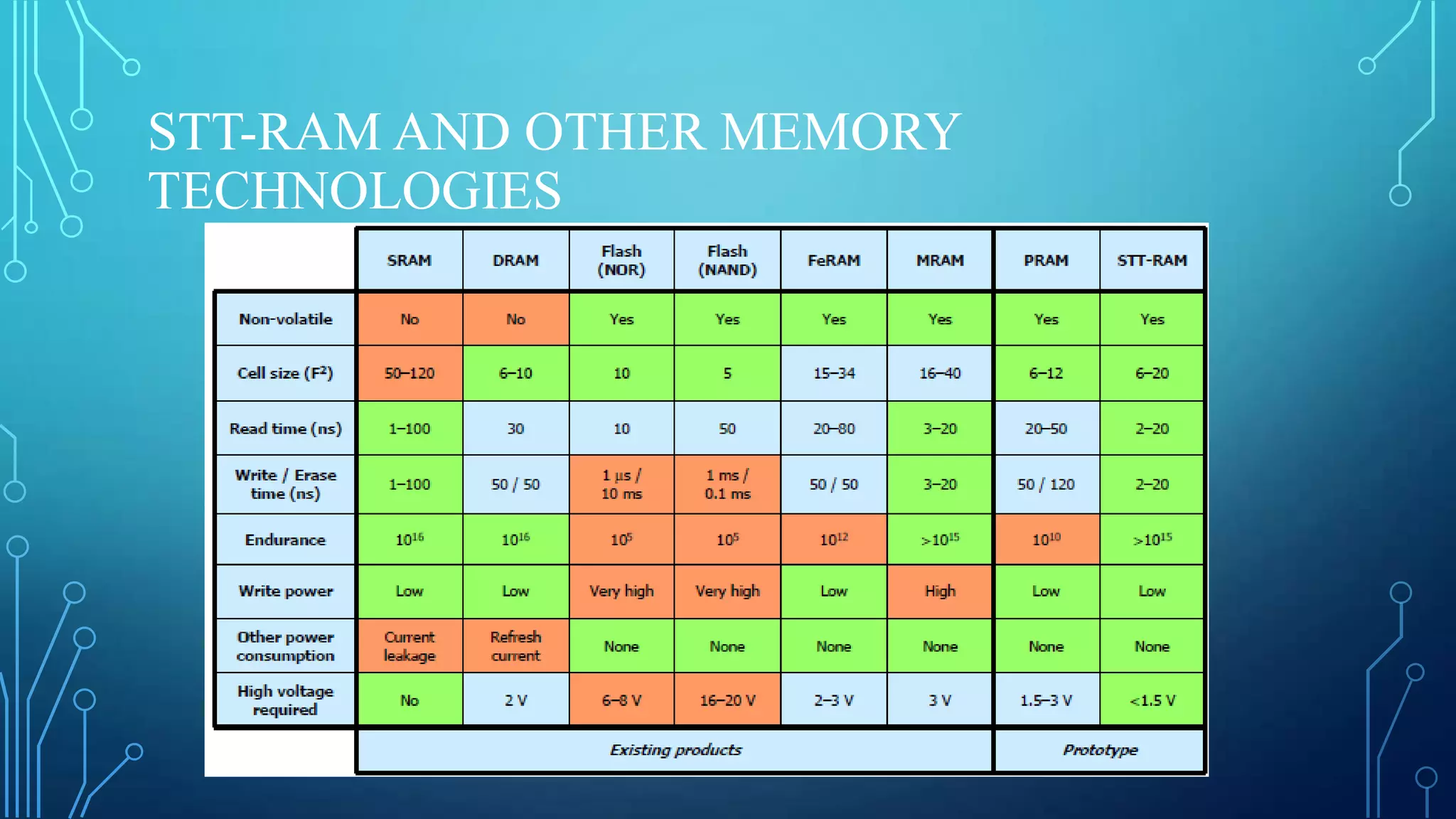

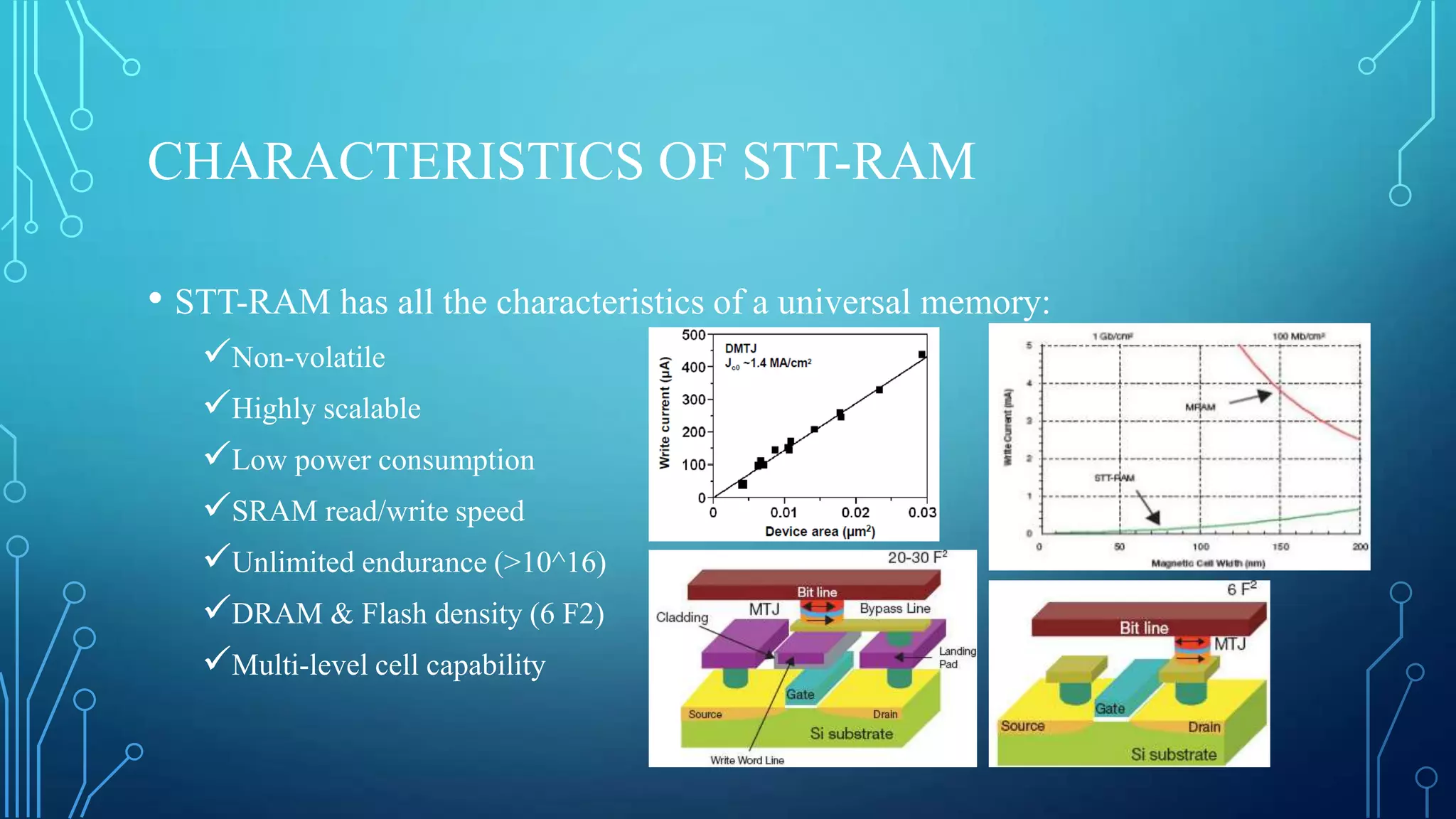

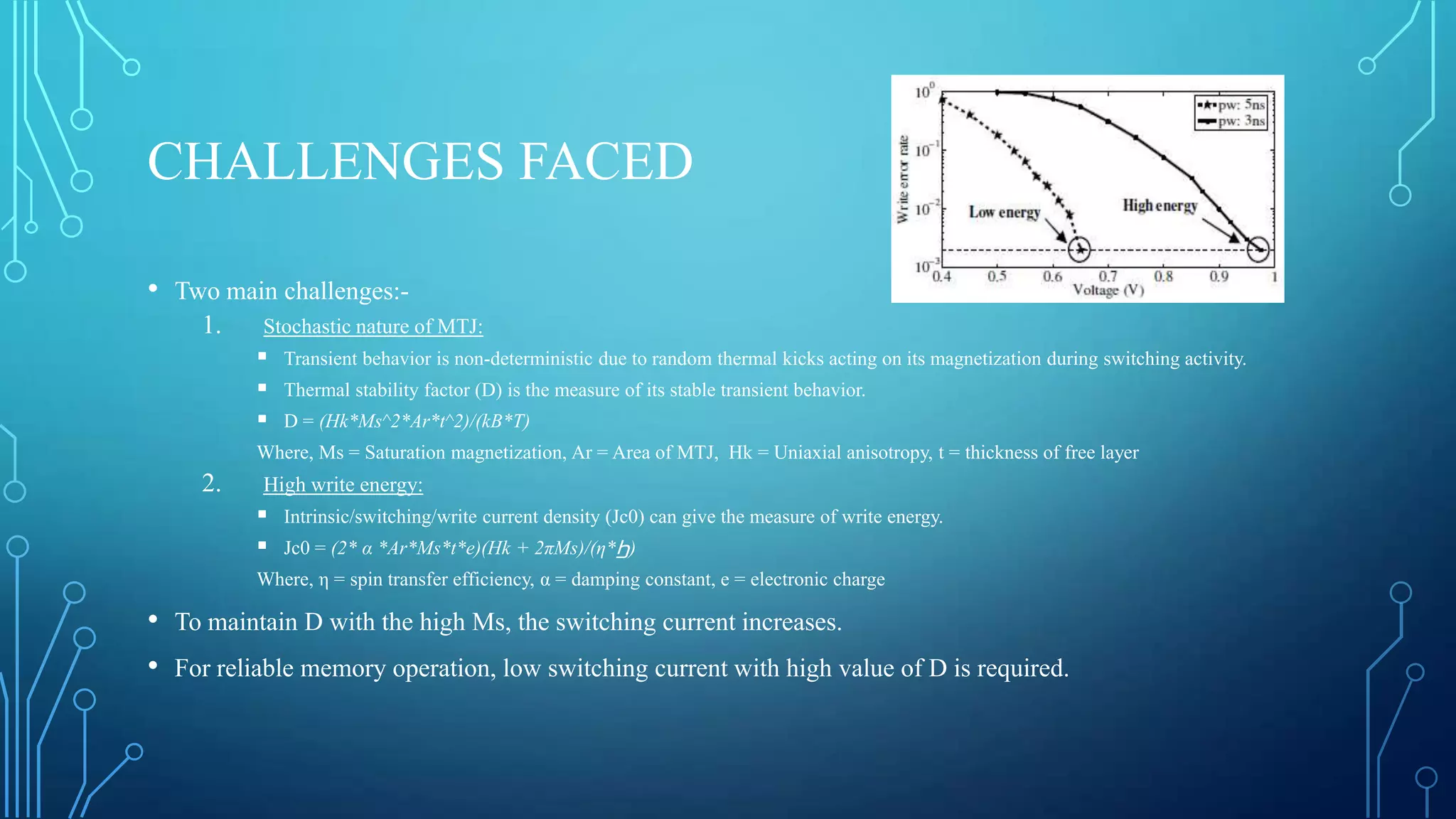

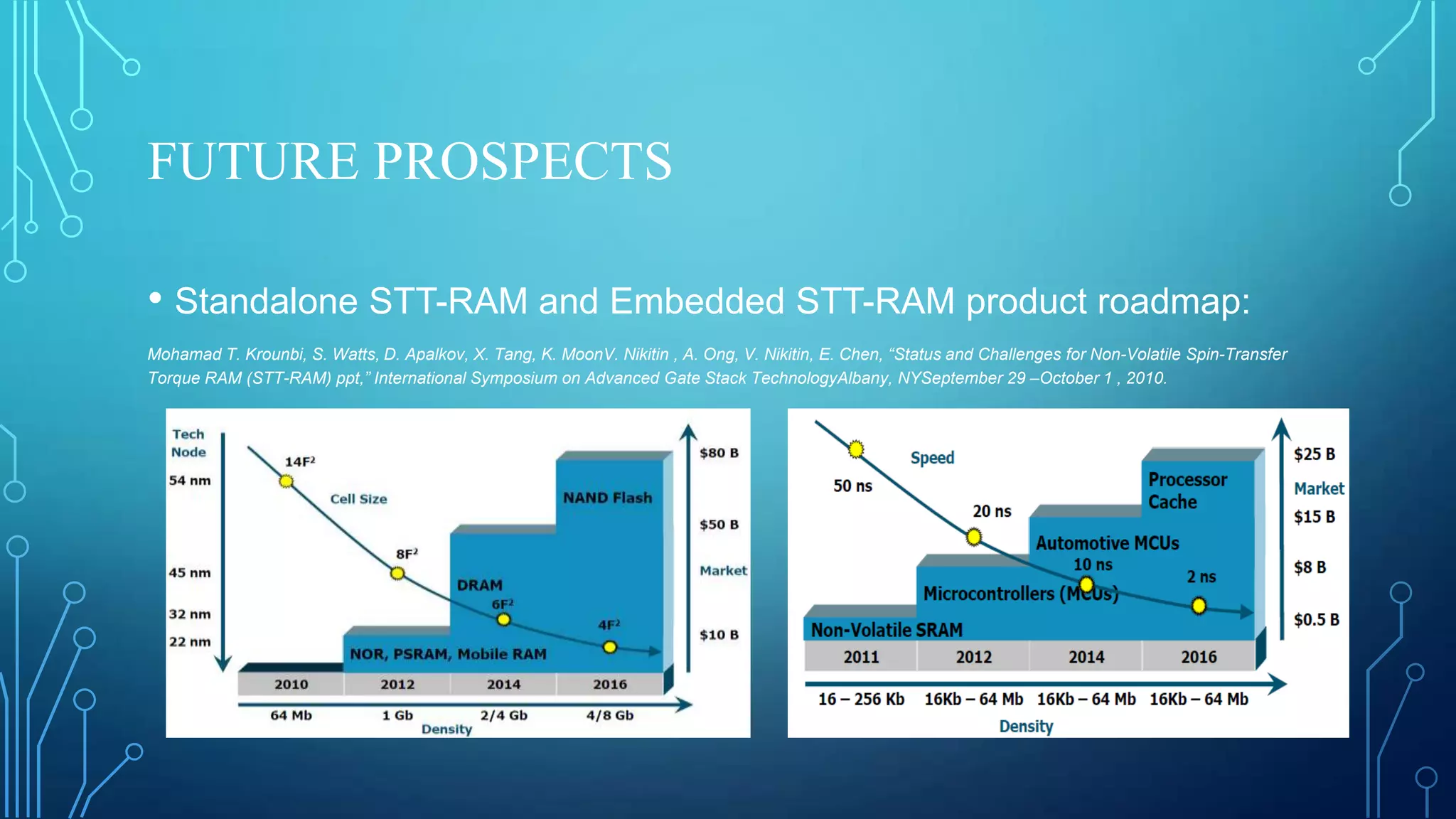

This document discusses STT-RAM (Spin Transfer Torque Random Access Memory) as a potential new memory technology. It provides an overview of STT-RAM, including its basic components and operation. STT-RAM has characteristics that could allow it to replace existing memory technologies. However, maintaining thermal stability while reducing write energy is a key challenge. Recent research has proposed techniques to improve STT-RAM's performance and energy efficiency to help address this challenge and bring STT-RAM closer to being a universal memory.