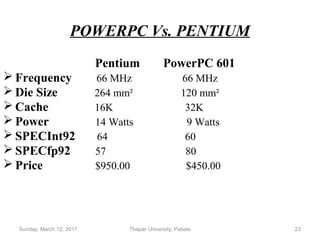

The document provides a detailed overview of the PowerPC microprocessor architecture developed by IBM, highlighting its origins, features, and various generations. It explains the architecture's design, supported modes, pipelining, execution units, and power management. Additionally, it compares the PowerPC with the Pentium processor in terms of specifications like frequency, die size, and performance.