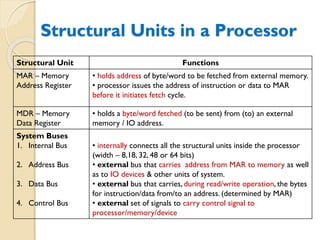

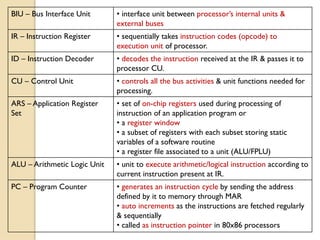

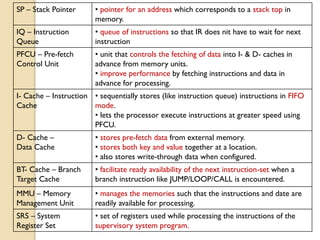

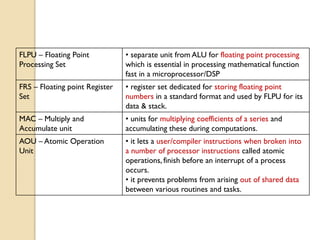

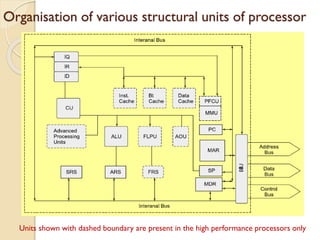

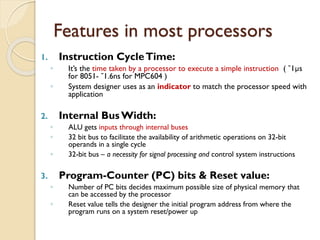

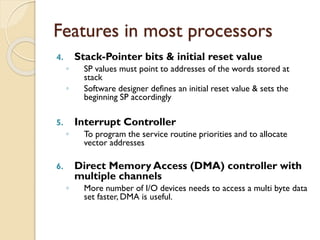

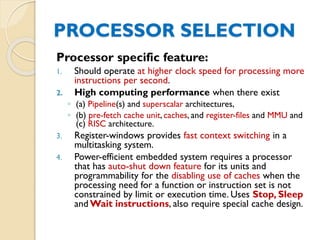

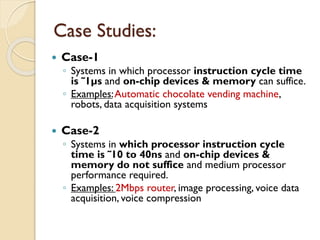

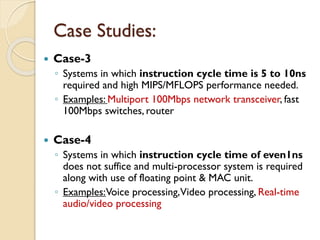

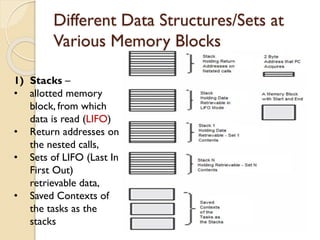

This document discusses processor and memory organization for embedded systems. It describes the structural units of a processor like the MAR, MDR, buses, BIU, IR, ID, CU, ALU, PC, and caches. It covers memory devices like ROM, RAM, SRAM, DRAM, and flash memory. It provides case studies on selecting a processor based on features like clock speed, performance needs, and power efficiency. The document aims to help with selecting appropriate processors and memory for different types of embedded systems.