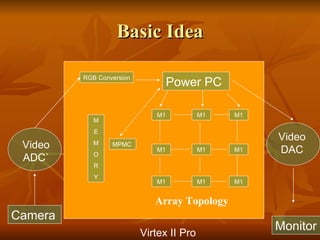

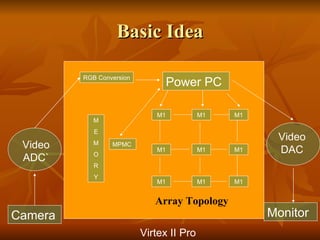

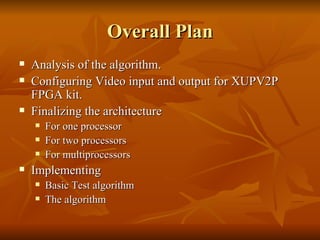

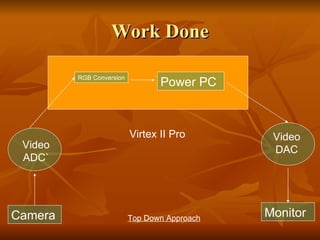

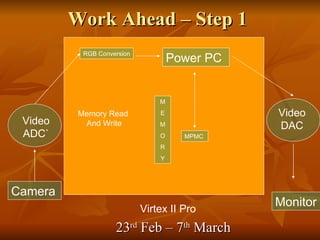

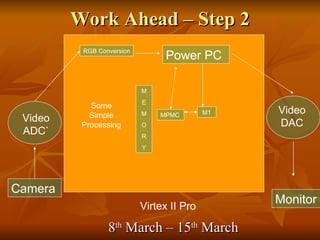

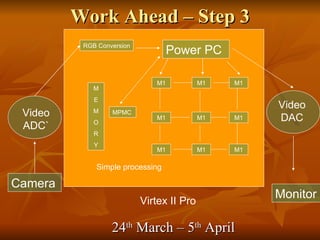

The document discusses the design of a soft core multiprocessor architecture on an FPGA to implement an adaptive background mixture model algorithm for motion segmentation in images. The goals are to learn FPGA design, leverage parallelism for real-time processing, and use a multiprocessor approach to process different image regions simultaneously. Each processor will perform the algorithm on a sub-region of the image in parallel. They will communicate via shared external memory and FIFO-based links. The proposed architecture includes multiple MicroBlaze processors connected in an array topology to process images from a video camera in real-time.

![Inter-processor Communication [12] For transferring large chunks of image data, we will be using shared external DDR Ram as It provides large memory space for storing multiple frames. Multiple processors can access the RAM simultaneously using MPMC. For sharing intermediate computation results we will use FSL Links between neighboring processors. Unidirectional point-to-point communication. Unshared non-arbitrated communication mechanism. FIFO based communication.](https://image.slidesharecdn.com/minip-090227004740-phpapp02/85/Multiprocessor-Architecture-for-Image-Processing-8-320.jpg)

![Network Topology [1] Completely meshed: Each node is connected to all other nodes. Adv: Reduce inter processor communication time. Disadvantage: Max 9 processors possible. Ring Network : Star Network Array Network: (our choice)](https://image.slidesharecdn.com/minip-090227004740-phpapp02/85/Multiprocessor-Architecture-for-Image-Processing-9-320.jpg)

![Work Done Studied Background mixture Model for foreground subtraction algorithm [2], [3] , as a case study. Analysis of the algorithm for: Parallelism exploitation Length of code for implementation Memory requirements to store data. Feasibility](https://image.slidesharecdn.com/minip-090227004740-phpapp02/85/Multiprocessor-Architecture-for-Image-Processing-11-320.jpg)

![Work Done Studied Microblaze architecture. [4] Studied FSL Link [5] PLB, LMB, OPB Buses [6] XPS Design Flow [7] Literary survey on related works [8],[9], [10], [11] Configuration Video input and output for XUPV2P FPGA kit. Bottom Up Approach](https://image.slidesharecdn.com/minip-090227004740-phpapp02/85/Multiprocessor-Architecture-for-Image-Processing-13-320.jpg)

![Related Works Design Development and performance evaluation of multiprocessor system on FPGA. Somen Barma, CSE IITD. [8]. A Microblaze based Multiprocessor SoC[1] An FPGA based soft multiprocessor system for IPv4 packet forwarding. [9] An automated framework for FPGA based soft Multiprocessor System. [10] Multiprocessor interconnection based on DMA for FPGA.[11]](https://image.slidesharecdn.com/minip-090227004740-phpapp02/85/Multiprocessor-Architecture-for-Image-Processing-19-320.jpg)

![REFERENCES [1] A Microblaze based Multiprocessor SOC – 2003 [2] Adaptive background mixture model for real-time tracking – 1999 [3] Understanding background mixture model for foreground segmentation – 2002 [4] Microblaze processor reference guide [5] Xilinx FSL datasheet [6] Xilinx Microblaze bus interface (ppt) [7] Virtex II Pro design flow – getting started [8] Design Development and performance evaluation of multiprocessor system on FPGA. Somen Barma, CSE IITD. Under Prof Kolin Paul [9] An FPGA based soft multiprocessor system for IPv4 packet forwarding. [10] An automated framework for FPGA based soft Multiprocessor System. [11] Multiprocessor interconnection based on DMA for FPGA. [12] XPS White paper – Designing multiprocessor System on Platform Stdio. Visit www.cse.iiitd.ernet.in/~ee5060412](https://image.slidesharecdn.com/minip-090227004740-phpapp02/85/Multiprocessor-Architecture-for-Image-Processing-20-320.jpg)