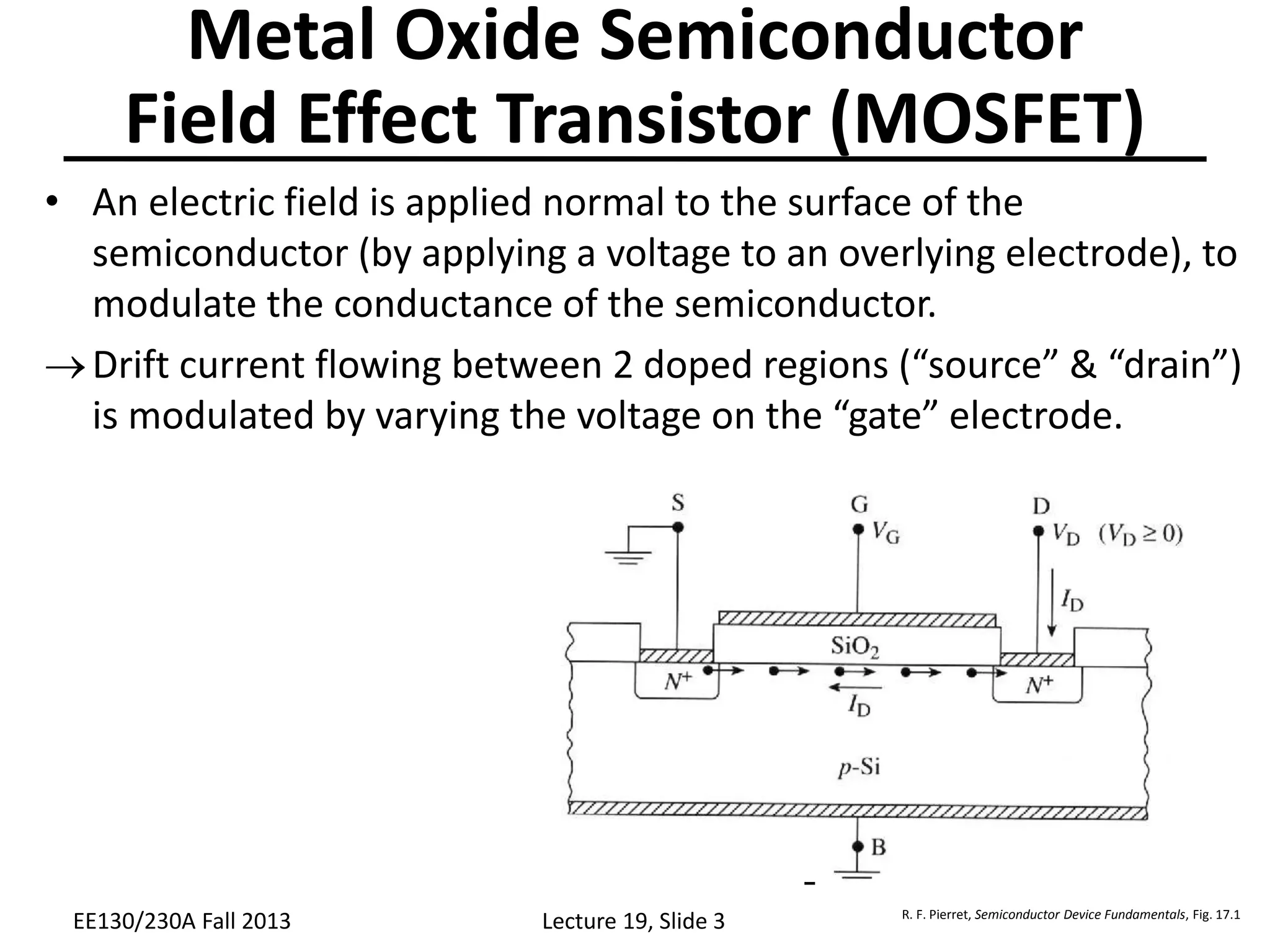

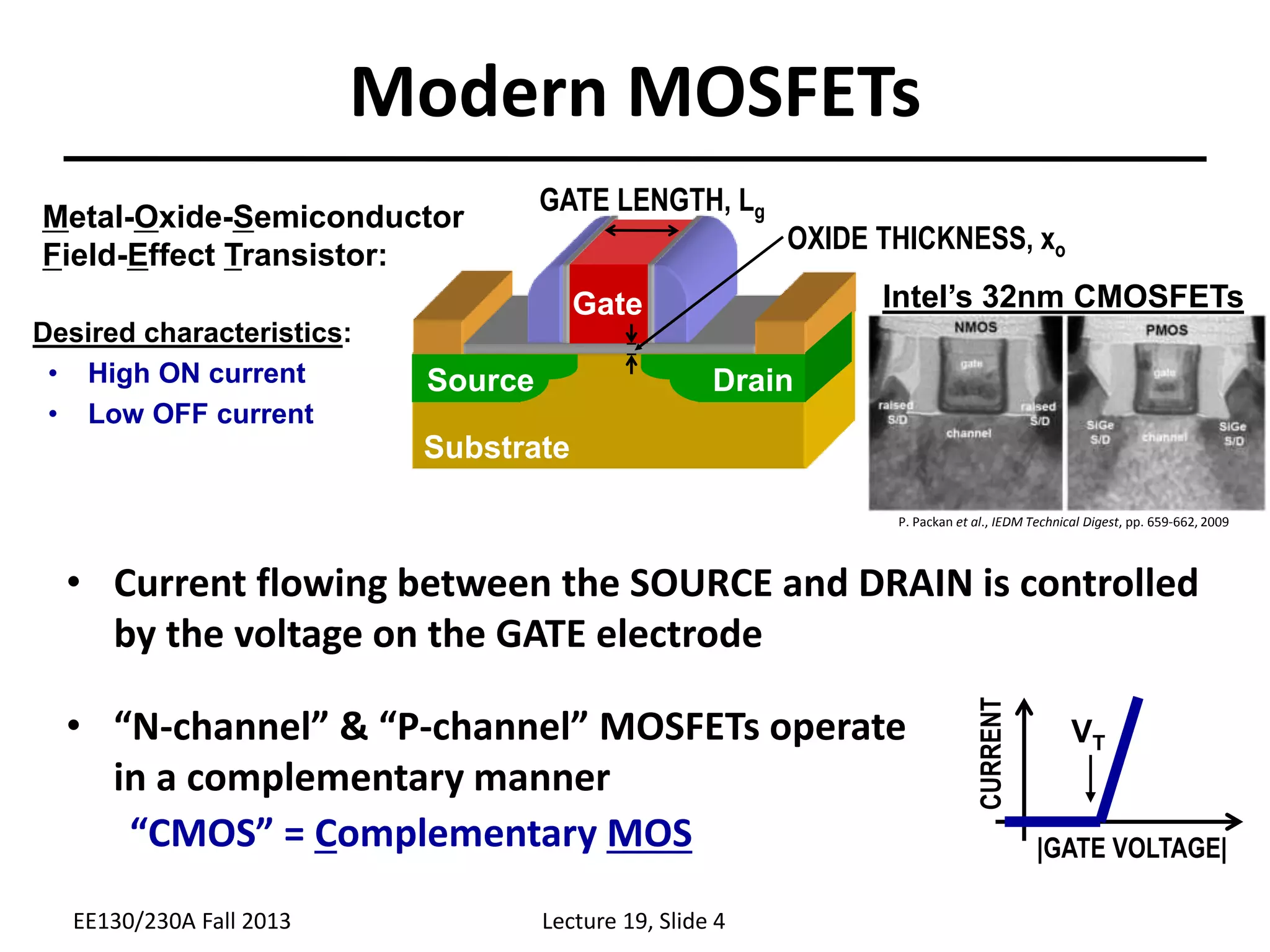

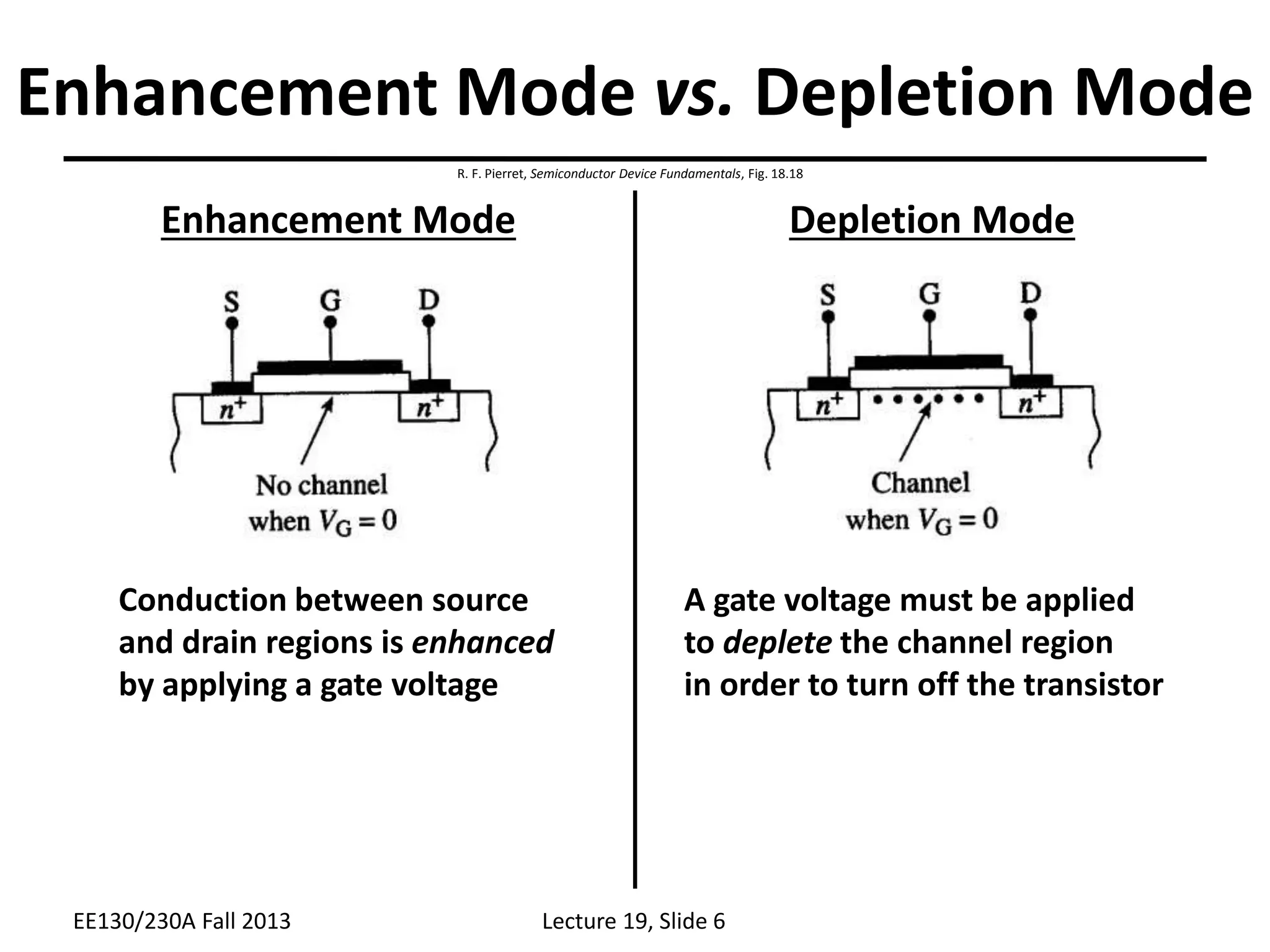

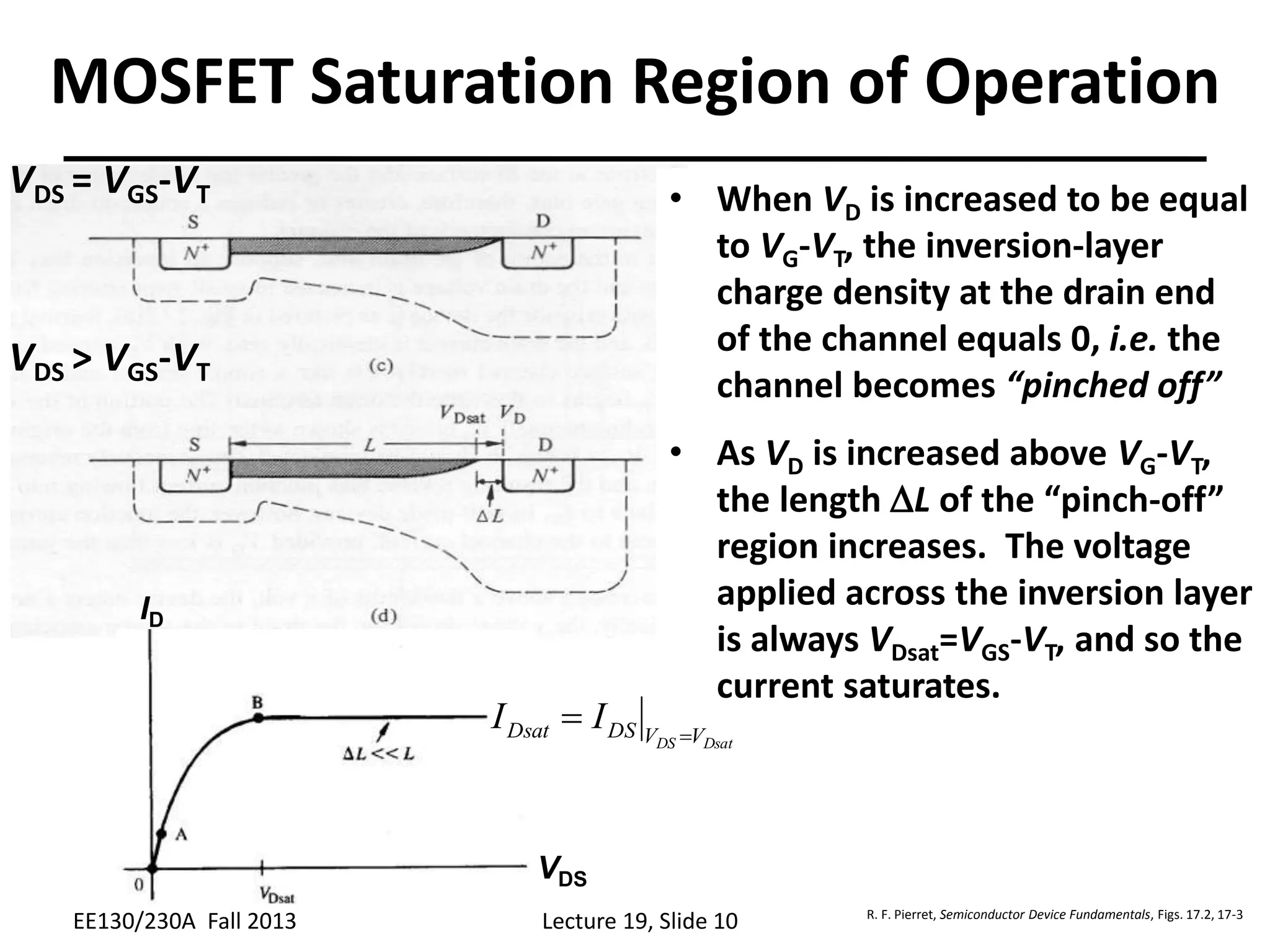

The document discusses the structure and operation of the metal-oxide-semiconductor field-effect transistor (MOSFET). It describes how a MOSFET works by using an electric field applied perpendicular to the semiconductor surface to modulate the conductance between the source and drain regions. The document outlines the qualitative theory of MOSFET operation and compares enhancement mode versus depletion mode. It also discusses N-channel versus P-channel MOSFETs and how they are used in complementary MOS (CMOS) devices and circuits.