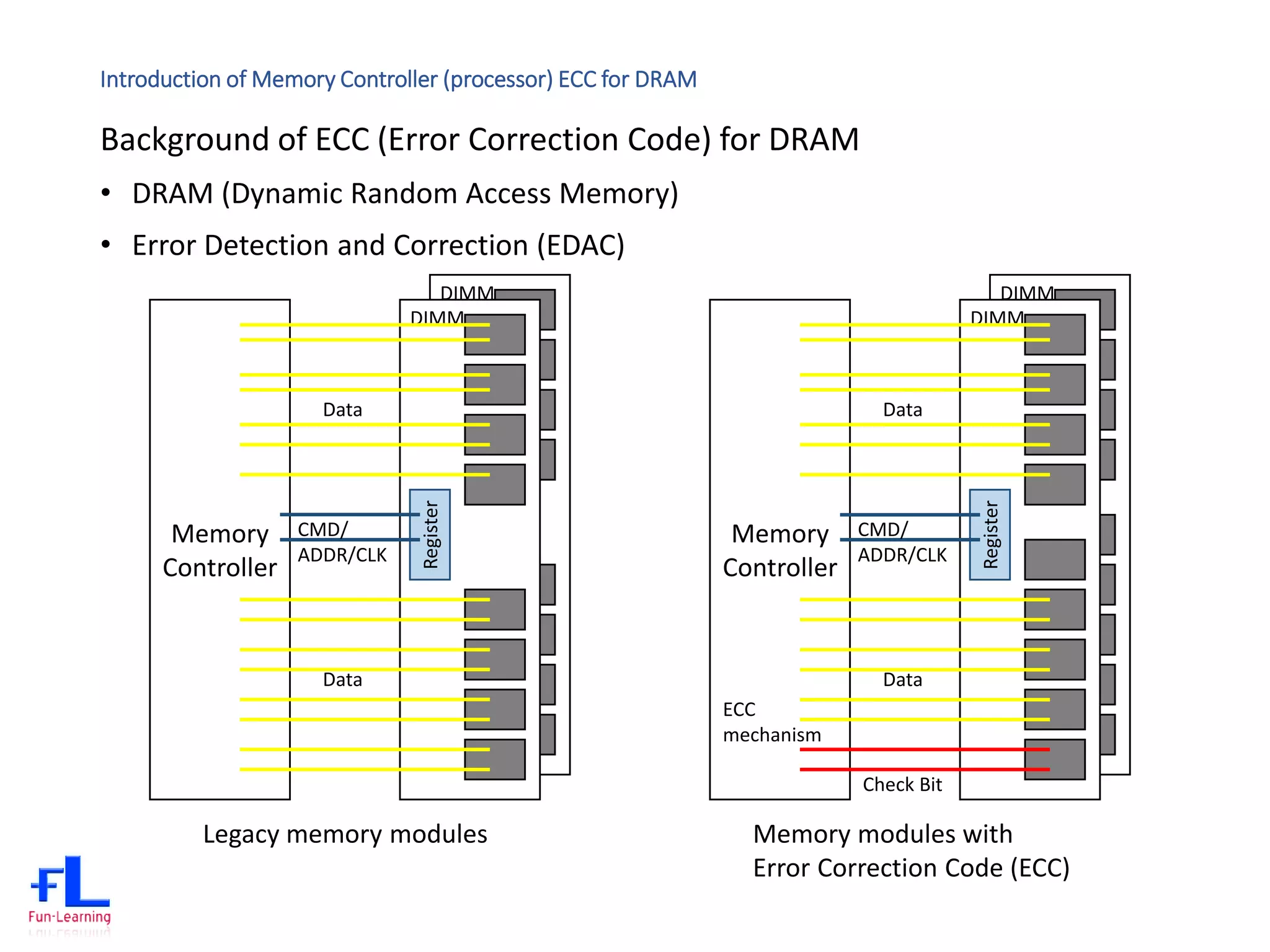

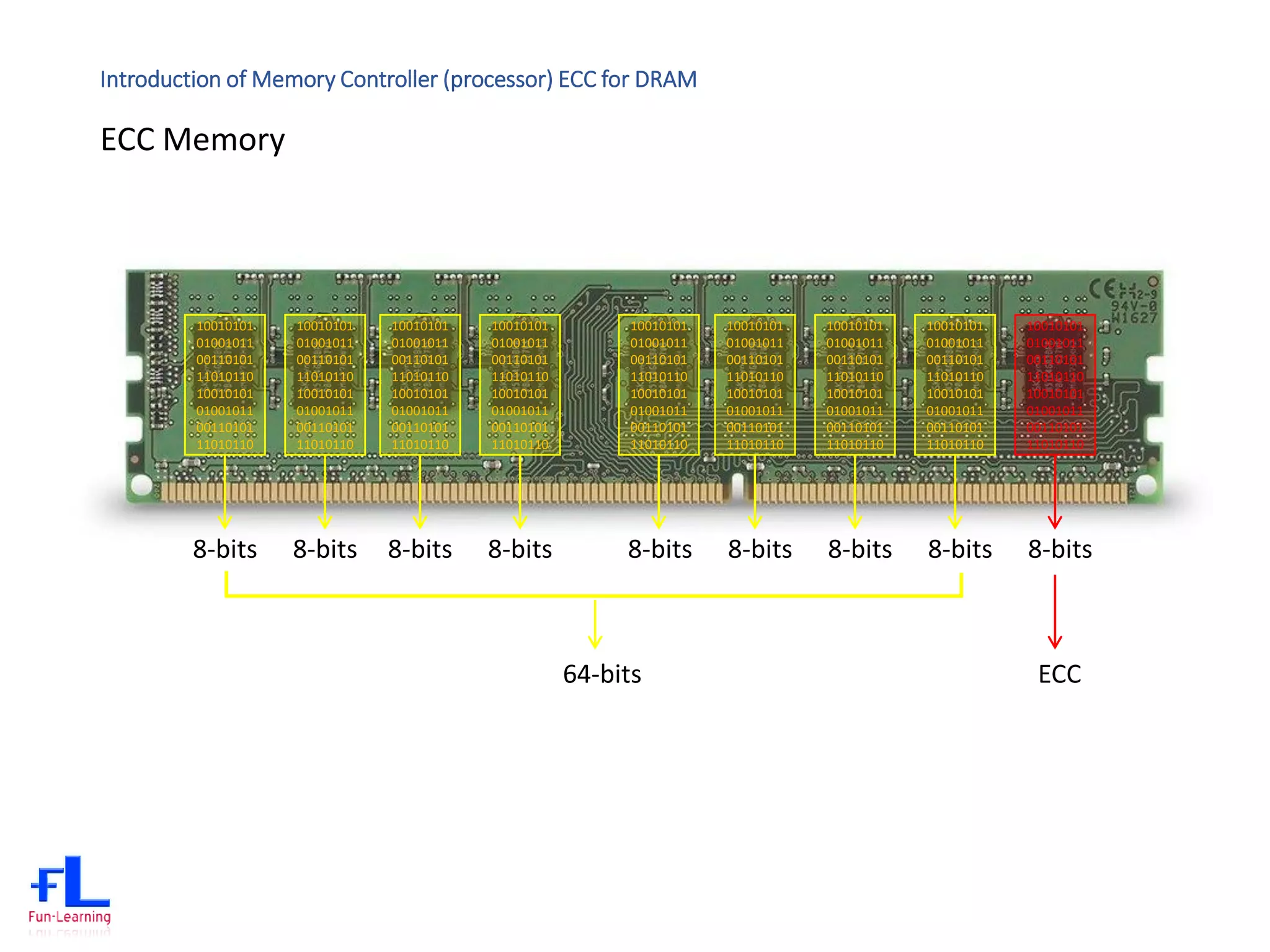

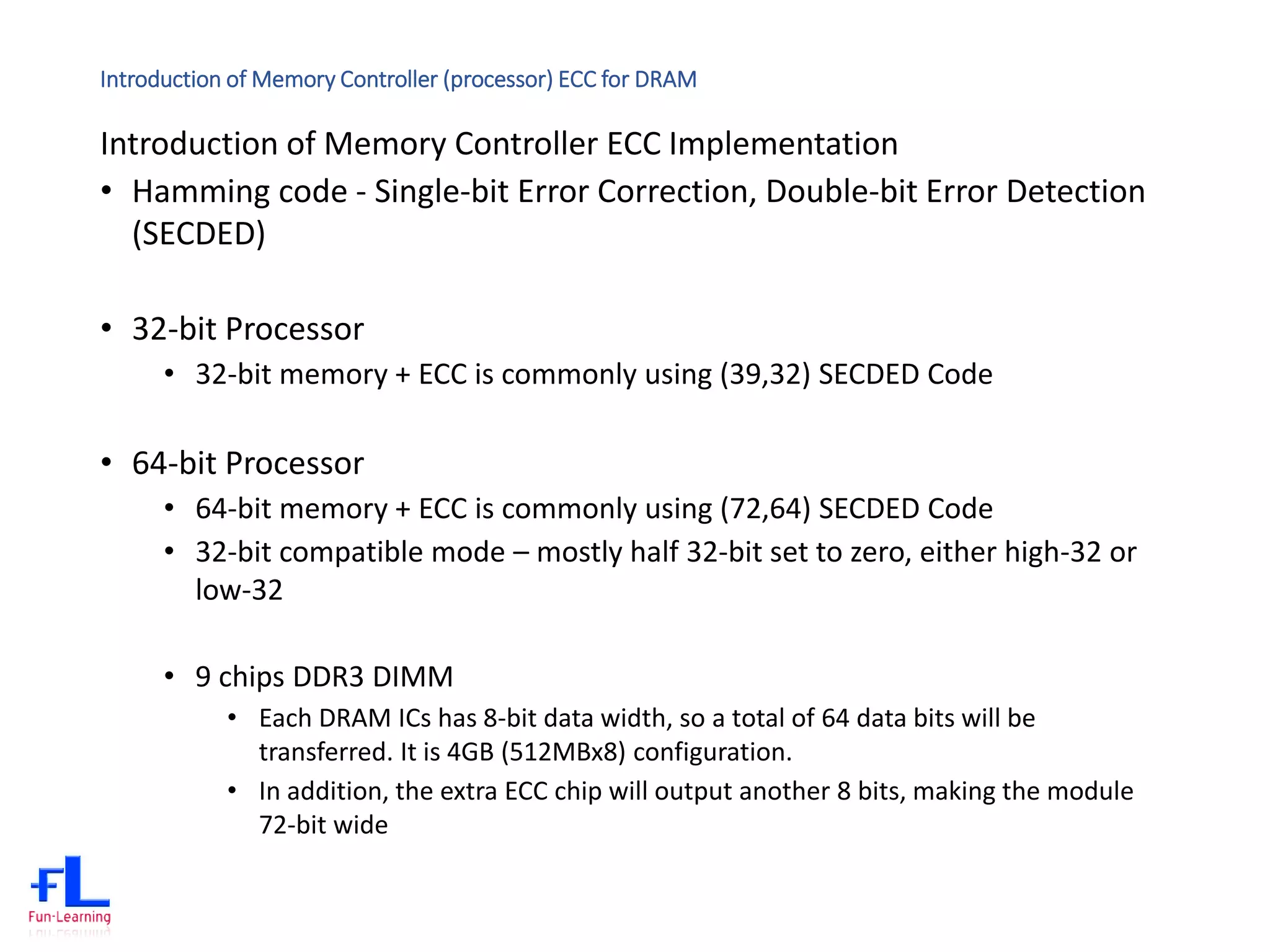

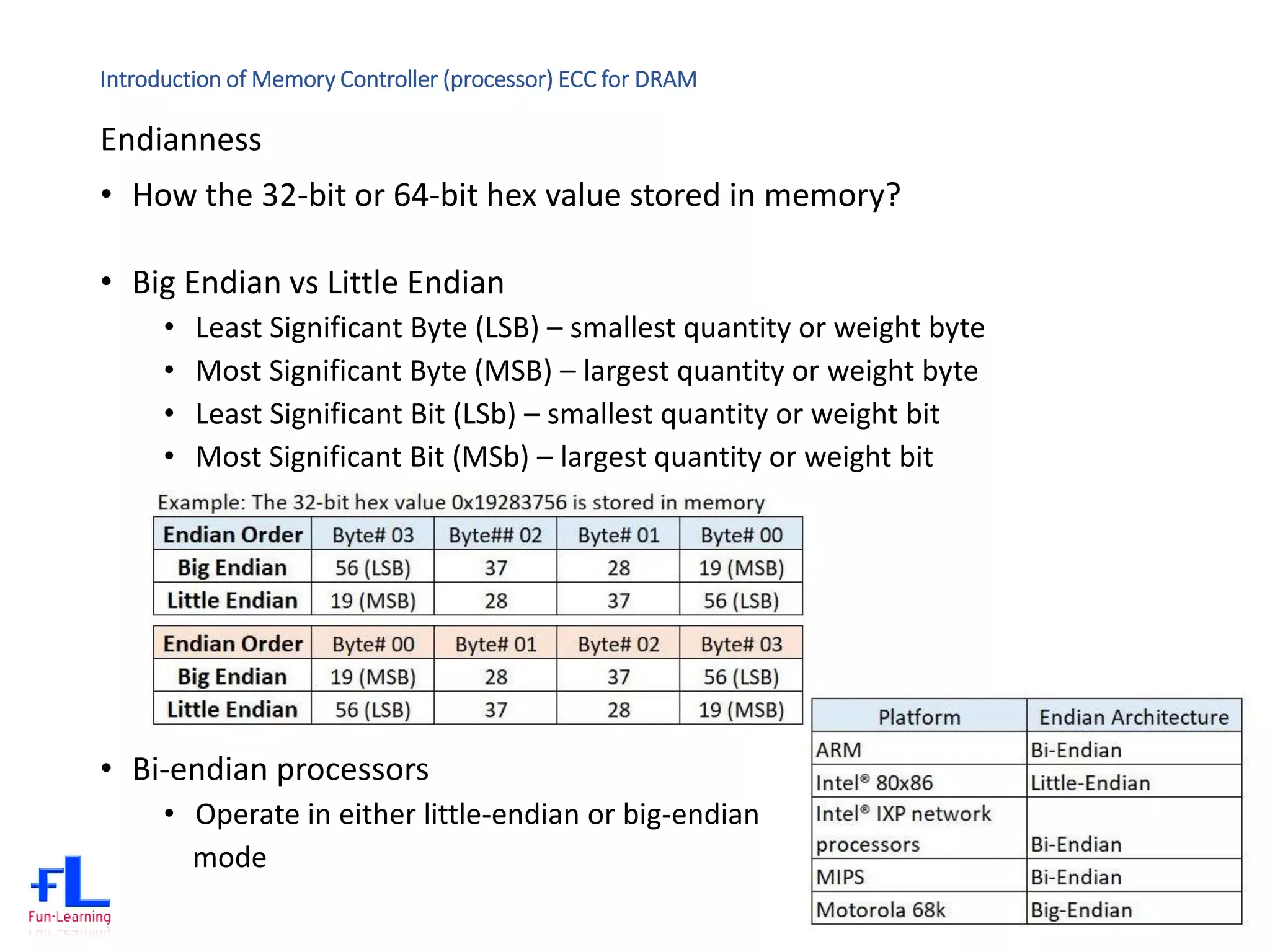

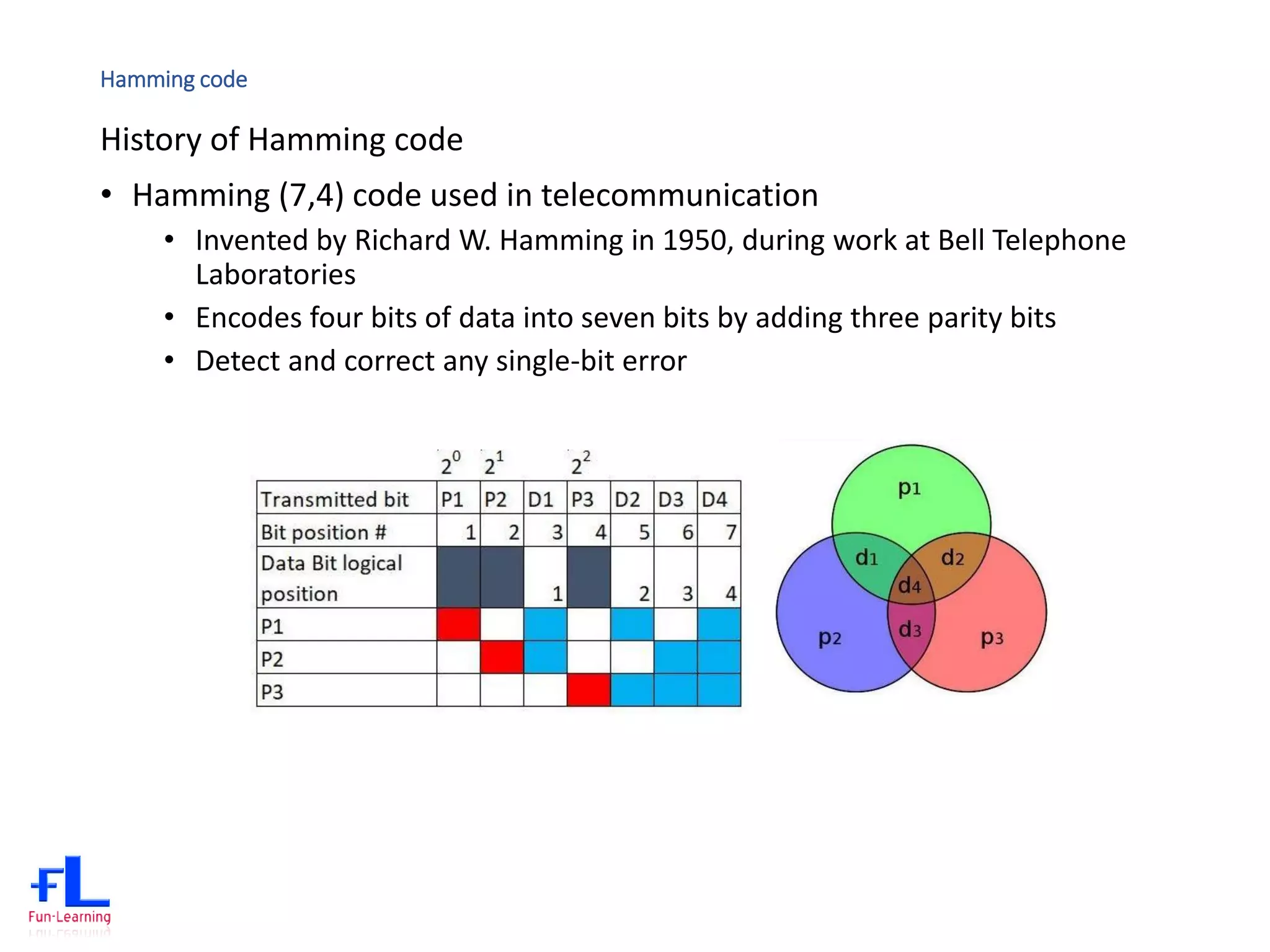

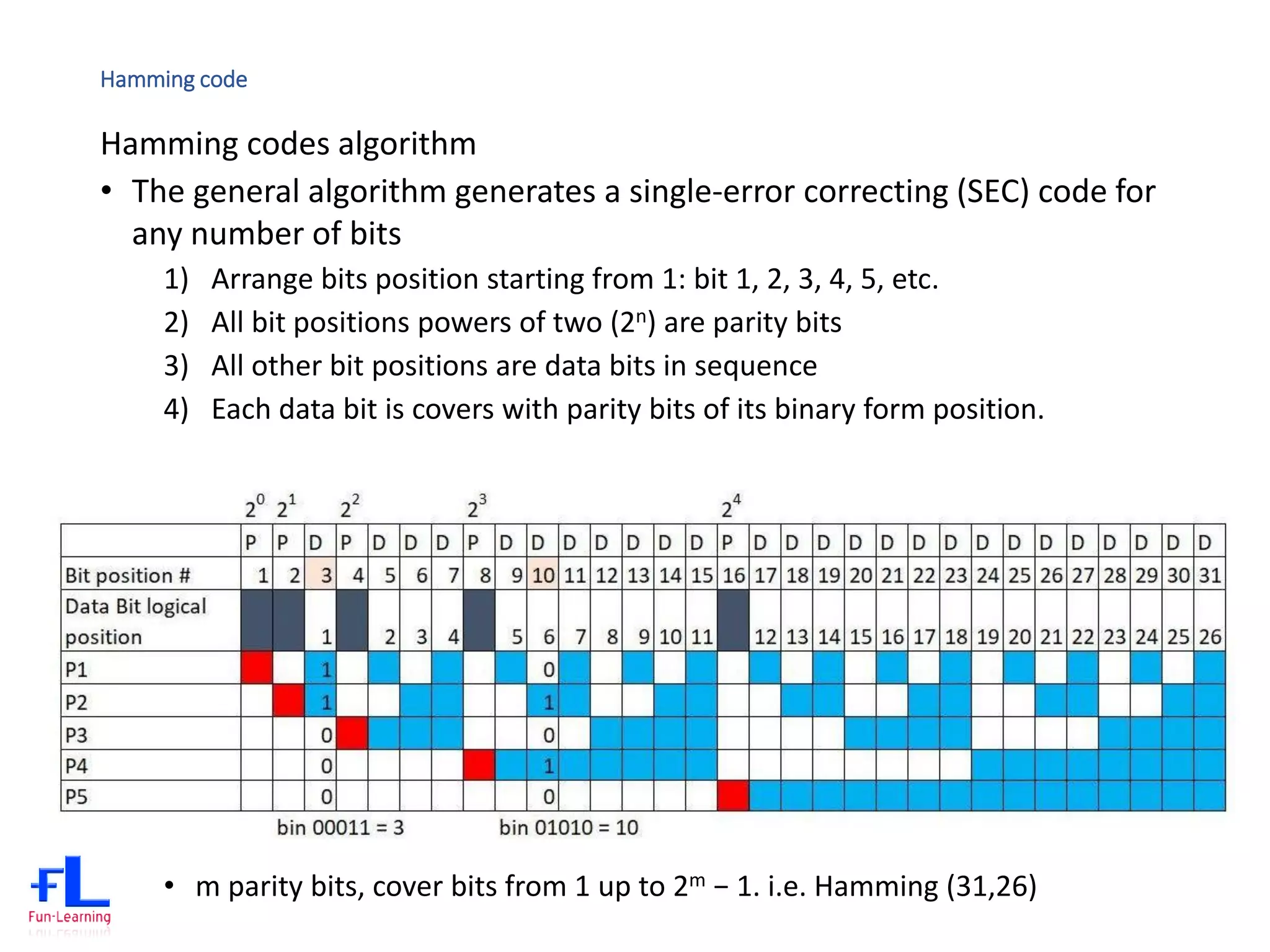

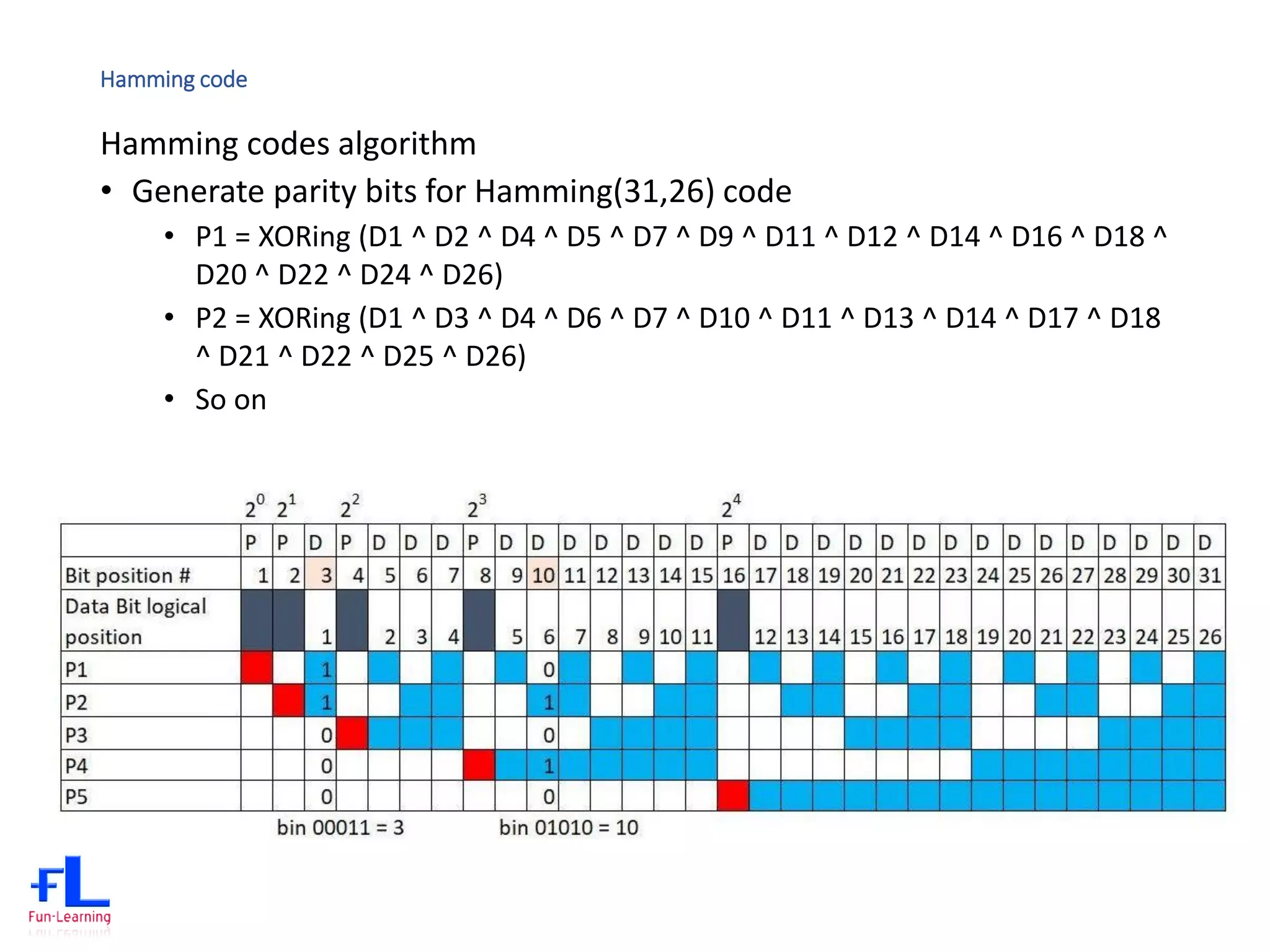

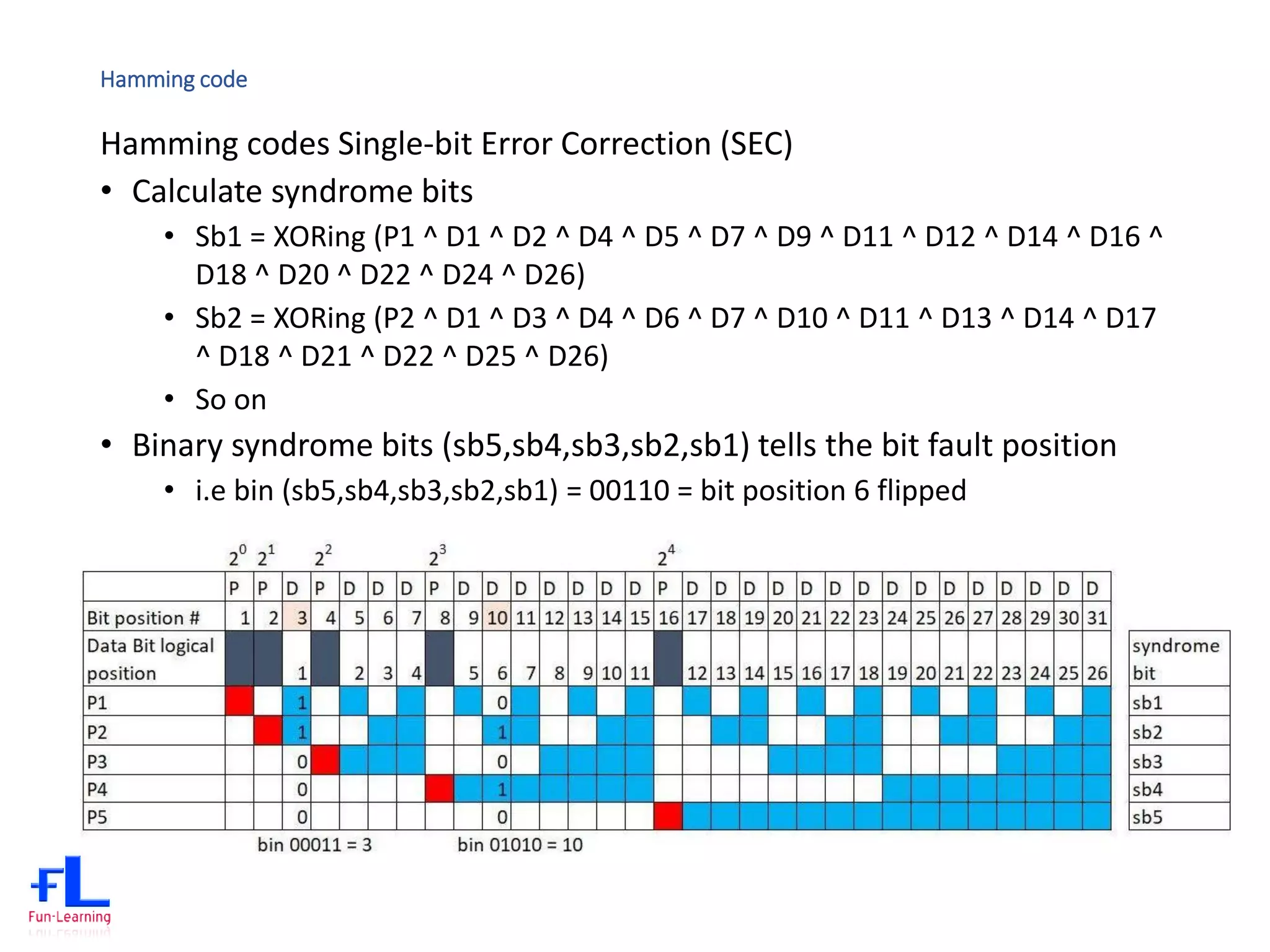

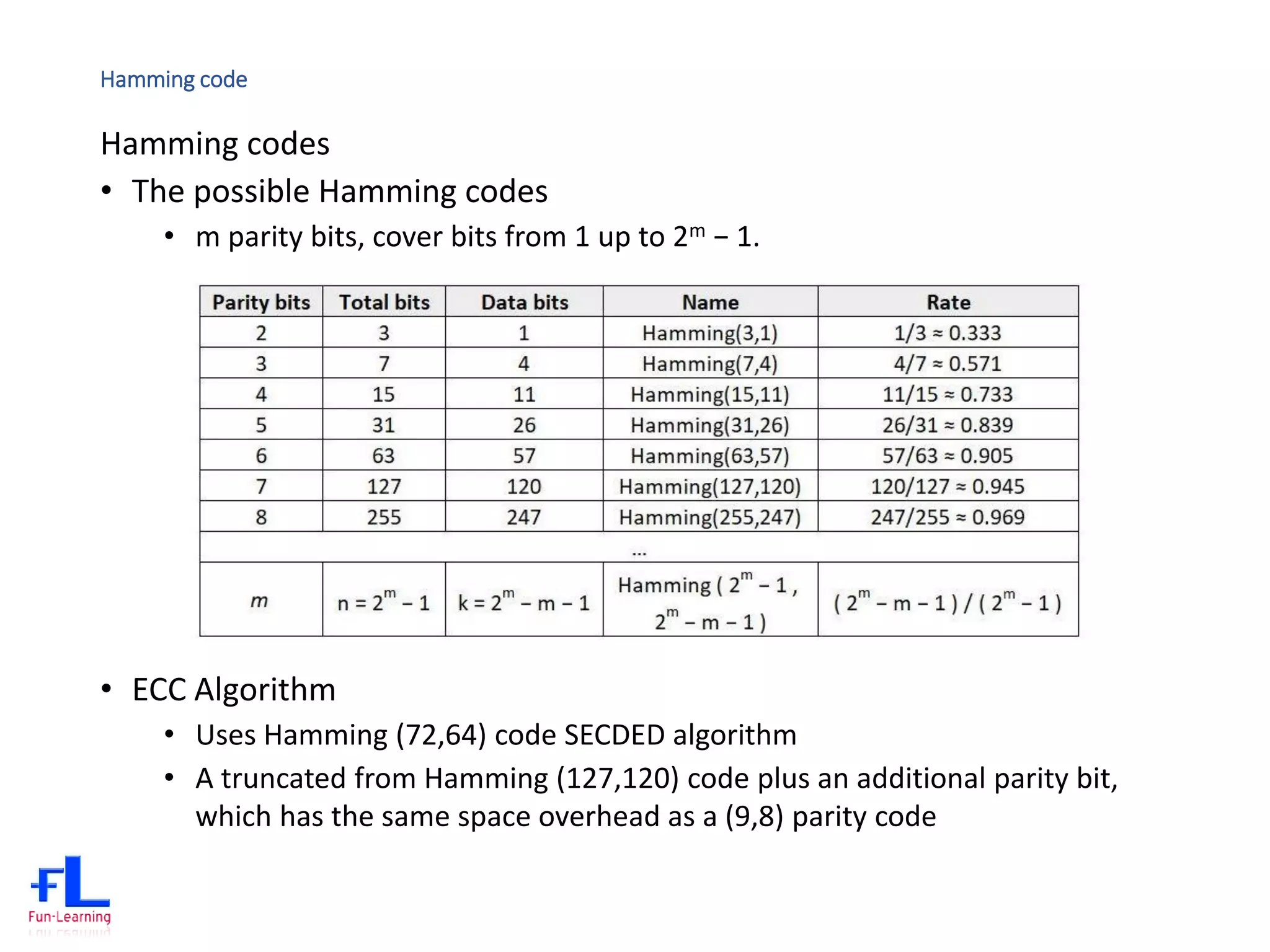

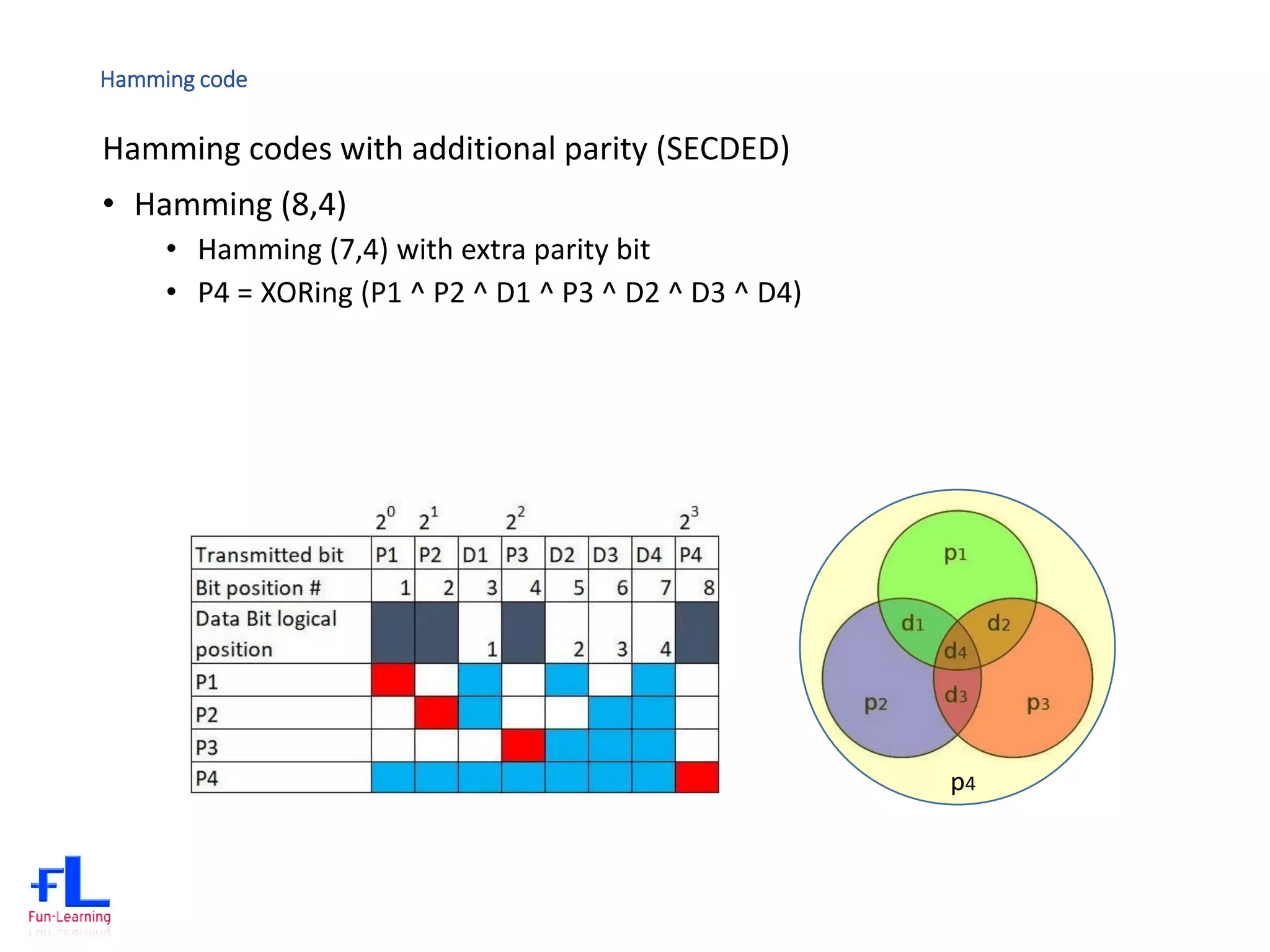

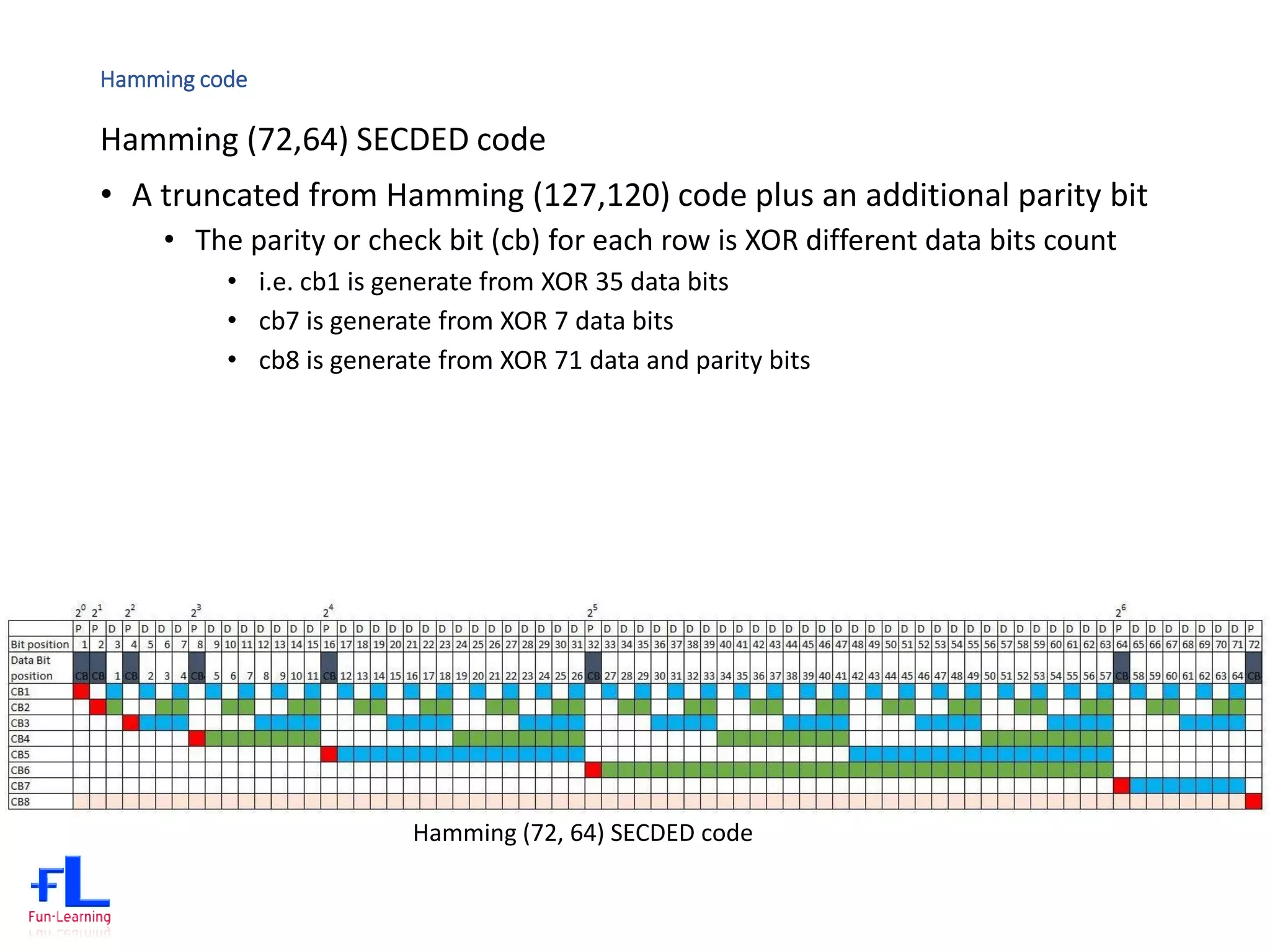

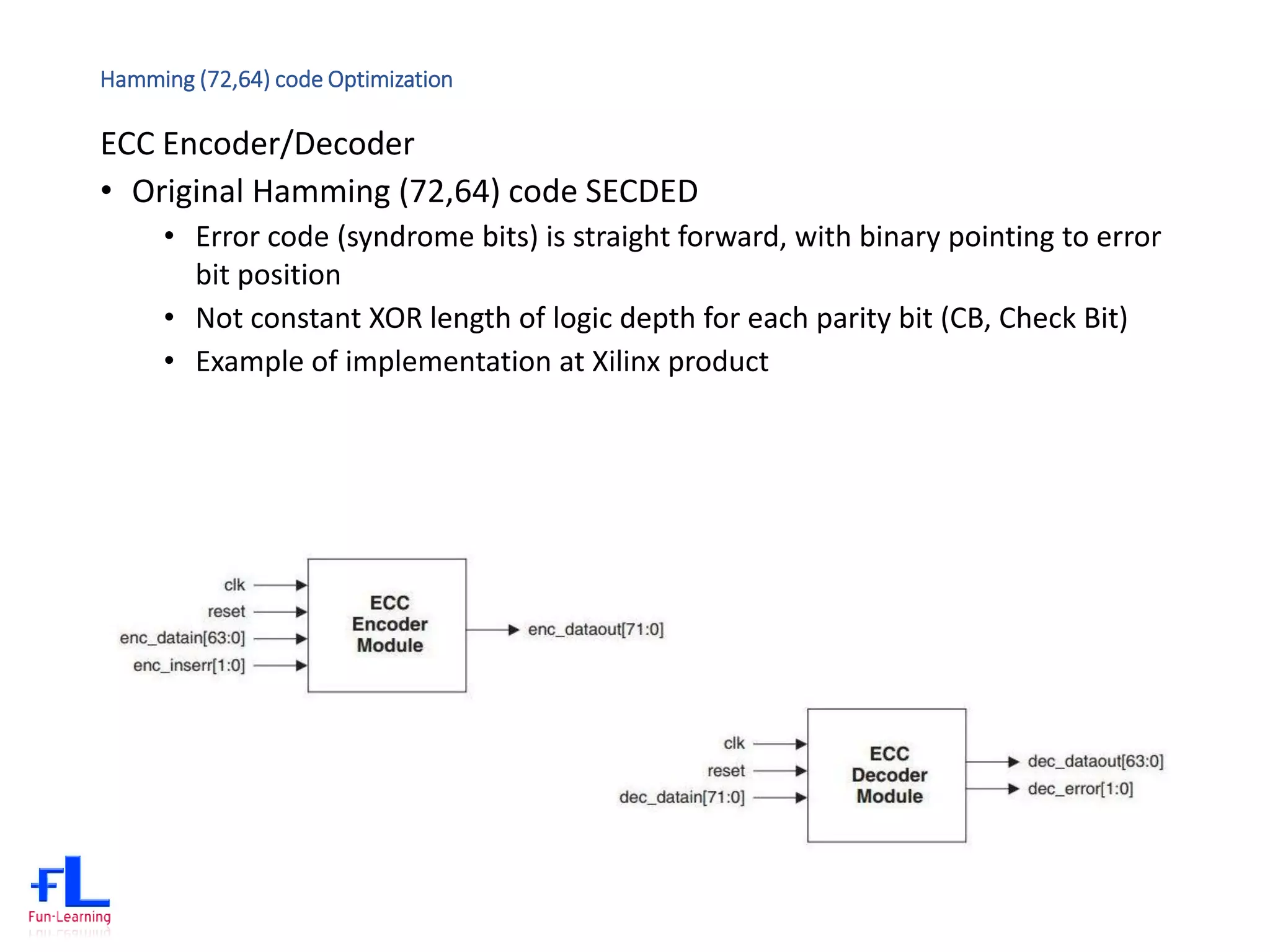

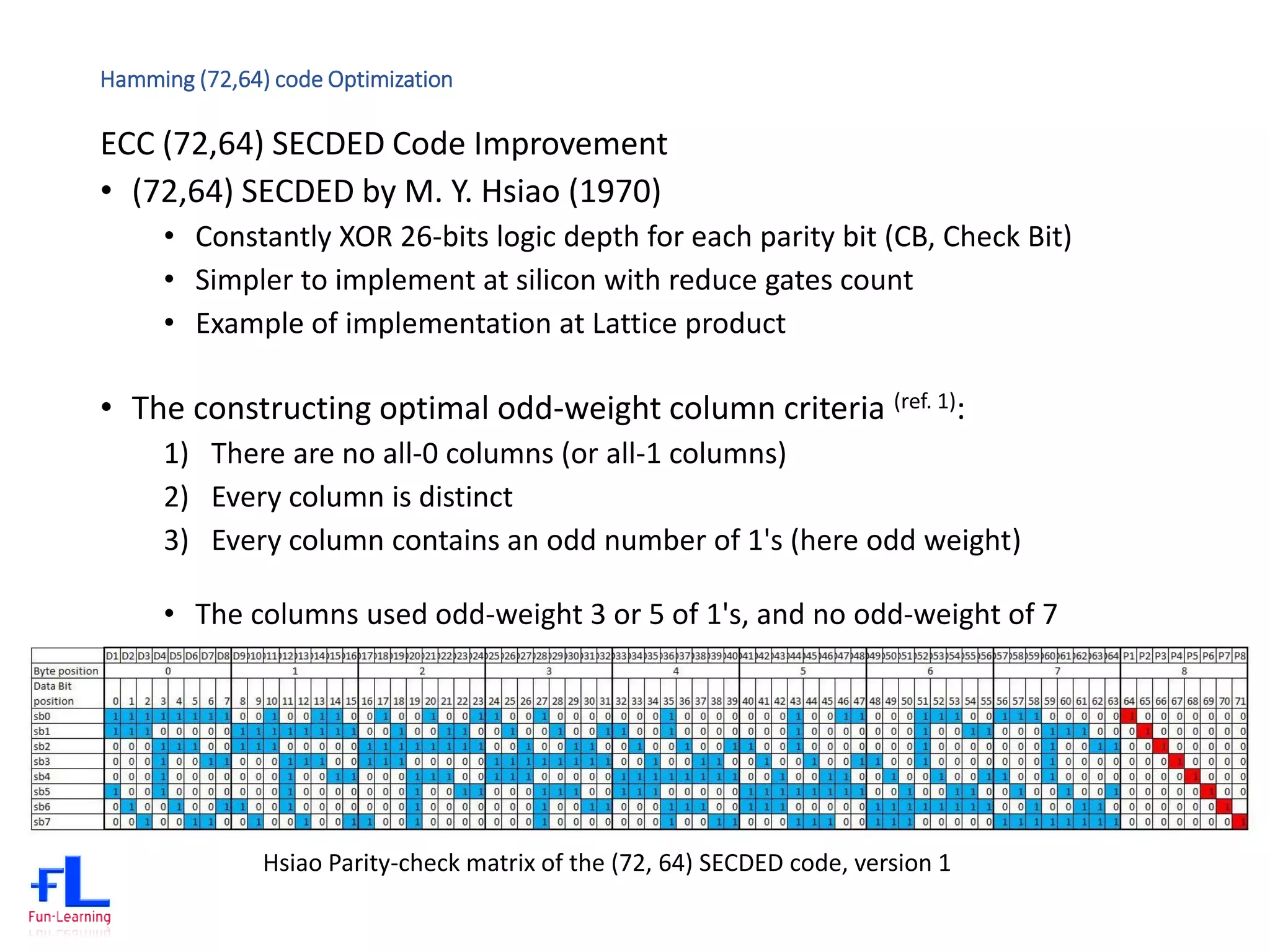

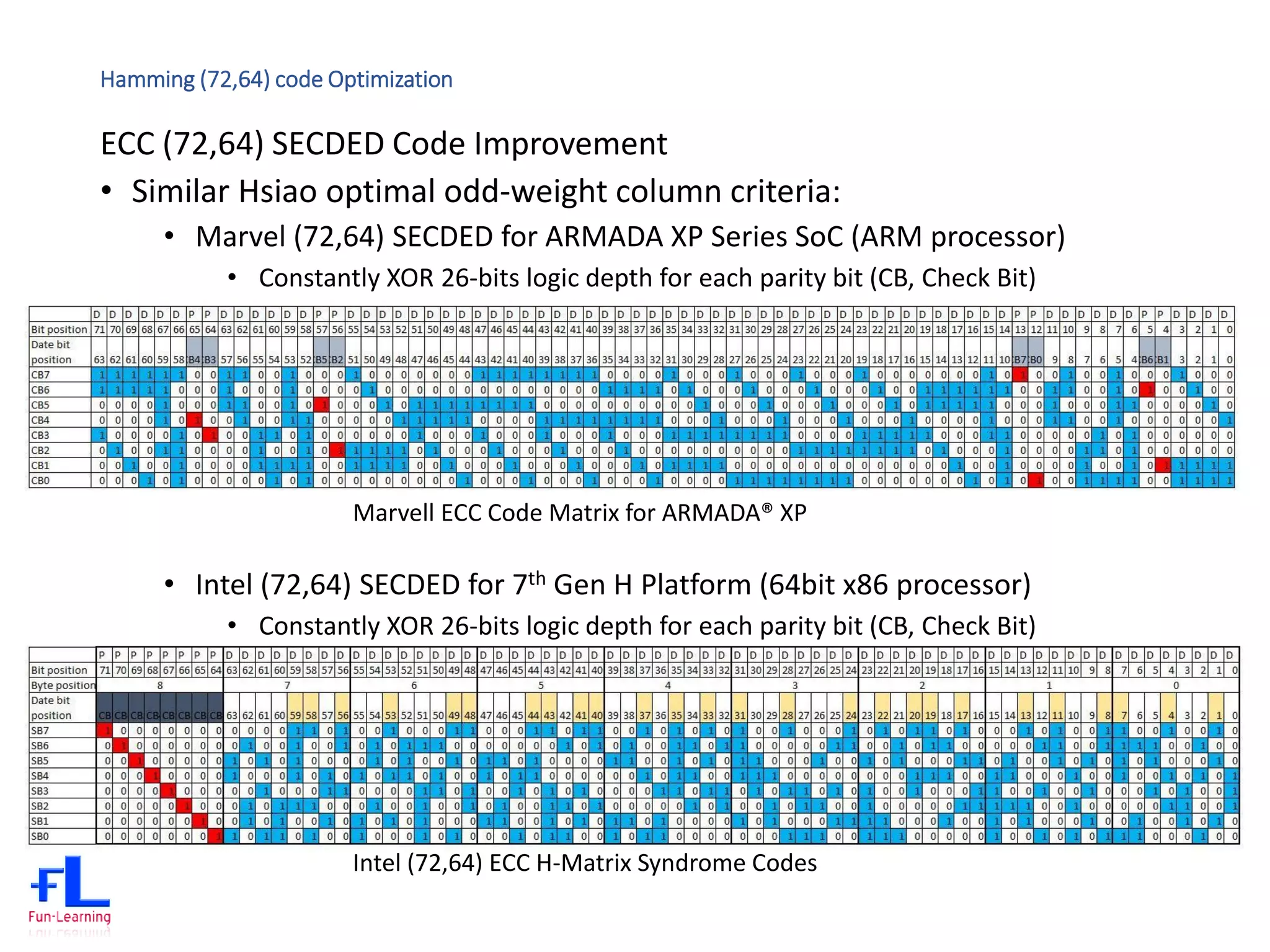

The document discusses error correction codes (ECC) used for dynamic random access memory (DRAM). It introduces how ECC is implemented using a memory controller on the processor. It describes the academic background of Hamming codes, including the commonly used (72,64) single error correction, double error detection (SECDED) code. It also discusses optimizations of the (72,64) SECDED code implemented in industrial systems to simplify the logic and reduce gate counts.