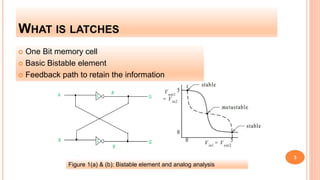

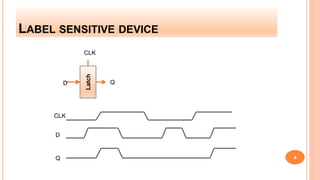

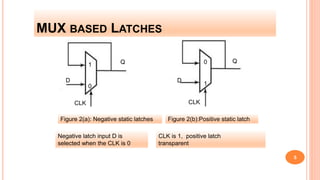

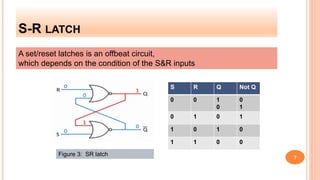

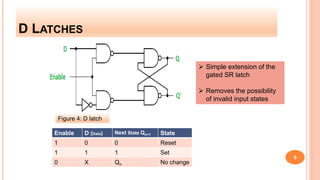

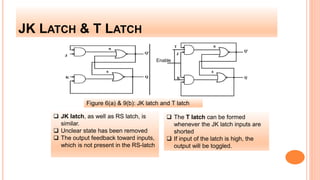

This document discusses different types of latches used in computing and data storage. It describes latches as basic bistable elements that use feedback to retain information. The document outlines several types of latches including SR latches, D latches, JK latches, and T latches. It explains their circuit designs and behaviors. Examples are provided of how latches are used to encode binary data and in synchronous and asynchronous systems. Advantages of latches like flexibility and power efficiency are contrasted with disadvantages like potential race conditions and metastability issues.