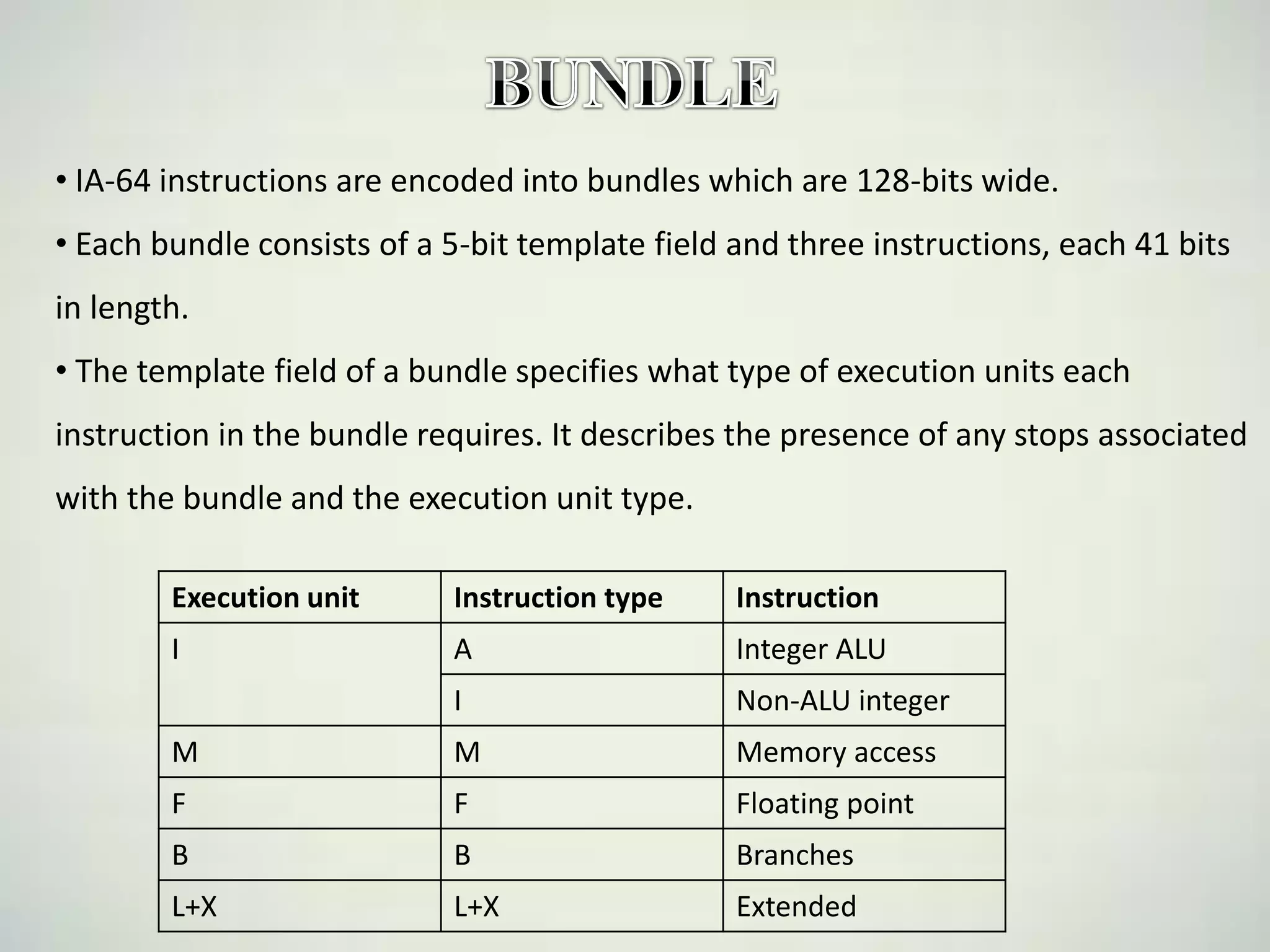

The document describes a RISC-style instruction set architecture featuring a variety of registers for different functions, including general purpose, floating point, and predicate registers, which optimize performance and support compiler exploitation of instruction-level parallelism. It details the use of a register stack mechanism for procedural calls, special load/store instructions, and advanced load capabilities to enhance speculative execution. Additionally, it outlines the bundling of instructions for parallel execution and the mechanisms for managing predicate registers and deferred exceptions.