hardware implementation of aes encryption and decryption for low area & low power consumption

•

1 like•911 views

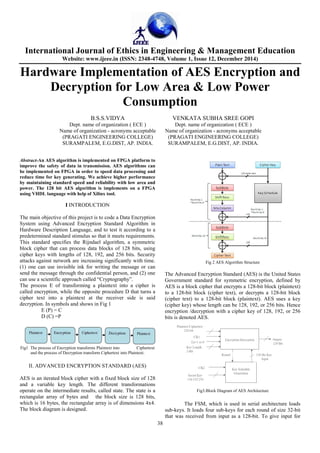

Abstract-An AES algorithm is implemented on FPGA platform to improve the safety of data in transmission. AES algorithms can be implemented on FPGA in order to speed data processing and reduce time for key generating. We achieve higher performance by maintaining standard speed and reliability with low area and power. The 128 bit AES algorithm is implements on a FPGA using VHDL language with help of Xilinx tool.

Report

Share

Report

Share

Download to read offline

Recommended

Hardware implementation of aes encryption and decryption for low area & power...

Hardware implementation of aes encryption and decryption for low area & power...eSAT Publishing House

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and TechnologyIMPLEMENTATION OF AES AS A CUSTOM HARDWARE USING NIOS II PROCESSOR

This document describes the implementation of the Advanced Encryption Standard (AES) algorithm as a custom hardware accelerator connected to a Nios II processor system. AES was written in VHDL and connected to the Nios II system through GPIO pins. This allows AES operations to be controlled through C code in the Nios II IDE while running the AES algorithm in hardware, improving encryption speeds significantly compared to an all-software implementation. Synthesis results showed the hardware AES implementation reduced the number of clock cycles needed for encryption by over 99% compared to running AES solely in software on the Nios II processor.

An Efficient VLSI Architecture for AES and It's FPGA Implementation

This document discusses the design and FPGA implementation of an efficient VLSI architecture for the AES encryption algorithm. It begins with an introduction to cryptography and the AES algorithm. It then describes the key components of AES including the state array, substitution bytes, shift rows, mix columns, add round key transformations, and key expansion. The document proposes a pipelined design to reduce encryption delay by generating round keys in parallel with encryption rounds. Simulation results show this pipelined AES architecture can operate at higher clock frequencies, increasing encryption throughput for time-critical applications. In conclusion, the hardware implementation provides faster encryption speeds and higher throughput compared to a software solution.

Implementation of Fast Pipelined AES Algorithm on Xilinx FPGA

Implementation of Fast Pipelined AES Algorithm on Xilinx FPGAInternational Journal of Science and Research (IJSR)

The Advanced Encryption Standard (AES) is a specification for the encryption of electronic data also called Rijndael. The algorithm described by AES is a symmetric-key algorithm, meaning the same key is used for both encrypting and decrypting the data. Hardware-based cryptography is used for authentication of users and of software updates and installations. Software implementations can generally not be used for this, as the cryptographic keys are stored in the PC memory during execution, and are vulnerable to malicious codes. Hardware-based encryption products can also vary in the level of protection they provide against brute force rewind attacks, Offline parallel attacks, or other cryptanalysis attacks. The algorithm was implemented in FPGA due to its flexibility and reconfiguration capability. A reconfigurable device is very convenient for a cryptography algorithm since it allows cheap and quick alterations. The implementation of pipelined cryptography hardware was used to improve performance in order to achieve higher throughput and greater parallelism. The AES hardware was implemented in three modules contains of the encryption, the decryption and the key expansion module.

IRJET- Design and Implementation of 256-Bits Cryptography Algorithm used in t...

The document describes a proposed 256-bit cryptography algorithm implemented in VHDL that is resistant to brute-force and timing attacks. The algorithm uses a modified version of the Data Encryption Standard (DES) to encrypt 256-bit plaintext into 256-bit ciphertext using a 224-bit cipher key. It then applies a Hamming(448,256) error correcting code to the ciphertext to generate the final 448-bit encrypted data. Simulation results show the encryption and decryption processes encrypt the plaintext into ciphertext and recover the original plaintext, with an encryption time of 19.231 nanoseconds, making the algorithm resistant to brute-force and timing attacks.

Arm recognition encryption by using aes algorithm

Abstract To provide the security of the Military confidential data we use encryption algorithm which take over reward of superior encryption algorithm. The proposed implementation using encryption algorithm was implemented on ARM 7 to encrypt and decrypt the confidential data on data storage devices such as SD card or Pen drive. The main objective of proposed implementation is to provide protection for storage devices. The ARM and encryption algorithm protect the data accessibility, reliability and privacy successfully. Since (AES) Advanced Encryption Standard algorithm is widely used in an embedded system or fixed organization. These AES algorithms are used for proper designs in defense for security. Keywords: Plain text, Cipher text, Data security, AES, Embedded System.ARM, storage device.

H04425053

This document proposes a double layer lookup table technique for improving data security when implemented on an FPGA. The technique uses two lookup tables embedded in the FPGA, each with predefined length and contents. Input data is encrypted by XORing it with the values in the first lookup table. This ciphertext is then encrypted again by XORing it with the second lookup table. This makes the real data difficult for an adversary to obtain as they would not know the length or contents of the lookup tables. The design is implemented in FPGA using VHDL programming and synthesis tools to create and download the configuration to the physical device. Experimental results demonstrate the encryption process using example data streams and lookup table values.

Fpga based encryption design using vhdl

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Recommended

Hardware implementation of aes encryption and decryption for low area & power...

Hardware implementation of aes encryption and decryption for low area & power...eSAT Publishing House

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and TechnologyIMPLEMENTATION OF AES AS A CUSTOM HARDWARE USING NIOS II PROCESSOR

This document describes the implementation of the Advanced Encryption Standard (AES) algorithm as a custom hardware accelerator connected to a Nios II processor system. AES was written in VHDL and connected to the Nios II system through GPIO pins. This allows AES operations to be controlled through C code in the Nios II IDE while running the AES algorithm in hardware, improving encryption speeds significantly compared to an all-software implementation. Synthesis results showed the hardware AES implementation reduced the number of clock cycles needed for encryption by over 99% compared to running AES solely in software on the Nios II processor.

An Efficient VLSI Architecture for AES and It's FPGA Implementation

This document discusses the design and FPGA implementation of an efficient VLSI architecture for the AES encryption algorithm. It begins with an introduction to cryptography and the AES algorithm. It then describes the key components of AES including the state array, substitution bytes, shift rows, mix columns, add round key transformations, and key expansion. The document proposes a pipelined design to reduce encryption delay by generating round keys in parallel with encryption rounds. Simulation results show this pipelined AES architecture can operate at higher clock frequencies, increasing encryption throughput for time-critical applications. In conclusion, the hardware implementation provides faster encryption speeds and higher throughput compared to a software solution.

Implementation of Fast Pipelined AES Algorithm on Xilinx FPGA

Implementation of Fast Pipelined AES Algorithm on Xilinx FPGAInternational Journal of Science and Research (IJSR)

The Advanced Encryption Standard (AES) is a specification for the encryption of electronic data also called Rijndael. The algorithm described by AES is a symmetric-key algorithm, meaning the same key is used for both encrypting and decrypting the data. Hardware-based cryptography is used for authentication of users and of software updates and installations. Software implementations can generally not be used for this, as the cryptographic keys are stored in the PC memory during execution, and are vulnerable to malicious codes. Hardware-based encryption products can also vary in the level of protection they provide against brute force rewind attacks, Offline parallel attacks, or other cryptanalysis attacks. The algorithm was implemented in FPGA due to its flexibility and reconfiguration capability. A reconfigurable device is very convenient for a cryptography algorithm since it allows cheap and quick alterations. The implementation of pipelined cryptography hardware was used to improve performance in order to achieve higher throughput and greater parallelism. The AES hardware was implemented in three modules contains of the encryption, the decryption and the key expansion module.

IRJET- Design and Implementation of 256-Bits Cryptography Algorithm used in t...

The document describes a proposed 256-bit cryptography algorithm implemented in VHDL that is resistant to brute-force and timing attacks. The algorithm uses a modified version of the Data Encryption Standard (DES) to encrypt 256-bit plaintext into 256-bit ciphertext using a 224-bit cipher key. It then applies a Hamming(448,256) error correcting code to the ciphertext to generate the final 448-bit encrypted data. Simulation results show the encryption and decryption processes encrypt the plaintext into ciphertext and recover the original plaintext, with an encryption time of 19.231 nanoseconds, making the algorithm resistant to brute-force and timing attacks.

Arm recognition encryption by using aes algorithm

Abstract To provide the security of the Military confidential data we use encryption algorithm which take over reward of superior encryption algorithm. The proposed implementation using encryption algorithm was implemented on ARM 7 to encrypt and decrypt the confidential data on data storage devices such as SD card or Pen drive. The main objective of proposed implementation is to provide protection for storage devices. The ARM and encryption algorithm protect the data accessibility, reliability and privacy successfully. Since (AES) Advanced Encryption Standard algorithm is widely used in an embedded system or fixed organization. These AES algorithms are used for proper designs in defense for security. Keywords: Plain text, Cipher text, Data security, AES, Embedded System.ARM, storage device.

H04425053

This document proposes a double layer lookup table technique for improving data security when implemented on an FPGA. The technique uses two lookup tables embedded in the FPGA, each with predefined length and contents. Input data is encrypted by XORing it with the values in the first lookup table. This ciphertext is then encrypted again by XORing it with the second lookup table. This makes the real data difficult for an adversary to obtain as they would not know the length or contents of the lookup tables. The design is implemented in FPGA using VHDL programming and synthesis tools to create and download the configuration to the physical device. Experimental results demonstrate the encryption process using example data streams and lookup table values.

Fpga based encryption design using vhdl

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

Js2517181724

IJERA (International journal of Engineering Research and Applications) is International online, ... peer reviewed journal. For more detail or submit your article, please visit www.ijera.com

G05124550

This document presents an optimized FPGA hardware implementation of public key cryptography using encryption and decryption. The implementation uses two keys - a public key for encryption that anyone can use, and a private key for decryption that only the intended recipient possesses. The design was tested on a Xilinx Virtex 5 FPGA. Encryption and decryption were shown to work correctly when the proper keys were used. Without the private key, decryption was not possible, demonstrating the security of the approach. Synthesis results showed the design utilizes FPGA resources efficiently compared to other related work.

FPGA and ASIC Implementation of Speech Encryption and Decryption using AES Al...

FPGA and ASIC Implementation of Speech Encryption and Decryption using AES Al...IJCSIS Research Publications

With increasing technology development in field of communication and Electronic devices, there is a need for better security service for information transfer in Medical Sectors, Banking, Financial and in other IoT applications etc. Fight against security attacks is of prime importance. Through Cryptographic techniques we can provide Authenticity as well as Confidentiality for the user data. In this paper, hardware implementation has been described for a real-time application of speech data encryption and decryption using AES algorithm along with the speech recognition using cross correlation technique. Verilog programming environment is used for AES cryptography whereas MATLAB is used for Speech recognition. ASIC design on AES core is implemented using Cadence tools. Number of gates, area and power used by AES core design has been drastically reduced by specifying wide range of constraints during front end designing. In Backend designing, layout of AES design, which is the physical geometric representation is also developed.Simulated Analysis and Enhancement of Blowfish Algorithm

This paper represents or analyzes the security of system based on Blowfish. Blowfish mainly focuses

on the encrypt and decrypt techniques and algorithms apply for cryptanalysis. It describe the algorithms for

encryption as well as decryption algorithms and also give the sufficient description of key generation, key

expansion, function and working principle of Blowfish cipher with proper explanations. Taking the current era,

Most of the famous systems which offer security for a network or web or to a data are vulnerability to attacks and

they are broken at some point of time by effective cryptanalysis methods, irrespective of its complex algorithmic

design. In the general, today’s cryptography world is bounded to an interpretive of following any one or multi

encryption scheme and that too for a single iteration on a single file only. This is evident in the maximum of the

encryption-decryption cases. It also describes the comparisons between older blowfish and enhances blowfish. It

also shows enhance Blowfish algorithm for encryption and decryption of data. It is also give the proper simulated

analysis of encryption and decryption time for different file formats using a windows application. It describe

feature of application and its process and efficiency as well as calculation of time and throughput.

A VHDL Implemetation of the Advanced Encryption Standard-Rijndael.pdf

This document describes a thesis submitted by Rajender Manteena to the University of South Florida for a Master of Science in Electrical Engineering. The thesis presents a VHDL implementation of the Advanced Encryption Standard (AES) Rijndael algorithm. It includes descriptions of the encryption and decryption processes, mathematical background on finite field arithmetic, and implementation results from simulating the VHDL code on an Altera FPGA development board. The goal was to create an optimized hardware implementation of the AES algorithm using VHDL for applications such as encryption processors or smart cards.

M04302093096

International Journal of Computational Engineering Research(IJCER) is an intentional online Journal in English monthly publishing journal. This Journal publish original research work that contributes significantly to further the scientific knowledge in engineering and Technology.

A vlsi implementation of a resource efficient and secure architecture of a b...

This document discusses the VLSI implementation of a resource efficient and secure architecture for a block cipher. It proposes two designs - a throughput enhanced design and an area reduced design. The designs implement a 128-bit block cipher using the Hummingbird algorithm. Simulation results on ModelSim and synthesis results on Xilinx show that the area reduced design uses fewer logic resources than the throughput enhanced design, making it more suitable for FPGA implementation where area is a concern.

Enhanced Advanced Encryption Standard (E-AES): using ESET

This document proposes an enhanced version of the Advanced Encryption Standard (AES) called E-AES. E-AES increases the key size to 2048 bits and the block size to 1024 bits. This provides more security than AES, which uses a 128, 192, or 256 bit key on a 128 bit block. E-AES specifies 64 rounds of encryption, compared to AES which uses 10 to 14 rounds depending on key size. The encryption process of E-AES involves four transformations at each round: byte substitution using an S-box, shifting rows of the state matrix, mixing data within columns, and adding a round key. This enhanced algorithm is proposed to address known attacks on AES and the use of its 16 year old standard with

An improved geo encryption algorithm in location based services

Abstract Wireless technology is used in many applications with location based data encryption techniques to secure the communication. The use of knowledge of the mobile user's location called Geo-encryption, produces more secure systems that can be used in different mobile applications. Location Based Data Encryption Methods (LBDEM) is a technique used to enhance the security of such applications called as Location Based Services (LBS). It collects position, time, latitude coordinates and longitude coordinates of mobile nodes and uses for the encryption and decryption process. Geo-encryption plays an important role to raise the security of LBS. Different Geo-protocols have been developed in the same area to add security with better throughput. The Advanced Encryption Standard in Geo-encryption with Dynamic Tolerance Distance (AES-GEDTD) is an approach which gives higher security with a great throughput. This approach mainly uses the AES algorithm, symmetric key encryption algorithm. But applying this algorithm to more complex data like images, videos, etc. like in Digital Film Distribution, we might face the problem of computational overhead. To overcome this problem, we analyze AES and modify it, to reduce the computational overhead. In the modified AES algorithm (M-AES), we omit the calculation of mix column operations and hence the M-AES-GEDTD is a fast and lightweight algorithm for multimedia data. Keywords: Geo-encryption; LBDEM; LBS, Geo-locked Keys .

Design of A New Lightweight Encryption for Embedded Security

The document describes a proposed new lightweight encryption algorithm called PRESENT GRP for embedded security applications. It is designed to have low power consumption, small memory footprint, and provide security. The algorithm combines the substitution box of the existing PRESENT algorithm with a new group random permutation (GRP) layer, which provides confusion and can permute bits faster than a lookup table. Simulation results show PRESENT GRP requires less gate equivalents and memory than existing lightweight algorithms like PRESENT, making it suitable for constrained embedded devices.

Wireless Network Security Architecture with Blowfish Encryption Model

Abstract: In this research paper ,we developed a model for a large network, wireless nodes are interconnected and each can be considered as a node processor that offer services to other node processors connected to a specific network. A very high proportion of the nodes that offer services need to carry out an authentication process so as to make an access request to the node offering the service. In this context, an integrated reconfigurable network security architecture moved to the application layer has become the need of the day for secure wireless data sharing. The security schemes of the seven layer OSI architecture need to be placed intrinsically in the wireless node itself and should be capable of supporting the MAC layer, IP address based layer and the routing protocols of the network layer. This work focuses on the use of emulator and embedded hardware architectures for wireless network security. In this work, the individual nodes can have a unique security signature pattern maintained by respective wireless nodes using an encryption algorithm and this is made dynamic. The metrics includes latency, throughput, Scalability, Effects of data transfer operation on node processor and application data located in the processor Keywords:Wireless Network security, Embedded hardware, Reconfigurable architecture, blowfish algorithm

New Technique Using Multiple Symmetric keys for Multilevel Encryption

In a world of accelerating communications, cryptography has become an essential component of the modern

means of communication systems. The emergence of the webas a reliable medium for commerce and

communication has made cryptography an essential component. Many algorithms or ciphers are in use

nowadays. The quality of the cipher is judged byits ability to prevent an unrelated party fromknowingthe

original content of the encrypted message. The proposed “Multilevel Encryption Model” is a cryptosystem that

adopts the basic principles of cryptography. It uses five symmetric keys (multiple)

in floating point numbers, plaintext, substitution techniques and key combinations with unintelligible

sequence to produce the ciphertext. The decryption process is also designed to reproduce the plaintext

G04701051058

International Journal of Computational Engineering Research (IJCER) is dedicated to protecting personal information and will make every reasonable effort to handle collected information appropriately. All information collected, as well as related requests, will be handled as carefully and efficiently as possible in accordance with IJCER standards for integrity and objectivity.

Introducing an Encryption Algorithm based on IDEA

Introducing an Encryption Algorithm based on IDEAInternational Journal of Science and Research (IJSR)

International Data Encryption Algorithm (IDEA) is one of the encryption algorithms that is widely used for security purpose. IDEA block cipher operates with 64-bit plain text block and 64-bit cipher text block, and a 128-bit key controls it. The fundamental design of the algorithm is using three different algebraic operations: bitwise Exclusive OR, multiplication modulo, and addition modulo. Having the largest number of weak keys is one of the drawbacks of IDEA. In addition, a new attack during round six of IDEA’s operations has been detected. In this paper, we propose and describe the new design and preliminary implementation of a more secure encryption algorithm based on IDEA, and it is named DS-IDEA. Increasing the size of the key from 128 bits to 512 bits will increase the complexity of the algorithm. The algorithm’s complexity is increased by increasing the amount of diffusion (multiplicative additive block) in a single round. It is implemented to provide better security to the user’s password within the Online Password Management System (OPMS) in order to protect the user’s data within the database from hackers and other forms of unauthorized access.

Implementation of Cryptography Architecture with High Secure Core

International Journal of Modern Engineering Research (IJMER) is Peer reviewed, online Journal. It serves as an international archival forum of scholarly research related to engineering and science education.

International Journal of Modern Engineering Research (IJMER) covers all the fields of engineering and science: Electrical Engineering, Mechanical Engineering, Civil Engineering, Chemical Engineering, Computer Engineering, Agricultural Engineering, Aerospace Engineering, Thermodynamics, Structural Engineering, Control Engineering, Robotics, Mechatronics, Fluid Mechanics, Nanotechnology, Simulators, Web-based Learning, Remote Laboratories, Engineering Design Methods, Education Research, Students' Satisfaction and Motivation, Global Projects, and Assessment…. And many more.

A Survey on Various Lightweight Cryptographic Algorithms on FPGA

In today’s rapid growing technology, digital data are exchanged very frequently in seamless wireless networks. Some of the real time applications examples which are transmitted quickly are voice, video, images and text but not limited to high sensitive information like transaction of creditcard, banking and confidential security numbers/data. Thus protection of confidential data is required with high security to avoid unauthorised access to Wireless networks. This can be done by a technique called ‘Cryptograhy’ and there are two crytography techniques available (such as symmetrical & asymmetrical techniques). The focus in this paper would be on Lightweight symmetric crytography. Lightweight cryptography is used for resource-limited devices such as radio frequency identification (RFID) tags, contactless smart cards and wireless sensor network. In this paper comparative study of selected lightweight symmetric block ciphers such as AES, PRESENT, TEA and HUMMINGBIRD is presented.

Renas Rajab Asaad

Abstract

There is great research going on in the field of data security nowadays. Protecting information from disclosure and breach is of high importance to users personally and to organizations and businesses around the world, as most of information currently are sensitive electronic information transferred over the internet and stored in cloud based system. In this paper, we propose a method to increase the security of messages transferred on the internet, or information stored in the cloud. Our proposed method mainly relies on the Triple Data Encryption Standard (TDES) algorithm. TDES is intact the Data Encryption Standard repeated three times in succession to encrypt data. TDES is considered highly secure as there is no applicable method to break the code itself without knowing the key. We propose to encrypt the key using Cipher Feedback Block algorithm, before using TDES to encrypt data. Such that even when the key is disclosed, the key itself cannot decipher the ciphered text without enciphering the key with CFB. This introduces a new dimension of security to the TDES algorithm.

The method introduced in this paper increases the security of the TDES algorithm using CFB algorithm by increasing the key security, such that it is actually not possible to decipher the text without prior knowledge and agreement of key and algorithms used.

Keywords: Data Encryption Standard, Triple Data Encryption Algorithm, Cipher Feedback Block.

Efficient Fpe Algorithm For Encrypting Credit Card Numbers

This document proposes an efficient format-preserving encryption (FPE) algorithm for encrypting credit card numbers. The algorithm uses AES-128 encryption and adds two additional steps to retain the plaintext format of 16 decimal digits. Specifically, it divides the 128-bit ciphertext into blocks, performs an XOR operation between blocks, and then converts the resulting hexadecimal values to decimal digits. This allows encryption without changing the database structure or queries. The proposed algorithm is faster and requires no additional storage compared to existing FPE techniques like prefix encryption, cycle walking, or Feistel networks. It provides an efficient way to encrypt sensitive numeric fields like credit cards while preserving functionality.

New modification on feistel DES algorithm based on multi-level keys

The data encryption standard (DES) is one of the most common symmetric encryption algorithms, but it experiences many problems. For example, it uses only one function (XOR) in the encryption process, and the combination of data is finite because it occurs only twice and operates on bits. This paper presents a new modification of the DES to overcome these problems. This could be done through adding a new level of security by increasing the key space (using three keys) during the 16 rounds of the standard encryption algorithm and by replacing the predefined XOR operation with a new # operation. Our proposed algorithm uses three keys instead of one. The first key is the input key used for encrypting and decrypting operations. The second key is used for determining the number of bits, while the third key is used for determining the table numbers, which are from 0 to 255. Having evaluated the complexity of our proposed algorithm, the results show that it is the most complex compared with the well-known DES and other modified algorithms. Consequently, in our proposed algorithm, the attacker try a number of attempts 2 1173 at minimum to decrypt the message. This means that the proposed DES algorithm will increase the security level of the well-known DES.

Advanced Encryption Standard (AES) Implementaion using Java

The document describes a project report on the implementation of the AES encryption algorithm. It was submitted by two students, Sunil Kumar R and Shreekant, in partial fulfillment of the requirements for a Bachelor of Engineering degree in computer science. The project was carried out under the guidance of three faculty members at R.V. College of Engineering in Bangalore. It includes a certificate signed by the faculty confirming the students' satisfactory completion of the project.

Aes

This paper presents 16 software implementations of the Advanced Encryption Standard (AES) cipher mapped to a fine-grained many-core processor array. The implementations explore different levels of data and task parallelism. The smallest design uses 6 cores for offline key expansion and 8 cores for online expansion, while the largest uses 107 and 137 cores respectively. Compared to other software platforms, the designs achieve 3.5-15.6 times higher throughput per chip area and 8.2-18.1 times higher energy efficiency.

Aes128 bit project_report

The document discusses the Advanced Encryption Standard (AES) algorithm, which is used for encryption and involves several processes applied to a rectangular array called the state. AES uses a variable number of rounds depending on the key size, with each round consisting of sub bytes, shift rows, mix columns, and add round key transformations except for the last round which excludes mix columns. The Rijndael cipher which was selected as the AES algorithm operates on a 4x4 byte state and supports key sizes of 128, 192, and 256 bits.

More Related Content

What's hot

Js2517181724

IJERA (International journal of Engineering Research and Applications) is International online, ... peer reviewed journal. For more detail or submit your article, please visit www.ijera.com

G05124550

This document presents an optimized FPGA hardware implementation of public key cryptography using encryption and decryption. The implementation uses two keys - a public key for encryption that anyone can use, and a private key for decryption that only the intended recipient possesses. The design was tested on a Xilinx Virtex 5 FPGA. Encryption and decryption were shown to work correctly when the proper keys were used. Without the private key, decryption was not possible, demonstrating the security of the approach. Synthesis results showed the design utilizes FPGA resources efficiently compared to other related work.

FPGA and ASIC Implementation of Speech Encryption and Decryption using AES Al...

FPGA and ASIC Implementation of Speech Encryption and Decryption using AES Al...IJCSIS Research Publications

With increasing technology development in field of communication and Electronic devices, there is a need for better security service for information transfer in Medical Sectors, Banking, Financial and in other IoT applications etc. Fight against security attacks is of prime importance. Through Cryptographic techniques we can provide Authenticity as well as Confidentiality for the user data. In this paper, hardware implementation has been described for a real-time application of speech data encryption and decryption using AES algorithm along with the speech recognition using cross correlation technique. Verilog programming environment is used for AES cryptography whereas MATLAB is used for Speech recognition. ASIC design on AES core is implemented using Cadence tools. Number of gates, area and power used by AES core design has been drastically reduced by specifying wide range of constraints during front end designing. In Backend designing, layout of AES design, which is the physical geometric representation is also developed.Simulated Analysis and Enhancement of Blowfish Algorithm

This paper represents or analyzes the security of system based on Blowfish. Blowfish mainly focuses

on the encrypt and decrypt techniques and algorithms apply for cryptanalysis. It describe the algorithms for

encryption as well as decryption algorithms and also give the sufficient description of key generation, key

expansion, function and working principle of Blowfish cipher with proper explanations. Taking the current era,

Most of the famous systems which offer security for a network or web or to a data are vulnerability to attacks and

they are broken at some point of time by effective cryptanalysis methods, irrespective of its complex algorithmic

design. In the general, today’s cryptography world is bounded to an interpretive of following any one or multi

encryption scheme and that too for a single iteration on a single file only. This is evident in the maximum of the

encryption-decryption cases. It also describes the comparisons between older blowfish and enhances blowfish. It

also shows enhance Blowfish algorithm for encryption and decryption of data. It is also give the proper simulated

analysis of encryption and decryption time for different file formats using a windows application. It describe

feature of application and its process and efficiency as well as calculation of time and throughput.

A VHDL Implemetation of the Advanced Encryption Standard-Rijndael.pdf

This document describes a thesis submitted by Rajender Manteena to the University of South Florida for a Master of Science in Electrical Engineering. The thesis presents a VHDL implementation of the Advanced Encryption Standard (AES) Rijndael algorithm. It includes descriptions of the encryption and decryption processes, mathematical background on finite field arithmetic, and implementation results from simulating the VHDL code on an Altera FPGA development board. The goal was to create an optimized hardware implementation of the AES algorithm using VHDL for applications such as encryption processors or smart cards.

M04302093096

International Journal of Computational Engineering Research(IJCER) is an intentional online Journal in English monthly publishing journal. This Journal publish original research work that contributes significantly to further the scientific knowledge in engineering and Technology.

A vlsi implementation of a resource efficient and secure architecture of a b...

This document discusses the VLSI implementation of a resource efficient and secure architecture for a block cipher. It proposes two designs - a throughput enhanced design and an area reduced design. The designs implement a 128-bit block cipher using the Hummingbird algorithm. Simulation results on ModelSim and synthesis results on Xilinx show that the area reduced design uses fewer logic resources than the throughput enhanced design, making it more suitable for FPGA implementation where area is a concern.

Enhanced Advanced Encryption Standard (E-AES): using ESET

This document proposes an enhanced version of the Advanced Encryption Standard (AES) called E-AES. E-AES increases the key size to 2048 bits and the block size to 1024 bits. This provides more security than AES, which uses a 128, 192, or 256 bit key on a 128 bit block. E-AES specifies 64 rounds of encryption, compared to AES which uses 10 to 14 rounds depending on key size. The encryption process of E-AES involves four transformations at each round: byte substitution using an S-box, shifting rows of the state matrix, mixing data within columns, and adding a round key. This enhanced algorithm is proposed to address known attacks on AES and the use of its 16 year old standard with

An improved geo encryption algorithm in location based services

Abstract Wireless technology is used in many applications with location based data encryption techniques to secure the communication. The use of knowledge of the mobile user's location called Geo-encryption, produces more secure systems that can be used in different mobile applications. Location Based Data Encryption Methods (LBDEM) is a technique used to enhance the security of such applications called as Location Based Services (LBS). It collects position, time, latitude coordinates and longitude coordinates of mobile nodes and uses for the encryption and decryption process. Geo-encryption plays an important role to raise the security of LBS. Different Geo-protocols have been developed in the same area to add security with better throughput. The Advanced Encryption Standard in Geo-encryption with Dynamic Tolerance Distance (AES-GEDTD) is an approach which gives higher security with a great throughput. This approach mainly uses the AES algorithm, symmetric key encryption algorithm. But applying this algorithm to more complex data like images, videos, etc. like in Digital Film Distribution, we might face the problem of computational overhead. To overcome this problem, we analyze AES and modify it, to reduce the computational overhead. In the modified AES algorithm (M-AES), we omit the calculation of mix column operations and hence the M-AES-GEDTD is a fast and lightweight algorithm for multimedia data. Keywords: Geo-encryption; LBDEM; LBS, Geo-locked Keys .

Design of A New Lightweight Encryption for Embedded Security

The document describes a proposed new lightweight encryption algorithm called PRESENT GRP for embedded security applications. It is designed to have low power consumption, small memory footprint, and provide security. The algorithm combines the substitution box of the existing PRESENT algorithm with a new group random permutation (GRP) layer, which provides confusion and can permute bits faster than a lookup table. Simulation results show PRESENT GRP requires less gate equivalents and memory than existing lightweight algorithms like PRESENT, making it suitable for constrained embedded devices.

Wireless Network Security Architecture with Blowfish Encryption Model

Abstract: In this research paper ,we developed a model for a large network, wireless nodes are interconnected and each can be considered as a node processor that offer services to other node processors connected to a specific network. A very high proportion of the nodes that offer services need to carry out an authentication process so as to make an access request to the node offering the service. In this context, an integrated reconfigurable network security architecture moved to the application layer has become the need of the day for secure wireless data sharing. The security schemes of the seven layer OSI architecture need to be placed intrinsically in the wireless node itself and should be capable of supporting the MAC layer, IP address based layer and the routing protocols of the network layer. This work focuses on the use of emulator and embedded hardware architectures for wireless network security. In this work, the individual nodes can have a unique security signature pattern maintained by respective wireless nodes using an encryption algorithm and this is made dynamic. The metrics includes latency, throughput, Scalability, Effects of data transfer operation on node processor and application data located in the processor Keywords:Wireless Network security, Embedded hardware, Reconfigurable architecture, blowfish algorithm

New Technique Using Multiple Symmetric keys for Multilevel Encryption

In a world of accelerating communications, cryptography has become an essential component of the modern

means of communication systems. The emergence of the webas a reliable medium for commerce and

communication has made cryptography an essential component. Many algorithms or ciphers are in use

nowadays. The quality of the cipher is judged byits ability to prevent an unrelated party fromknowingthe

original content of the encrypted message. The proposed “Multilevel Encryption Model” is a cryptosystem that

adopts the basic principles of cryptography. It uses five symmetric keys (multiple)

in floating point numbers, plaintext, substitution techniques and key combinations with unintelligible

sequence to produce the ciphertext. The decryption process is also designed to reproduce the plaintext

G04701051058

International Journal of Computational Engineering Research (IJCER) is dedicated to protecting personal information and will make every reasonable effort to handle collected information appropriately. All information collected, as well as related requests, will be handled as carefully and efficiently as possible in accordance with IJCER standards for integrity and objectivity.

Introducing an Encryption Algorithm based on IDEA

Introducing an Encryption Algorithm based on IDEAInternational Journal of Science and Research (IJSR)

International Data Encryption Algorithm (IDEA) is one of the encryption algorithms that is widely used for security purpose. IDEA block cipher operates with 64-bit plain text block and 64-bit cipher text block, and a 128-bit key controls it. The fundamental design of the algorithm is using three different algebraic operations: bitwise Exclusive OR, multiplication modulo, and addition modulo. Having the largest number of weak keys is one of the drawbacks of IDEA. In addition, a new attack during round six of IDEA’s operations has been detected. In this paper, we propose and describe the new design and preliminary implementation of a more secure encryption algorithm based on IDEA, and it is named DS-IDEA. Increasing the size of the key from 128 bits to 512 bits will increase the complexity of the algorithm. The algorithm’s complexity is increased by increasing the amount of diffusion (multiplicative additive block) in a single round. It is implemented to provide better security to the user’s password within the Online Password Management System (OPMS) in order to protect the user’s data within the database from hackers and other forms of unauthorized access.

Implementation of Cryptography Architecture with High Secure Core

International Journal of Modern Engineering Research (IJMER) is Peer reviewed, online Journal. It serves as an international archival forum of scholarly research related to engineering and science education.

International Journal of Modern Engineering Research (IJMER) covers all the fields of engineering and science: Electrical Engineering, Mechanical Engineering, Civil Engineering, Chemical Engineering, Computer Engineering, Agricultural Engineering, Aerospace Engineering, Thermodynamics, Structural Engineering, Control Engineering, Robotics, Mechatronics, Fluid Mechanics, Nanotechnology, Simulators, Web-based Learning, Remote Laboratories, Engineering Design Methods, Education Research, Students' Satisfaction and Motivation, Global Projects, and Assessment…. And many more.

A Survey on Various Lightweight Cryptographic Algorithms on FPGA

In today’s rapid growing technology, digital data are exchanged very frequently in seamless wireless networks. Some of the real time applications examples which are transmitted quickly are voice, video, images and text but not limited to high sensitive information like transaction of creditcard, banking and confidential security numbers/data. Thus protection of confidential data is required with high security to avoid unauthorised access to Wireless networks. This can be done by a technique called ‘Cryptograhy’ and there are two crytography techniques available (such as symmetrical & asymmetrical techniques). The focus in this paper would be on Lightweight symmetric crytography. Lightweight cryptography is used for resource-limited devices such as radio frequency identification (RFID) tags, contactless smart cards and wireless sensor network. In this paper comparative study of selected lightweight symmetric block ciphers such as AES, PRESENT, TEA and HUMMINGBIRD is presented.

Renas Rajab Asaad

Abstract

There is great research going on in the field of data security nowadays. Protecting information from disclosure and breach is of high importance to users personally and to organizations and businesses around the world, as most of information currently are sensitive electronic information transferred over the internet and stored in cloud based system. In this paper, we propose a method to increase the security of messages transferred on the internet, or information stored in the cloud. Our proposed method mainly relies on the Triple Data Encryption Standard (TDES) algorithm. TDES is intact the Data Encryption Standard repeated three times in succession to encrypt data. TDES is considered highly secure as there is no applicable method to break the code itself without knowing the key. We propose to encrypt the key using Cipher Feedback Block algorithm, before using TDES to encrypt data. Such that even when the key is disclosed, the key itself cannot decipher the ciphered text without enciphering the key with CFB. This introduces a new dimension of security to the TDES algorithm.

The method introduced in this paper increases the security of the TDES algorithm using CFB algorithm by increasing the key security, such that it is actually not possible to decipher the text without prior knowledge and agreement of key and algorithms used.

Keywords: Data Encryption Standard, Triple Data Encryption Algorithm, Cipher Feedback Block.

Efficient Fpe Algorithm For Encrypting Credit Card Numbers

This document proposes an efficient format-preserving encryption (FPE) algorithm for encrypting credit card numbers. The algorithm uses AES-128 encryption and adds two additional steps to retain the plaintext format of 16 decimal digits. Specifically, it divides the 128-bit ciphertext into blocks, performs an XOR operation between blocks, and then converts the resulting hexadecimal values to decimal digits. This allows encryption without changing the database structure or queries. The proposed algorithm is faster and requires no additional storage compared to existing FPE techniques like prefix encryption, cycle walking, or Feistel networks. It provides an efficient way to encrypt sensitive numeric fields like credit cards while preserving functionality.

New modification on feistel DES algorithm based on multi-level keys

The data encryption standard (DES) is one of the most common symmetric encryption algorithms, but it experiences many problems. For example, it uses only one function (XOR) in the encryption process, and the combination of data is finite because it occurs only twice and operates on bits. This paper presents a new modification of the DES to overcome these problems. This could be done through adding a new level of security by increasing the key space (using three keys) during the 16 rounds of the standard encryption algorithm and by replacing the predefined XOR operation with a new # operation. Our proposed algorithm uses three keys instead of one. The first key is the input key used for encrypting and decrypting operations. The second key is used for determining the number of bits, while the third key is used for determining the table numbers, which are from 0 to 255. Having evaluated the complexity of our proposed algorithm, the results show that it is the most complex compared with the well-known DES and other modified algorithms. Consequently, in our proposed algorithm, the attacker try a number of attempts 2 1173 at minimum to decrypt the message. This means that the proposed DES algorithm will increase the security level of the well-known DES.

What's hot (19)

FPGA and ASIC Implementation of Speech Encryption and Decryption using AES Al...

FPGA and ASIC Implementation of Speech Encryption and Decryption using AES Al...

Simulated Analysis and Enhancement of Blowfish Algorithm

Simulated Analysis and Enhancement of Blowfish Algorithm

A VHDL Implemetation of the Advanced Encryption Standard-Rijndael.pdf

A VHDL Implemetation of the Advanced Encryption Standard-Rijndael.pdf

A vlsi implementation of a resource efficient and secure architecture of a b...

A vlsi implementation of a resource efficient and secure architecture of a b...

Enhanced Advanced Encryption Standard (E-AES): using ESET

Enhanced Advanced Encryption Standard (E-AES): using ESET

An improved geo encryption algorithm in location based services

An improved geo encryption algorithm in location based services

Design of A New Lightweight Encryption for Embedded Security

Design of A New Lightweight Encryption for Embedded Security

Wireless Network Security Architecture with Blowfish Encryption Model

Wireless Network Security Architecture with Blowfish Encryption Model

New Technique Using Multiple Symmetric keys for Multilevel Encryption

New Technique Using Multiple Symmetric keys for Multilevel Encryption

Implementation of Cryptography Architecture with High Secure Core

Implementation of Cryptography Architecture with High Secure Core

A Survey on Various Lightweight Cryptographic Algorithms on FPGA

A Survey on Various Lightweight Cryptographic Algorithms on FPGA

Efficient Fpe Algorithm For Encrypting Credit Card Numbers

Efficient Fpe Algorithm For Encrypting Credit Card Numbers

New modification on feistel DES algorithm based on multi-level keys

New modification on feistel DES algorithm based on multi-level keys

Viewers also liked

Advanced Encryption Standard (AES) Implementaion using Java

The document describes a project report on the implementation of the AES encryption algorithm. It was submitted by two students, Sunil Kumar R and Shreekant, in partial fulfillment of the requirements for a Bachelor of Engineering degree in computer science. The project was carried out under the guidance of three faculty members at R.V. College of Engineering in Bangalore. It includes a certificate signed by the faculty confirming the students' satisfactory completion of the project.

Aes

This paper presents 16 software implementations of the Advanced Encryption Standard (AES) cipher mapped to a fine-grained many-core processor array. The implementations explore different levels of data and task parallelism. The smallest design uses 6 cores for offline key expansion and 8 cores for online expansion, while the largest uses 107 and 137 cores respectively. Compared to other software platforms, the designs achieve 3.5-15.6 times higher throughput per chip area and 8.2-18.1 times higher energy efficiency.

Aes128 bit project_report

The document discusses the Advanced Encryption Standard (AES) algorithm, which is used for encryption and involves several processes applied to a rectangular array called the state. AES uses a variable number of rounds depending on the key size, with each round consisting of sub bytes, shift rows, mix columns, and add round key transformations except for the last round which excludes mix columns. The Rijndael cipher which was selected as the AES algorithm operates on a 4x4 byte state and supports key sizes of 128, 192, and 256 bits.

Advanced Encryption Standard (AES)

This document discusses AES (Advanced Encryption Standard), a symmetric encryption algorithm. It explains the AES encryption process which involves:

1) Performing rounds of substitution, shifting rows, mixing columns and adding a round key on the plaintext

2) The number of rounds depends on the key size (10 rounds for 128-bit keys)

3) The round keys are derived from the original key through an expansion process

Introduccion a la criptografia

Este documento explica los conceptos básicos de la criptografía, incluyendo su definición, objetivos de seguridad (confidencialidad, integridad y autenticación) y los tipos de algoritmos criptográficos (simétricos como AES y asimétricos como RSA). También describe procesos como encriptación, desencriptación y firmas digitales, así como algunos algoritmos específicos como DES, 3DES, RC4, RC5, Blowfish e IDEA.

Implementation of aes and blowfish algorithm

IJRET : International Journal of Research in Engineering and Technology is an international peer reviewed, online journal published by eSAT Publishing House for the enhancement of research in various disciplines of Engineering and Technology. The aim and scope of the journal is to provide an academic medium and an important reference for the advancement and dissemination of research results that support high-level learning, teaching and research in the fields of Engineering and Technology. We bring together Scientists, Academician, Field Engineers, Scholars and Students of related fields of Engineering and Technology

AES Cryptosystem

Cryptography and Network security, describe and explain the AES cryptosystem, Explores mistakes in paper research

and Nmap tools.

Advanced Encryption Standard (AES)

This document describes a student project to implement the Advanced Encryption Standard (AES) in Verilog. AES is a symmetric block cipher that uses 128-bit blocks and 128/192/256-bit keys. The project aims to develop optimized and synthesizable Verilog code to encrypt and decrypt 128-bit data using AES. The document provides background on cryptography, AES, and its algorithm which includes key expansion, substitution, transposition, and mixing operations. It also outlines the implementation, encryption, decryption, and performance estimation aspects of the project.

AES-Advanced Encryption Standard

Advanced Encryption Standard. What is AES? Why AES? Cryptography. Working of AES. Attacks on AES. Full working description of AES.

Hardware Implementation Of QPSK Modulator for Satellite Communications

QPSK Modulator is simulated on Matlab , FPGA is designed on Xilinx ISE and Implemented on Xilinx Virtex - 4 Development kit

Introduction to VLSI Technology

This document provides an introduction to VLSI technology and MOS transistors. It discusses the history and generations of integrated circuits from SSI to VLSI. The dominant fabrication process for high performance VLSI circuits is now silicon CMOS technology. The document then describes the basic MOS transistor structure and different types of MOS transistors including nMOS, pMOS, and CMOS. It explains the working of enhancement mode and depletion mode transistors. Finally, it discusses CMOS fabrication processes like p-well and n-well and the basic structure of a p-well CMOS process.

Viewers also liked (11)

Advanced Encryption Standard (AES) Implementaion using Java

Advanced Encryption Standard (AES) Implementaion using Java

Hardware Implementation Of QPSK Modulator for Satellite Communications

Hardware Implementation Of QPSK Modulator for Satellite Communications

Similar to hardware implementation of aes encryption and decryption for low area & low power consumption

Aes 128 192_256_bits_project_report

The document describes the implementation of the Advanced Encryption Standard (AES) algorithm in Matlab. It includes:

1) An introduction to AES that describes its motivation, definitions, requirements and overall processes.

2) A high-level design section explaining the AES algorithm, its overall structure consisting of key expansion, encryption and decryption processes using operations like SubBytes, ShiftRows, MixColumns and AddRoundKey.

3) A detailed design section describing the individual operations for both encryption and decryption, including pseudo-code. It also provides illustrations of the operations.

4) Sections on key expansion and results from implementing the AES algorithm in Matlab.

An Efficient VLSI Design of AES Cryptography Based on DNA TRNG Design

This document describes an efficient VLSI design for AES cryptography using a true random number generator (TRNG) and DNA encoding. It aims to improve security and reduce area and delay compared to standard AES. The design generates random round keys using a TRNG instead of the standard key expansion process. It further encodes a partial key from the TRNG using DNA encoding to produce the full 128-bit key, strengthening security. Simulation and synthesis results show the TRNG-based AES has lower area and delay than standard AES. Combining the TRNG with DNA encoding further optimizes the design.

High throughput FPGA Implementation of Advanced Encryption Standard Algorithm

The growth of computer systems and electronic communications and transactions has meant that the need for effective security and reliability of data communication, processing and storage is more important than ever. In this context, cryptography is a high priority research area in engineering. The Advanced Encryption Standard (AES) is a symmetric-key criptographic algorithm for protecting sensitive information and is one of the most widely secure and used algorithm today. High-throughput, low power and compactness have always been topic of interest for implementing this type of algorithm. In this paper, we are interested on the development of high throughput architecture and implementation of AES algorithm, using the least amount of hardware possible. We have adopted a pipeline approach in order to reduce the critical path and achieve competitive performances in terms of throughput and efficiency. This approach is effectively tested on the AES S-Box substitution. The latter is a complex transformation and the key point to improve architecture performances. Considering the high delay and hardware required for this transformation, we proposed 7-stage pipelined S-box by using composite field in order to deal with the critical path and the occupied area resources. In addition, efficient AES key expansion architecture suitable for our proposed pipelined AES is presented. The implementation had been successfully done on Virtex-5 XC5VLX85 and Virtex-6 XC6VLX75T Field Programmable Gate Array (FPGA) devices using Xilinx ISE v14.7. Our AES design achieved a data encryption rate of 108.69 Gbps and used only 6361 slices ressource. Compared to the best previous work, this implementation improves data throughput by 5.6% and reduces the used slices to 77.69%.

CNS team 6.pptx

This document discusses the AES encryption algorithm and key generation. AES is a block cipher that operates on 128-bit blocks and is used widely to encrypt sensitive data. It was developed by NIST to replace DES after it was cracked. AES works by repeating rounds that perform substitution, shifting, mixing, and adding a round key. The number of rounds depends on the key size, being 10 for 128-bit keys, 12 for 192-bit keys, and 14 for 256-bit keys. A key schedule algorithm calculates the round keys from the initial key. The document also covers generating keys for symmetric and asymmetric encryption.

An Efficient FPGA Implementation of the Advanced Encryption Standard Algorithm

A proposed FPGA-based implementation of the Advanced Encryption Standard (AES) algorithm is presented in this paper. This implementation is compared with other works to show the efficiency. The design uses an iterative looping approach with block and key size of 128 bits, lookup table implementation of S -box. This gives low complexity architecture and easily achieves low latency as well as high throughput. Simulation results, performance results are presented and compared with previous reported designs.

IJCER (www.ijceronline.com) International Journal of computational Engineerin...

This document describes an area optimized and pipelined FPGA implementation of the AES encryption and decryption algorithm. The AES algorithm is divided into four 32-bit units that are processed sequentially with a clock. This reduces the chip size compared to previous implementations that processed the full 128-bit blocks. Pipelining is used to increase throughput. The implementation is tested on a Spartan 3 FPGA using VHDL. It aims to achieve both high throughput and reduced hardware usage compared to prior designs.

Js2517181724

The document describes the design of a custom cryptographic processor for implementing symmetric key operations. The processor is implemented on an FPGA using Verilog. It includes instruction units to perform logical operations, arithmetic operations, and finite field arithmetic needed for symmetric key algorithms like AES, Blowfish, RC5, RC6, IDEA. The processor is pipelined for high speed and includes modules for an ALU, control unit, registers, and multiplexers. Experimental results showed the processor operates at high speed with low area and delay compared to a general purpose processor.

A04660105

This document describes the implementation of the AES (Advanced Encryption Standard) algorithm using a fully pipelined design on an FPGA. It first provides background on the AES algorithm, including its key components and previous hardware implementations. It then details the proposed fully pipelined design, which implements each of AES's 10 rounds as separate pipeline stages to achieve high throughput. Key generation is also pipelined internally. Simulation results show the design achieves a throughput higher than previous reported implementations.

Analysis of symmetric key cryptographic algorithms

This document analyzes and compares several symmetric key cryptographic algorithms. It begins with an introduction about the importance of data security and encryption. Then it provides an overview of symmetric key cryptography and describes the basic process of using a shared secret key for encryption and decryption. The rest of the document summarizes and compares the most common symmetric algorithms including DES, 3DES, IDEA, AES, RC4, RC5, RC6, and Blowfish. It analyzes the key details of how each algorithm works including block size, number of rounds, and security issues. The conclusion is that symmetric key cryptography is important for data security and continues to be improved through ongoing research.

Novel Adaptive Hold Logic Circuit for the Multiplier using Add Round Key and ...

Digital multipliers are among the most critical arithmetic functional units in many applications, such as the Fourier transform, discrete cosine transforms, and digital filtering. The through put of these applications depends on multipliers, if the multipliers are too slow, the performance of entire circuits will be reduced. The negative bias temperature instability effect occurs when a PMOS transistor is under negative bias (Vgs = −Vdd), increasing the threshold voltage of a PMOS transistor and reducing the multiplier speed. Similarly, positive bias temperature instability occurs when an NMOS transistor is under positive bias. Both effects degrade the speed of the transistor and in the long term, the system may be fail due to timing violations. Therefore, it is required to design reliable high-performance multipliers. In this paper, we implement an aging aware multiplier design with a novel adaptive hold logic (AHL) circuit. The multiplier is able to provide the higher throughput through the variable latency and can adjust the adaptive hold logic (AHL) circuit to lessen performance degradation that is due to the aging effect. The proposed design can be applied to the column bypass multiplier.

Design and Implementation of Area Efficiency AES Algoritham with FPGA and ASIC,

Abstract: A public domain encryption standard is subject to continuous, vigilant, expert cryptanalysis. AES is a symmetric encryption algorithm processing data in block of 128 bits. Under the influence of a key, a 128-bit block is encrypted by transforming it in a unique way into a new block of the same size. To implement AES Rijndael algorithm on FPGA using Verilog and synthesis using Xilinx, Plain text of 128 bit data is considered for encryption using Rijndael algorithm utilizing key. This encryption method is versatile used for military applications. The same key is used for decryption to recover the original 128 bit plain text. For high speed applications, the Non LUT based implementation of AES S-box and inverse S-box is preferred. Development of physical design of AES-128 bit is done using cadence SoC encounter. Performance evaluation of the physical design with respect to area, power, and time has been done. The core consumes 10.11 mW of power for the core area of 330100.742 μm2.

Keywords: Encryption, Decryption Rijndael algorithm, FPGA implementation, Physical Design.

IRJET- Implementation of AES Algorithm in Arduino Mega2560 Board

1) The document discusses the implementation of the Advanced Encryption Standard (AES) algorithm for encryption on an Arduino Mega2560 board. AES was chosen to securely transmit sensor data collected by microcontrollers.

2) AES provides stronger encryption than older standards like DES and 3DES through its larger key sizes of 128, 192, and 256 bits and more rounds of encryption. The document implements a simple version of AES on the Arduino board.

3) Testing showed the AES code used 8824 bytes of program storage on the Arduino and encryption took 3016 microseconds while decryption took 3792 microseconds, demonstrating AES can provide security for resource-constrained devices.

Design and Implementation of Area Efficiency AES Algoritham with FPGA and ASIC

Abstract: A public domain encryption standard is subject to continuous, vigilant, expert cryptanalysis. AES is a symmetric encryption algorithm processing data in block of 128 bits. Under the influence of a key, a 128-bit block is encrypted by transforming it in a unique way into a new block of the same size. To implement AES Rijndael algorithm on FPGA using Verilog and synthesis using Xilinx, Plain text of 128 bit data is considered for encryption using Rijndael algorithm utilizing key. This encryption method is versatile used for military applications. The same key is used for decryption to recover the original 128 bit plain text. For high speed applications, the Non LUT based implementation of AES S-box and inverse S-box is preferred. Development of physical design of AES-128 bit is done using cadence SoC encounter. Performance evaluation of the physical design with respect to area, power, and time has been done. The core consumes 10.11 mW of power for the core area of 330100.742 μm2.

Comparative Analysis of Cryptographic Algorithms and Advanced Cryptographic A...

Comparative Analysis of Cryptographic Algorithms and Advanced Cryptographic A...editor1knowledgecuddle

Today is the era of Internet and networks applications. So,Information security is a challenging issue in today’s technological world. There is a demand for a stronger encryption which is very hard to crack. The role of Cryptography is most important in the field of network security. There is a broad range of cryptographic algorithms that are used for securing networks and presently continuous researches on the new cryptographic algorithms are going on for evolving more advanced techniques for secures

communication. In this study is made for the cryptography algorithms, particularly algorithms- AES, DES, RSA, Blowfishare compared and performance is evaluated. Also some enhanced algorithms are described and compared with the enhanced algorithms.

Keywords - AES, DES, BLOWFISH, Decryption, Encryption, SecurityBiomedical image transmission based on Modified feistal algorithm

This document presents a high-performance hardware implementation of a biomedical image encryption system using a modified Feistal algorithm. The encryption algorithm is based on DES with a novel key scheduling technique. The encrypted images are unintelligible but have high clarity when decrypted. The system is implemented on an FPGA and achieves an encryption rate of 35.5 Gbit/s. It uses different keys each clock cycle, making the encrypted images very difficult to break.

82 86

This document analyzes and compares the performance of various cryptography algorithms. It discusses symmetric key algorithms like DES, AES, Blowfish and IDEA as well as asymmetric algorithms like RSA and Diffie-Hellman. The performance is evaluated based on parameters like encryption/decryption time, memory usage and throughput. Experiments show that Blowfish has better performance than AES for encrypting audio files, with lower average encryption and decryption times. In conclusion, cryptography is important for network security and Blowfish performs encryption/decryption more efficiently than AES for audio files.

82 86

This document discusses and compares several cryptography algorithms. It begins by introducing symmetric key algorithms like DES, AES, and Blowfish that use the same key for encryption and decryption. It then covers asymmetric key algorithms like RSA that use a public key for encryption and private key for decryption. The document evaluates the algorithms by describing their basic workings, including key sizes, block sizes, number of rounds, and encryption/decryption processes. It aims to study these cryptography algorithms and analyze their performance characteristics.

IRJET- Hardware and Software Co-Design of AES Algorithm on the basis of NIOS ...

1. The document discusses a hardware-software co-design of the AES encryption algorithm implemented on the NIOS II soft-core processor on an FPGA.

2. It proposes using a hardware-software co-design methodology to implement AES for encryption and decryption of 128-bit blocks using 128, 192, or 256-bit keys.

3. The implementation will utilize the Quartus II software tools and NIOS II integrated development environment to program the FPGA with the AES algorithm designed around the NIOS II soft-core processor.

Aes

This document presents new software speed records for AES-128 encryption and decryption on various platforms including 8-bit AVR microcontrollers, NVIDIA GPUs, and the Cell broadband engine. The key findings are that the AVR implementation requires 124.6 and 181.3 cycles per byte for encryption and decryption respectively while using less than 2KB of code size. For the Cell, byte-sliced implementations achieve 11.7 and 14.4 cycles per byte. The fastest GPU implementation delivers throughputs of 0.17 and 0.19 cycles per byte for encryption and decryption handling multiple input streams in parallel.

Cyber forensics

1. IPSec is a set of security protocols that provide privacy and authentication for IP communications. It has two main components: Authentication Header (AH) and Encapsulating Security Payload (ESP).

2. The Internet Key Exchange (IKE) and Oakley key determination protocol are used for automatic key management to establish Security Associations between IPSec nodes.

3. The ISAKMP framework defines procedures for establishing, negotiating, modifying and deleting Security Associations, including the exchange of key generation and authentication data payloads.

Similar to hardware implementation of aes encryption and decryption for low area & low power consumption (20)

An Efficient VLSI Design of AES Cryptography Based on DNA TRNG Design

An Efficient VLSI Design of AES Cryptography Based on DNA TRNG Design

High throughput FPGA Implementation of Advanced Encryption Standard Algorithm

High throughput FPGA Implementation of Advanced Encryption Standard Algorithm

An Efficient FPGA Implementation of the Advanced Encryption Standard Algorithm

An Efficient FPGA Implementation of the Advanced Encryption Standard Algorithm

IJCER (www.ijceronline.com) International Journal of computational Engineerin...

IJCER (www.ijceronline.com) International Journal of computational Engineerin...

Analysis of symmetric key cryptographic algorithms

Analysis of symmetric key cryptographic algorithms

Novel Adaptive Hold Logic Circuit for the Multiplier using Add Round Key and ...

Novel Adaptive Hold Logic Circuit for the Multiplier using Add Round Key and ...

Design and Implementation of Area Efficiency AES Algoritham with FPGA and ASIC,

Design and Implementation of Area Efficiency AES Algoritham with FPGA and ASIC,

IRJET- Implementation of AES Algorithm in Arduino Mega2560 Board

IRJET- Implementation of AES Algorithm in Arduino Mega2560 Board

Design and Implementation of Area Efficiency AES Algoritham with FPGA and ASIC

Design and Implementation of Area Efficiency AES Algoritham with FPGA and ASIC

Comparative Analysis of Cryptographic Algorithms and Advanced Cryptographic A...

Comparative Analysis of Cryptographic Algorithms and Advanced Cryptographic A...

Biomedical image transmission based on Modified feistal algorithm

Biomedical image transmission based on Modified feistal algorithm

IRJET- Hardware and Software Co-Design of AES Algorithm on the basis of NIOS ...

IRJET- Hardware and Software Co-Design of AES Algorithm on the basis of NIOS ...

More from Kumar Goud

Ijeee 33-36-surveillance system for coal mines based on wireless sensor network

Abstract: The foremost critical task for coal mine is of keeping track of miners spread out across a large mining areas .It becomes even difficult when mine tunnels collapse. Many mines use a radio system to track miners, but when a collapse occurs, the base stations connected by a thin wire often are rendered useless. In this project to overcome the demerits of radio system we used wireless technology for tracking the miners. For this purpose a small RF transmitter module is equipped to each person entering a mine. Each transceiver placed in the mine look after the location of miners. The transceivers communicate with base stations through Zigbee module. In addition of tracking the location of miners we also include sensors such as temperature & humidity to intimate the base station & miners when some atmosphere changes occur. Mine operators are now able to monitor the real-time locations of each miner to better pinpoint their locations in the event of an emergency. Even after a full-day of use, mine operators can locate an individual miner within ten feet.

Key Words: Wireless sensor networks (WSN), ZIGBEE, and LPC2148.

Ijeee 28-32-accurate fault location estimation in transmission lines

Accurate Fault Location Estimation in Transmission Lines

B. Narsimha Reddy Dr. P. Chandra Sekar

Sr. Assistant Professor, Dept. of EEE Associate Professor, Dept. of EEE

Mahatma Gandhi Institute of Technology Mahatma Gandhi Institute of Technology

Hyderabad, TS, India Hyderabad, TS, India

babubnr@gmail.com Pcs_76@rediffmail.com