The project report discusses the design and implementation of a real-time SDRAM controller using Verilog, focusing on optimizing memory access performance by exploring various memory mapping strategies to balance latency and bandwidth under power constraints. It covers the background of memory types, the architecture of the controller, and detailed methodologies for verification and validation. The study concludes with results on power consumption and suggestions for future improvements in memory controller design.

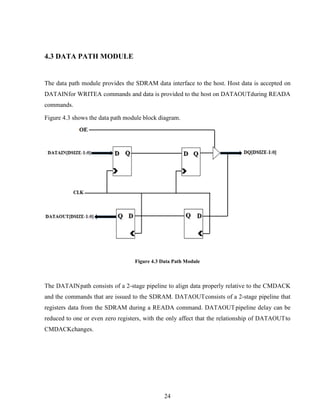

![5

Each memory cell of SRAM stores one bit of data using six transistors: a flip flop and two

access transistors (i.e. four transistors). SRAM is the faster of the two types of RAM because it

does not involve capacitors, which involve sense amplification of a small charge. For this

reason, it is used in cache memory of computers. Additionally, SRAM requires a very small

amount of power to maintain its data in standby mode Although SRAM is fast and energy

efficient it is also expensive due to the amount of silicon needed for its large cell size. This

presented the need for a denser memory cell, which brought about DRAM.

2.3 DYNAMIC RANDOM ACCESS MEMORY

According to Wakerly , “In order to build RAMs with higher density (more bits per chip), chip

designers invented memory cells that use as little as one transistor per bit. Each DRAM cell

consists of one transistor and a capacitor. Since capacitors “leak” or lose charge over time,

DRAM must have a refresh cycle to prevent data loss.

According to a high-performance DRAM study on earlier versions of DRAM, DRAM’s

refresh cycle is one reason DRAM is slower than SRAM. The cells of DRAM use sense

amplifiers to transmit data to the output buffer in the case of a read and transmit data back to the

memory cell in the case of a refresh. During a refresh cycle, the sense amplifier reads the

degraded value on a capacitor into a D- Latch and writes back the same value to the capacitor

so it is charged correctly for 1 or 0. Since all rows of memory must be refreshed and the sense

amplifier must determine the value of a, already small, degenerated capacitance, refresh

takes a significant amount of time. The refresh cycle typically occurs about every 64

milliseconds the refresh rate of the latest DRAM (DDR3) is about 1 microsecond.

Although refresh increases memory access time, according to a high-performance DRAM study

on earlier versions of DRAM, the greatest amount of time is lost during row

addressing, more specifically, “[extracting] the required data from the sense amps/row caches” .

During addressing, the memory controller first strobes the row address (RAS) onto the address

bus. Once the RAS is sent, a sense amplifier (one for each cell in the row) determines if a

charge indicating a 1 or 0 is loaded into each capacitor.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-15-320.jpg)

![13

3.2.1 Xilinx Integrated Software Environment (ISE)

We designed the arbiter using Verilog hardware description language in Xilinx Integrated

Software Environment (ISE). ISE is an environment in which the user can “take [their] design

from design entry through Xilinx device programming”. The main workbench for ISE is ISE

Project Navigator. The Project Navigator tool allows the user to effectively manage their

design and call upon development processes. In Figure 3.1, a screen shot of ISE Project

Navigator :

Figure 3.1 Screen Shot of ISE Project Navigator

Figure 3.1 shows some main windows in ISE Project Navigator. On the right hand side is the

window for code entry. The hierarchal view of modules in the design appears on the

left, and when implementation is selected from the top, the design implementation progress is

shown in the bottom window. If simulation were selected instead of implementation there

would be an option to run the design for simulation.

The main processes called upon by ISE are synthesis, implementation, and bit stream

generation. During synthesis, Xilinx Synthesis Technology (XST) is called upon. XST

synthesizes Verilog, VHDL or mixed language designs and creates netlist files. Netlist files, or

NGC files, contain the design logic and constraints.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-23-320.jpg)

![15

Implementation has a much longer turn- around time than synthesis, so while functionality in

hardware ensures the design is working, simulation is the practical choice for iterative

verification.

In order to test our design in hardware, we utilized ChipScope Pro Analyzer, a GUI which

allows the user to “configure [their] device, choose triggers, setup the console, and view results

of the capture on the fly”. In order to use ChipsScope Pro, you may either insert ChipScope

Pro Cores into the design using the Core Generator, a tool that can be accessed in ISE Project

Figure 3.2 Flow Chart and Timing for Simulation and Hardware Validation

Navigator, or utilize the Plan Ahead or Core Inserter tool, which automatically inserts cores into

the design netlist for you. One method of inserting ChipScope cores into the design is by utilizing

Plan Ahead software. The Plan Ahead tool enables the creation of floorplans.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-25-320.jpg)

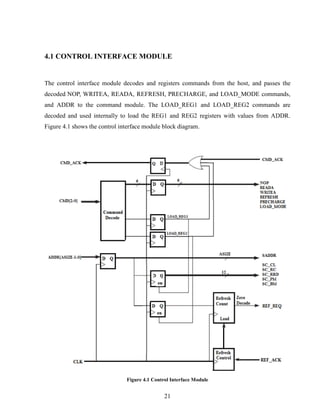

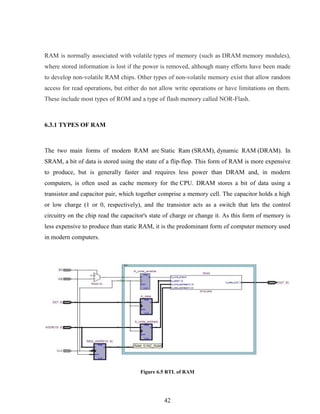

![23

Figure 4.2 Command Module Block Diagram

After the arbiter has accepted a command from the host, the command is passed onto the

command generator portion of the command module. The command module uses three shift

registers to generate the appropriate timing between the commands that are issued to the

SDRAM. One shift register is used to control the timing the ACTIVATE command; a second is

used to control the positioning of the READA or WRITEA commands; a third is used to time

command durations, which allows the arbiter to determine if the last requested operation has been

completed.

The command module also performs the multiplexing of the address to the SDRAM. The row

portion of the address is multiplexed out to the SDRAM outputs A[11:0] during the

ACTIVATE(RAS) command. The column portion is then multiplexed out to the SDRAM address

outputs during a READA (CAS) or WRITEA command.

The output signal OEis generated by the command module to control tristate buffers in the last

stage of the DATAIN path in the data path module.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-33-320.jpg)

![28

Table 5.2 Interface Signals

5.3 SDRAM CONTROLLER COMMAND INTERFACE

The SDR SDRAM Controller provides a synchronous command interface to the SDRAM and

several control registers. Table shows the commands, which are described in following sections.

The following rules apply to the commands with reference with table 5.2:

All commands, except NOP, are driven by the user ontoCMD [2:0]; ADDR and DATAIN

are set appropriately for the requested command. The controller registers the command on

the next rising clock edge.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-38-320.jpg)

![29

To acknowledge the command the controller asserts CMDACKfor one clock period.

For READA or WRITEA commands, the user should start receiving or writing data on

DATAOUTand DATAIN.

The user must drive NOP onto CMD [2:0] by the next rising clock edge after CMDACKis

asserted.

Table 5.3 Interface Commands

5.3.1 NOP Command

NOP is a no operation command to the controller. When NOP is detected by the controller, it

performs a NOP in the following clock cycle. A NOP must be issued the following clock cycle

after the controller has acknowledged a command.

The NOP command has no affect on SDRAM accesses that are already in progress.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-39-320.jpg)

![35

Figure 5.4 shows an example timing diagram of the PRECHARGE command. The following

sequence describes the general operation of a PRECHARGE command:

The user asserts PRECHARGE on CMD.

The DR SDRAM Controller asserts CMDACK to acknowledge the command and

simultaneously starts issuing commands to the SDRAM devices.

The user asserts NOP on CMD

5.3.6 LOAD_MODE Command

The LOAD_MODE command instructs the SDR SDRAM Controller to perform a LMR command

to the SDRAM. The value that is to be written into the SDRAM mode register must be present on

ADDR [11:0]with the LOAD_MODE command. The value on ADDR [11:0]is mapped directly to

the SDRAM pins A11-A0 when the SDR SDRAM Controller issues the LMR to the SDRAM.

Figure 5.5 shows an example timing diagram.

The following sequence describes the general operation of a LOAD_MODE command, the

users asserts LOAD_MODE on CMD.

The SDR SDRAM Controller asserts CMDACK to acknowledge the command and

simultaneously starts issuing commands to the SDRAM devices.

One clock after the SDR SDRAM Controller asserts CMDACK, the users asserts NOP on

CMD.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-45-320.jpg)

![62

REFERENCES

[1] C. van Berkel, “Multi-core for Mobile Phones,” in Proc. DATE, 2009.

[2] “International Technology Roadmap for Semiconductors (ITRS),” 2009.

[3] P. Kollig et al., “Heterogeneous Multi-Core Platform for Consumer Multimedia

Applications,” in Proc. DATE, 2009.

[4] L. Steffens et al., “Real-Time Analysis for Memory Access in Media Processing SoCs : A

Practical Approach,” Proc. ECRTS, 2008.

[5] S. Bayliss et al., “Methodology for designing statically scheduled application-specific

SDRAM controllers using constrained local search, “in Proc. FPT, 2009.

[6] B. Akesson et al., “Architectures and modelling of predictable memory controllers for

improved system integration,” in Proc. DATE, 2011.

[7] J. Reineke et al., “PRET DRAM Controller: Bank Privatization for Predictability and

Temporal Isolation,” in Proc. CODES+ISSS, 2011.

[8] M. Paolieri et al., “An Analyzable Memory Controller for Hard Real-Time CMPs,”

Embedded Systems Letters, IEEE, vol. 1, no. 4, 2009.

[9] Micron Technology Inc., “DDR3-800-1Gb SDRAM Datasheet, 02/10 EN edition,” 2006.

[10] D. Stiliadis et al., “Latency-rate servers: a general model for analysis of traffic scheduling

algorithms,” IEEE/ACM Trans. Netw., 1998. [11] B. Akesson et al., “Classification and Analysis

of Predictable Memory Patterns,” in Proc.RTCSA, 2010.

[12] DDR2 SDRAM Specification, JESD79-2E ed., JEDEC Solid State Technology

Association, 2008.

[13] DDR3 SDRAM Specification, JESD79-3D ed., JEDEC Solid State Technology

Association, 2009.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-72-320.jpg)

![63

[14] K. Chandrasekar et al., “Improved Power Modelling of DDR SDRAMs,” in Proc. DSD,

2011.

[15] B. Akesson et al., “Automatic Generation of Efficient Predictable Memory Patterns,” in

Proc. RTCSA, 2011.](https://image.slidesharecdn.com/memorymapselectionofrealtimesdramcontrollerusingverilogfullprojectreport-140608155243-phpapp02/85/Memory-map-selection-of-real-time-sdram-controller-using-verilog-full-project-report-73-320.jpg)