This document summarizes the design of AMD's "Zen 3" x86-64 microprocessor core. Some key points:

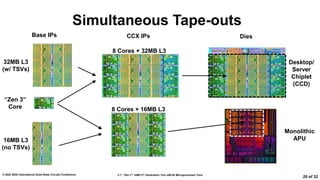

- "Zen 3" is AMD's second generation 7nm CPU core, designed to deliver higher performance than "Zen 2" through a 19% increase in instructions per clock (IPC) enabled by architectural changes and maintaining the same TSMC 7nm process.

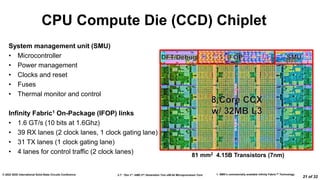

- Changes from "Zen 2" include larger caches, increased instruction issue widths, faster floating point units, and higher load/store bandwidth. These changes aim to improve performance across desktop, mobile, and server segments.

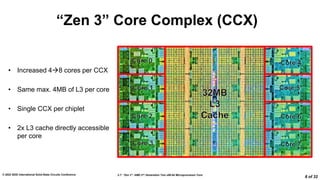

- The core complex now includes 8 cores sharing 32MB of L3 cache, compared to 4 cores

![2.7: “Zen 3”: AMD 2nd Generation 7nm x86-64 Microprocessor Core

© 2022 IEEE International Solid-State Circuits Conference

5 of 32

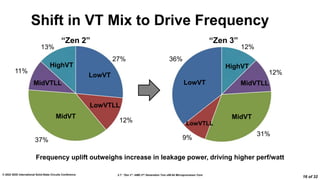

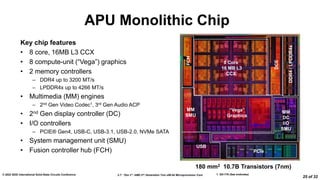

“Zen 3” Design Goals

• “Zen 3” first “ground-up” re-design of AMD “Zen” family of CPUs

• Goal: deliver performance uplift over “Zen 2”

– Driven primarily by IPC uplift via new microarchitecture

• Same TSMC 7nm FinFET technology as “Zen 2”

– Additional design effort to push frequency in same process

• Achieved +19%1 IPC (ave.), up to +6% frequency, up to +20%2 perf/watt

1. R5K-003, 2. R5K-007 (See endnotes)

AMD chiplet strategy [Naffziger, ISSCC 2020] allows for independent

optimization of CPU and non-CPU IP in product deployment](https://image.slidesharecdn.com/isscc2022paper2-220418201501/85/Zen-3-AMD-2nd-Generation-7nm-x86-64-Microprocessor-Core-5-320.jpg)

![2.7: “Zen 3”: AMD 2nd Generation 7nm x86-64 Microprocessor Core

© 2022 IEEE International Solid-State Circuits Conference

6 of 32

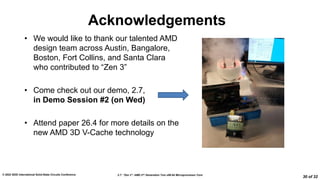

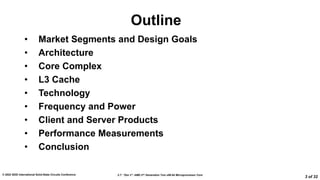

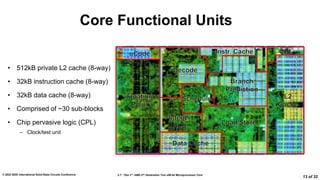

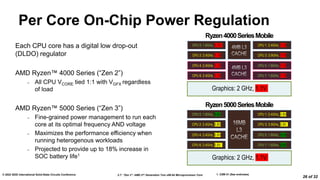

“Zen 3” Architecture

32K I-Cache (8-way)

Decode

Branch Prediction

Op-Cache

Op Queue

Dispatch

Integer Rename

Scheduler Scheduler Scheduler Scheduler Scheduler Scheduler

Floating Point Rename

ALU

BR

AGU ALU

AGU

ST

ALU

ST

AGU ALU BR

F2I

ST

MUL

MAC

ADD

MUL

MAC

ADD

F2I

ST

32K D-Cache (8-way) 512K L2 (I+D) Cache (8-way)

Load/Store Queues

Integer Register File Floating Point Register File

6 Macro Ops/Cycle Dispatched

4 Instructions/Cycle 8 Macro Ops/Cycle

3 Loads/Cycle

2 Stores/Cycle

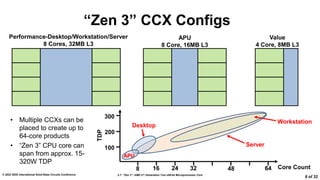

Major changes from “Zen 2”

• L1 BTB: 5121024 entries

• Improved branch pred. bandwidth

• Int issue width: 710

• Reorder buffer: 224256 entries

• FP issue width: 46

• FMAC latency: 54 cycles

• LD/ST bandwidth: 2/13/2

• TLB table walkers: 46

[Evers, Hot Chips 2021]](https://image.slidesharecdn.com/isscc2022paper2-220418201501/85/Zen-3-AMD-2nd-Generation-7nm-x86-64-Microprocessor-Core-6-320.jpg)

![2.7: “Zen 3”: AMD 2nd Generation 7nm x86-64 Microprocessor Core

© 2022 IEEE International Solid-State Circuits Conference

27 of 32

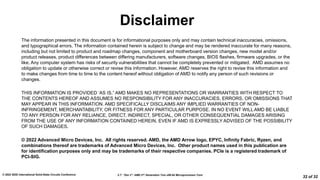

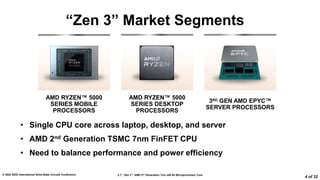

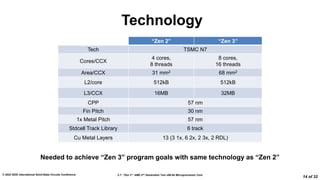

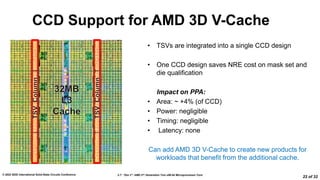

Server Performance

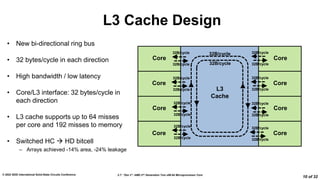

Benchmark Config “Zen 2” “Zen 3” Uplift

SPECint®2017

64 Cores [7763 vs. 7H12]1 717 854 +19%

32 Cores [75F3 vs. 7532]2 444 596 +34%

SPECfp®2017

64 Cores [7763 vs. 7H12]3 543 651 +20%

32 Cores [75F3 vs. 7532]2 434 546 +26%

SPECjbb®2017 64 Cores[7763 vs. 7H12]4 249k 314k +26%

1. MLN-088B, 2. MLN-120A, 3. MLN-086B, 4. MLN-092B, 5. MLN-061A (See endnotes)

0

100

200

300

400

500

600

700

800

900

2018 2019 2020 2021

SPECint®2017_int_base

Score

SPECint®2017 Improvement by Year 1,5

“Zen” “Zen 2” “Zen 2”

“Zen 3”

7601

(32 Cores)

7742

(64 Cores)

7H12

(64 Cores)

7763

(64 Cores)

282

701 717

854](https://image.slidesharecdn.com/isscc2022paper2-220418201501/85/Zen-3-AMD-2nd-Generation-7nm-x86-64-Microprocessor-Core-27-320.jpg)

![2.7: “Zen 3”: AMD 2nd Generation 7nm x86-64 Microprocessor Core

© 2022 IEEE International Solid-State Circuits Conference

28 of 32

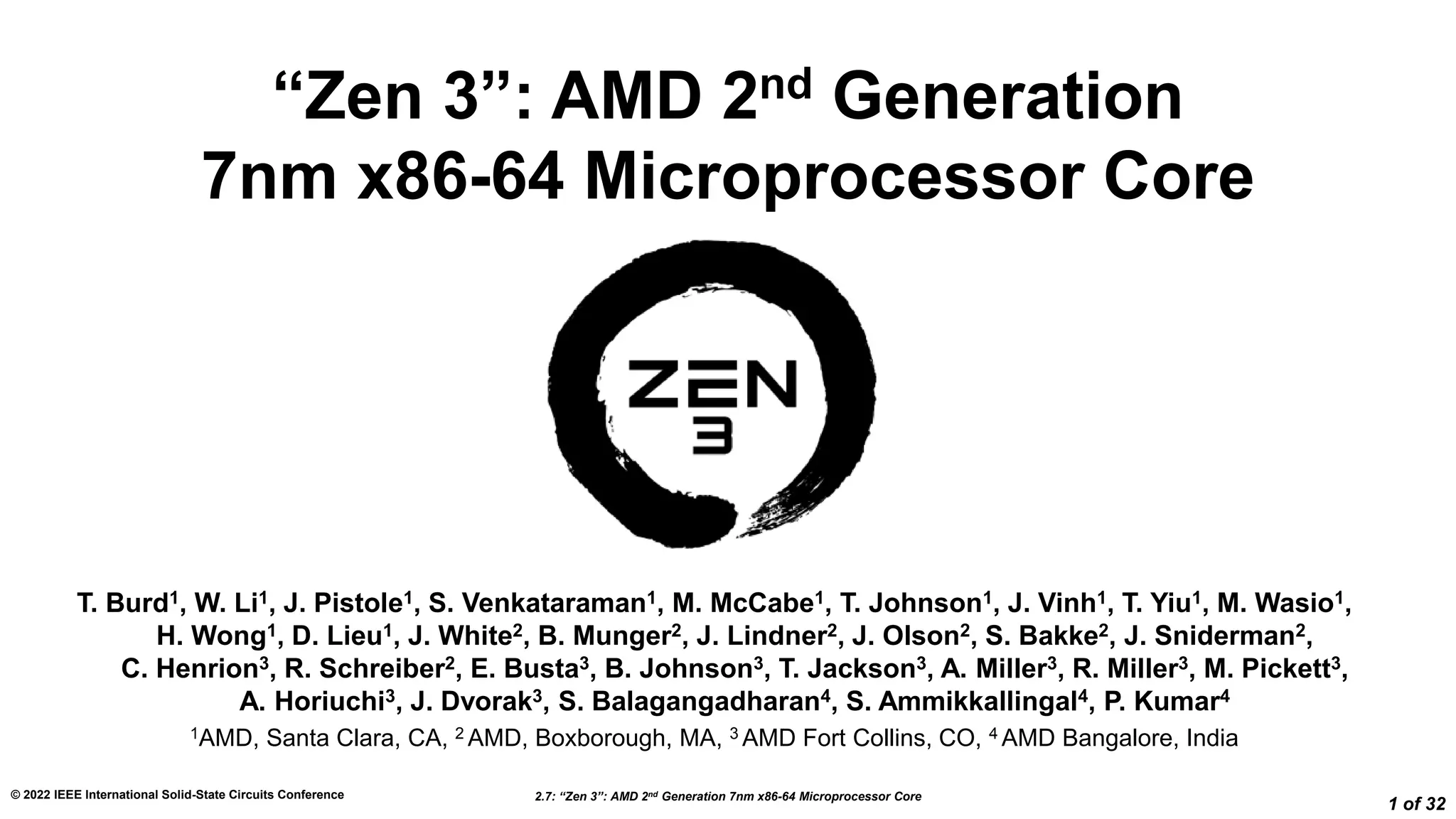

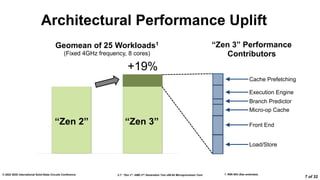

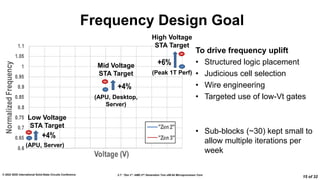

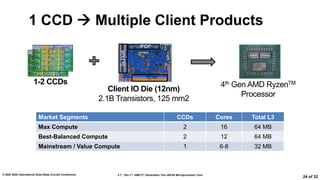

Client Performance

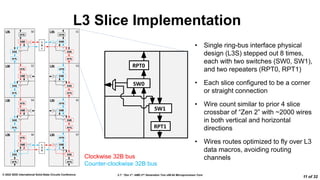

Benchmark Segment “Zen 2” “Zen 3” Uplift

Cinebench R20

Desktop [5950X vs. 3900XT]1,5 546 (4.7 GHz) 640 (4.9 GHz) +17%

Mobile [5800U vs. 5600U]2 474 (4.4Ghz) 551 (4.6 GHz) +16%

Benchmark Config “Zen 2” “Zen 3” Uplift

Cinebench R20 8 Cores [5800U vs. 4800U]2 3218 3655 +14%

PCMark 10 8 Cores [5800U vs. 4800U]3 5081 6074 +20%

PCMark Apps 8 Cores [5800U vs. 4800U]3 8663 10663 +23%

Single-

Thread

Multi-

Thread

1. R5K-004, 2. CZM-48, 3. CZM-38, 4. R5K-009, 5. R5K-025 (See endnotes)

Benchmark Game Config Uplift

CS:GOTM (DirectX® 9)

12 Cores

[3900XT

vs.

5900X]4

+46%

PUBGTM (DirectX® 11) +33%

DOTATM (Vulkan®) +24%

F1TM 2019 (DirectX® 12) +24%

BattlefieldTM V (DirectX® 12) +5%

Benchmark Game Config Uplift

League of LegendsTM (DirectX® 11)

12 Cores

[3900XT

vs.

5900X]4

+50%

Shadow of the Tomb RaiderTM (DirectX® 12) +28%

Far CryTM New Dawn (DirectX® 11) +22%

Ashes of the SingularityTM (Vulkan®) +19%

Total WarTM : Three Kingdoms (DirectX® 11) +6%

Major Gaming Uplifts with “Zen 3”: +26% on average](https://image.slidesharecdn.com/isscc2022paper2-220418201501/85/Zen-3-AMD-2nd-Generation-7nm-x86-64-Microprocessor-Core-28-320.jpg)