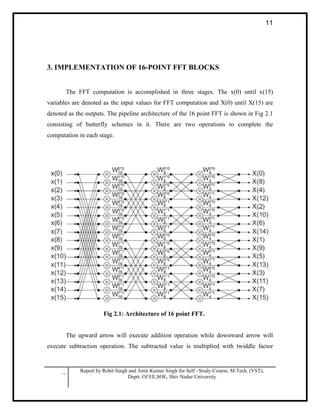

This document presents an implementation of the Fast Fourier Transform (FFT) algorithm. It begins with an introduction to FFTs, explaining that they can compute the Discrete Fourier Transform (DFT) much more efficiently than direct evaluation, reducing the computation time from O(N^2) to O(N log N). It then describes the basic butterfly structures used in FFTs and shows how to implement 16-point FFT blocks. The document includes MATLAB code for an 8-point DFT and FFT, as well as VHDL code for a 16-point FFT processor. It provides details on decimation-in-time and decimation-in-frequency algorithms and how they recursively break down the DFT into smaller transforms

![.. Report by Rohit Singh and Amit Kumar Singh for Self –Study-Course, M.Tech. (VST),

Deptt. Of EE,SOE, Shiv Nadar University

6

One can factor a common multiplier out of the second sum in the

equation. It is the two sums are the DFT of the even-indexed part x2m and the DFT of

odd-indexed part x2m + 1 of the function xn. Denote the DFT of the Even-indexed inputs

x2m by Ek and the DFT of the Odd-indexed inputs x2m + 1 by Ok and we obtain:

However, these smaller DFTs have a length of N/2, so we need compute only N/2

outputs: thanks to the periodicity properties of the DFT, the outputs for N/2 < k < N from

a DFT of length N/2 are identical to the outputs for 0< k < N/2. That is, Ek + N / 2 = Ek

and Ok + N / 2 = Ok. The phase factor exp[ − 2πik / N] called a twiddle factor which

obeys the relation: exp[ − 2πi(k + N / 2) / N] = e − πiexp[ − 2πik / N] = − exp[ − 2πik / N],

flipping the sign of the Ok + N / 2 terms. Thus, the whole DFT can be calculated as

follows:

This result, expressing the DFT of length N recursively in terms of two DFTs of

size N/2, is the core of the radix-2 DIT fast Fourier transform. The algorithm gains its

speed by re-using the results of intermediate computations to compute multiple DFT

outputs. Note that final outputs are obtained by a +/− combination of Ek and Okexp( −

2πik / N), which is simply a size-2 DFT; when this is generalized to larger radices below,

the size-2 DFT is replaced by a larger DFT (which itself can be evaluated with an FFT).](https://image.slidesharecdn.com/fftprocessor-140531030707-phpapp01/85/Design-of-FFT-Processor-6-320.jpg)

![.. Report by Rohit Singh and Amit Kumar Singh for Self –Study-Course, M.Tech. (VST),

Deptt. Of EE,SOE, Shiv Nadar University

13

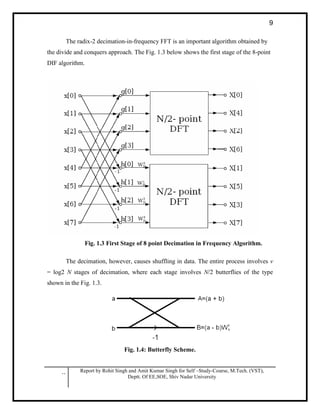

5. Matlab Code for 8 point FFT

% program to calculate 8 point FFT

clear all;

clc;

x=input (' enter the sequence of length 8 ');

tic

s0=zeros(1,8);

s1=zeros(1,8);

s2=zeros(1,8);

s3=zeros(1,8);

N=size(x,2);

if (N < 8 || N > 8)

disp(' sequence is of not proper length ');

else

stage1=[1 1 1 0-1j 1 1 1 0-1j];

stage2=[1 1 1 1 1 0.707-0.707j 0-1j -0.707-0.707j];

p=[0:7]';

t=bitrevorder(p);

% calculation of stage zero

for i=1:N

s0(i)=x(t(i)+1);

end

% calculation of stage one

for i=1:2:N

s1(i)=s0(i)+s0(i+1);

s1(i+1)=s0(i)-s0(i+1);

end

for a=1:N

s1(a)=s1(a)*stage1(a);

end

% calculation of stage two

for i=1:4:N

s2(i)=s1(i)+s1(i+2);

s2(i+1)=s1(i+1)+s1(i+3);

s2(i+2)=s1(i)-s1(i+2);

s2(i+3)=s1(i+1)-s1(i+3);

end

for a=1:N

s2(a)=s2(a)*stage2(a);

end

% calculation of stage three

s3(1)=s2(1)+s2(5);

s3(2)=s2(2)+s2(6);

s3(3)=s2(3)+s2(7);

s3(4)=s2(4)+s2(8);

s3(5)=s2(1)-s2(5);

s3(6)=s2(2)-s2(6);

s3(7)=s2(3)-s2(7);

s3(8)=s2(4)-s2(8);

end

disp(' FFT result ');

s3

toc](https://image.slidesharecdn.com/fftprocessor-140531030707-phpapp01/85/Design-of-FFT-Processor-13-320.jpg)